# InnoMux2-EP Family

Off-Line Zero Voltage Switching (ZVS) Flyback Switcher IC for Multi-Output Applications

### **Product Highlights**

### **Highly Integrated, Compact Footprint**

- Up to 3 independently regulated outputs using a single controller and transformer

- · Eliminates post regulators

- Incorporates a multi-mode Quasi-Resonant Discontinuous Conduction Mode (DCM) and Continuous Conduction Mode (CCM) flyback controller, 650 V, 725 V, 750 V or 1700 V power switch, secondary-side control and synchronous rectification driver

- Integrated FluxLink<sup>™</sup> feedback link eliminates optocouplers

- Zero voltage switching (ZVS) using advanced SR FET control with DCM only mode

- Excellent transient response: <±5% CV with 100% load step

- Outputs up to 200 V for CV and CC (LED drive) configurations

### **EcoSmart™ - Energy Efficient**

- PowiGaN<sup>™</sup> technology enables >90% efficient power supplies

- Designs easily meet global energy efficiency regulations

- Proprietary switching algorithm ensures high efficiency across load

- Low dissipation allows PCB cooling no heat sinks required

### **Advanced Protection / Safety Features**

- Primary sensed output OVP

- · Open SR-FET gate detection

- · Hysteretic thermal shutdown

- Input voltage monitor with accurate brown-in/brown-out and overvoltage protection

- Overload protection for each output

- LED short / open protection

### Full Safety and Regulatory Compliance7

- · Reinforced isolation

- Isolation voltage >4000 VAC

- 100% production HIPOT tested

- UL1577 isolation voltage 4000 VAC (max), TUV (EN62368-1), CQC (GB4943.1) and DIN EN IEC 60747-17 (VDE 0884-17) See Note 7

- Enables designs required to meet class A performance criteria for EN61000-4 suite of test standards, including EN61000-4-2, 4-3 (30 V/m), 4-4, 4-5, 4-6, 4-8 (100 A/m) and 4-9 (1000 A/m)

### **Green Package**

Halogen free and RoHS compliant

### **Applications**

- High efficiency driver for monitors and TVs

- Ideal for designs that need to meet Energy Star 8, CEC, and 2021/2023 EU labeling requirements

- High efficiency multi-output power supplies for industrial, smartmeter and appliance applications

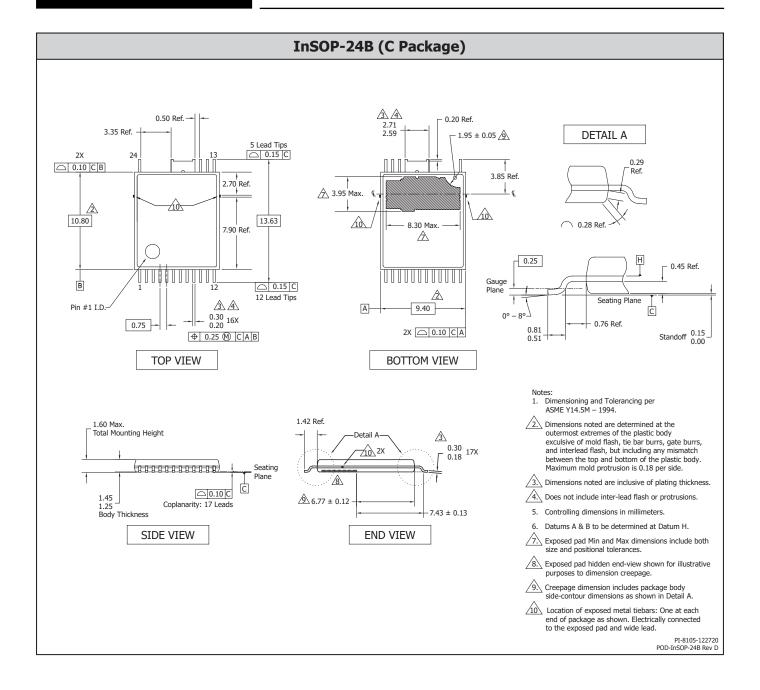

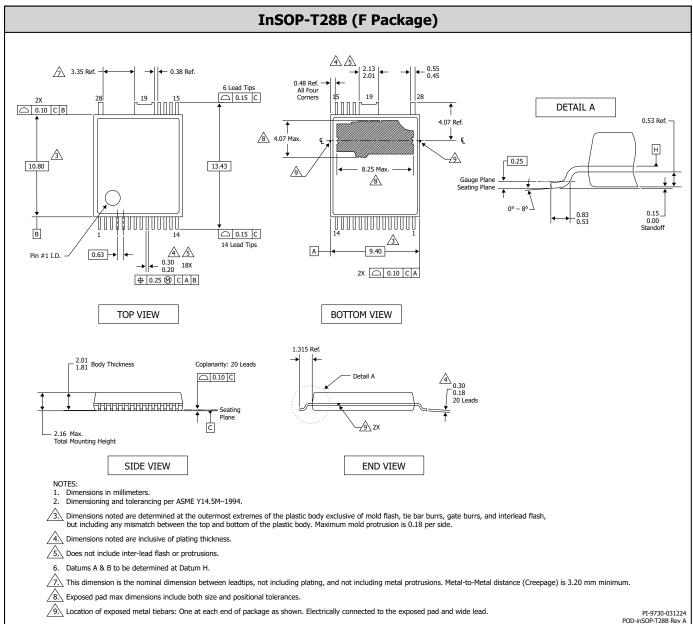

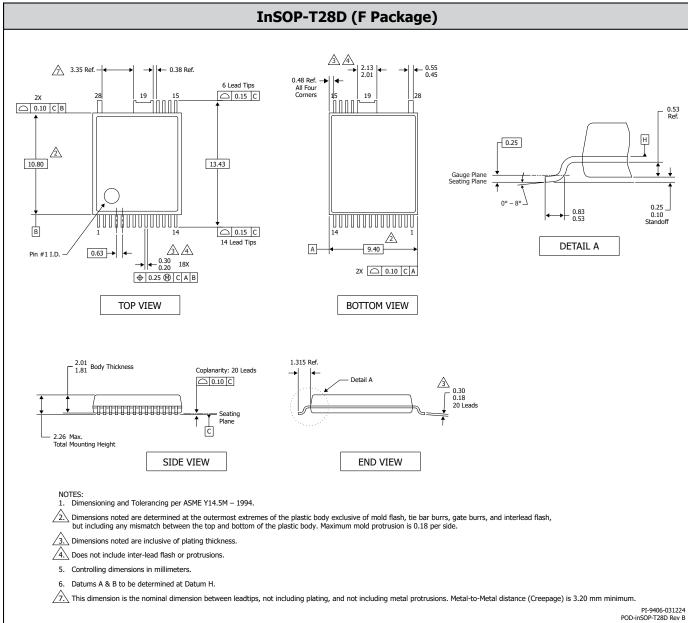

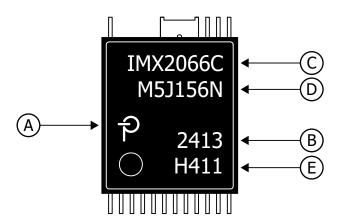

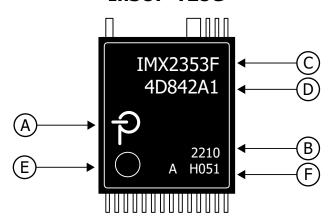

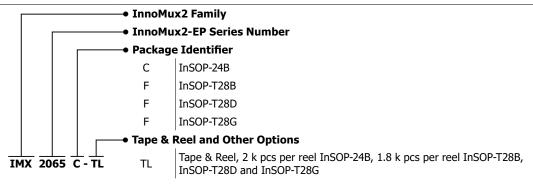

Figure 5. Left - InnoMux2-EP in InSOP-24B Package. Middle - InnoMux2-EP in InSOP-T28D/B Package. Right - InnoMux2-EP in InSOP-T28G Package.

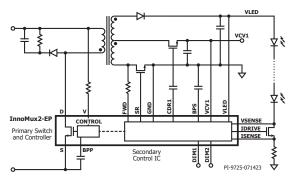

Figure 1. Typical Application with LED Driver. (IMX2353F (1700 V) does not support LED Driver)

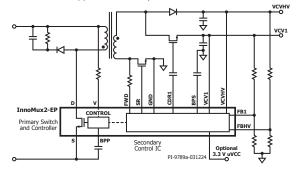

Figure 2. Typical Application with Two Constant Voltages.

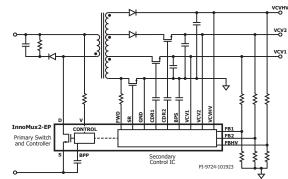

Figure 3. Typical Application with Three Constant Voltages.

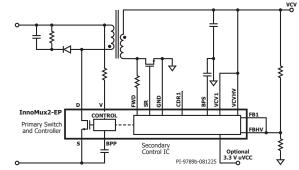

Figure 4. Typical Application with One Output.

www.power.com August 2025

| Output Power 1        | <b>Table</b>                    |                         |         |                                   |  |  |  |  |

|-----------------------|---------------------------------|-------------------------|---------|-----------------------------------|--|--|--|--|

| D d                   | 1 CV & 1 CC Output <sup>6</sup> |                         |         |                                   |  |  |  |  |

| Product               | 230 VAC ±15% <sup>1</sup>       | 85-265 VAC <sup>1</sup> |         | 385 VDC (PFC Input)               |  |  |  |  |

| 650 V MOSFET          |                                 |                         |         |                                   |  |  |  |  |

| IMX2267C <sup>2</sup> | 40 W                            | 36                      | W       |                                   |  |  |  |  |

| IMX2268C <sup>2</sup> | 55 W                            | 50                      | W       |                                   |  |  |  |  |

| 750 V PowiGaN         |                                 | Up to 3 CV              | Outputs | 6                                 |  |  |  |  |

| IMX2278F⁴             | 77 W                            | 60                      | W       | 85 W                              |  |  |  |  |

| IMX2279F⁴             | 88 W                            | 88 W 70 W               |         | 97 W                              |  |  |  |  |

| IMX2270F⁴             | 100 W                           | 80                      | W       | 110 W                             |  |  |  |  |

| 725 V MOSFET          |                                 |                         |         |                                   |  |  |  |  |

| IMX2174F <sup>3</sup> | 20 W                            | 15                      | W       |                                   |  |  |  |  |

| IMX2175F <sup>3</sup> | 25 W                            | 20                      | W       |                                   |  |  |  |  |

| IMX2176F <sup>3</sup> | 35 W                            | 27                      | W       |                                   |  |  |  |  |

| IMX2177F <sup>3</sup> | 40 W                            | 36                      | W       |                                   |  |  |  |  |

| 750 V PowiGaN         |                                 |                         |         |                                   |  |  |  |  |

| IMX2378F <sup>3</sup> | 70 W                            | 55                      | W       | 77 W                              |  |  |  |  |

| IMX2379F <sup>3</sup> | 80 W                            | 65                      | W       | 88 W                              |  |  |  |  |

| IMX2370F <sup>3</sup> | 90 W                            | 75                      | W       | 100 W                             |  |  |  |  |

| 1700 V PowiGaN        |                                 |                         |         |                                   |  |  |  |  |

|                       | 85-670 VAC<br>Peak or Open Fra  | nme¹                    | Pe      | 300-1000 VDC<br>ak or Open Frame¹ |  |  |  |  |

|                       |                                 |                         |         |                                   |  |  |  |  |

100 W

55 W

IMX2353F⁵

- Table 1. InnoMux2-EP Controller Part Numbers.

Continuous power using nominal primary current limit in a typical open frame application at +50 °C ambient with adequate PCB thermal design to ensure package temperature <125 °C.</li>

InSOP-24B (C) exposed pad.

InSOP-T28D (F).

InSOP-T28B (F) exposed pad.

InSOP-T28G (F).

Use Feature Code table on page 39 when selecting parts with 1 or 2 CV outputs. Parts with no feature code are configured to support 3 CV output designs.

Contact PI for Information on UL, TUV, CQC and DIN EN IEC 60747-17.

### **Description**

The InnoMux™2-EP IC dramatically improves power conversion efficiency. By independently regulating and protecting each output the InnoMux2-EP family eliminates multiple downstream conversion stages. InnoMux2-EP IC-based designs have low BOM count and small size. The family incorporates both primary and secondary-side controllers, with protection, sense elements and a safety-rated

feedback mechanism (FluxLink) into a single IC. The InnoMux2-EP IC also includes an LED backlight controller that supports multi-mode dimming making it ideal for monitors, TVs and appliances with lighting or display requirements.

The InnoMux2-EP IC contains enhanced features for maximizing conversion efficiency including quasi-resonant switching in DCM operation, accurate SR control and minimum-threshold-regulation for the LED driver.

### **Configuration Options**

|          |                  | _                   |                            |                   |                  | _                                        |                                            |                     |                                       |            |

|----------|------------------|---------------------|----------------------------|-------------------|------------------|------------------------------------------|--------------------------------------------|---------------------|---------------------------------------|------------|

| Part No. | Switch<br>Rating | Continuous<br>Power | Peak<br>Power <sup>1</sup> | Output            | CV1 <sup>2</sup> | Maximum<br>V <sub>LED</sub> <sup>2</sup> | V <sub>SENSE</sub><br>Voltage <sup>2</sup> | SR MOSFET<br>Driver | Dimming<br>Interface <sup>2</sup>     | Package    |

| IMX2267C | 650 V            | 36 W¹               | 57 W                       | 1 CV, 1 CC        | 12 V             | 80 V                                     | 0.8 V                                      | No                  | 2-Pin Filtered PWM/<br>Hybrid Dimming | InSOP-24B  |

| IMX2268C | 650 V            | 50 W¹               | 80 W                       | 1 CV, 1 CC        | 12 V             | 80 V                                     | 0.8 V                                      | No                  | 2-Pin Filtered PWM/<br>Hybrid Dimming | InSOP-24B  |

| IMX2278F | 750 V            | 60 W¹               | 94 W                       | 1 CV, 1 CC        | 12 V             | 140 V                                    | 0.9 V                                      | Yes                 | 2-Pin Filtered PWM/<br>Hybrid Dimming | InSOP-T28B |

| IMX2279F | 750 V            | 70 W¹               | 110 W                      | 1 CV, 1 CC        | 12 V             | 150 V                                    | 1.0 V                                      | Yes                 | 2-Pin Filtered PWM/<br>Hybrid Dimming | InSOP-T28B |

| IMX2270F | 750 V            | 80 W¹               | 130 W                      | 1 CV, 1 CC        | 12 V             | 170 V                                    | 1.0 V                                      | Yes                 | 2-Pin Filtered PWM/<br>Hybrid Dimming | InSOP-T28B |

| IMX2174F | 725 V            | 15 W¹               |                            | 2 CV³             |                  |                                          |                                            | Yes                 |                                       | InSOP-T28D |

| IMX2175F | 725 V            | 22 W¹               |                            | 2 CV³             |                  |                                          |                                            | Yes                 |                                       | InSOP-T28D |

| IMX2176F | 725 V            | 27 W¹               |                            | 2 CV³             |                  |                                          |                                            | Yes                 |                                       | InSOP-T28D |

| IMX2177F | 725 V            | 36 W¹               |                            | 2 CV <sup>3</sup> |                  |                                          |                                            | Yes                 |                                       | InSOP-T28D |

| IMX2378F | 750 V            | 55 W¹               |                            | 3 CV <sup>4</sup> |                  |                                          |                                            | Yes                 |                                       | InSOP-T28D |

| IMX2379F | 750 V            | 65 W¹               |                            | 3 CV⁴             |                  |                                          |                                            | Yes                 |                                       | InSOP-T28D |

| IMX2370F | 750 V            | 75 W¹               |                            | 3 CV <sup>4</sup> |                  |                                          |                                            | Yes                 |                                       | InSOP-T28D |

| IMX2353F | 1700 V           | 100 W <sup>5</sup>  |                            | 3 CV <sup>6</sup> |                  |                                          |                                            | Yes                 |                                       | InSOP-T28G |

Table 2. Configuration Options.

- 1. 85 265 VAC.

- 2. These parameters can be configured to other values.

- 3. Can be configured to 3 CV.

- 4. Can be configured to 2 CV.

- 5. 300 1000 VDC.

- 6. Also available on 2 CV. See Feature Code Table.

### **Block Diagrams**

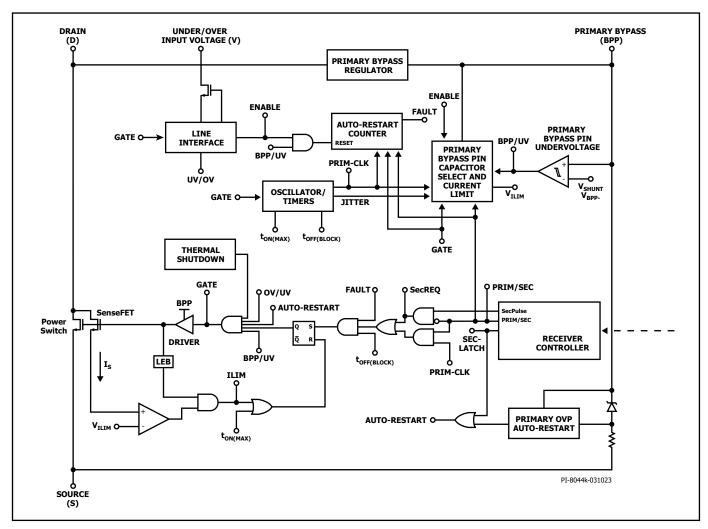

Figure 6. InnoMux2-EP Primary Block Diagram.

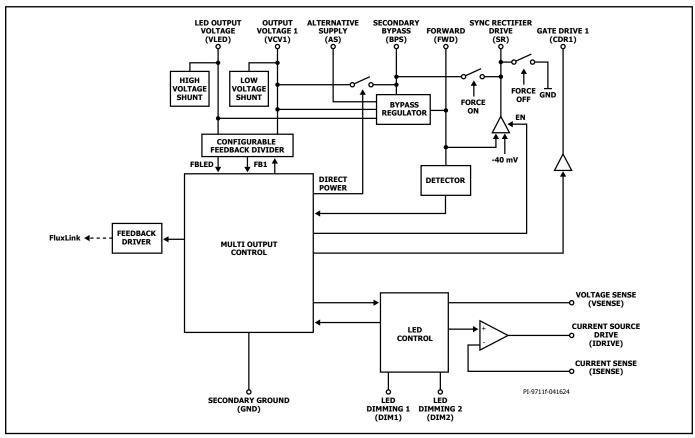

Figure 7. InnoMux2-EP Secondary Block Diagram LED Configuration. (Not applicable for IMX2353F)

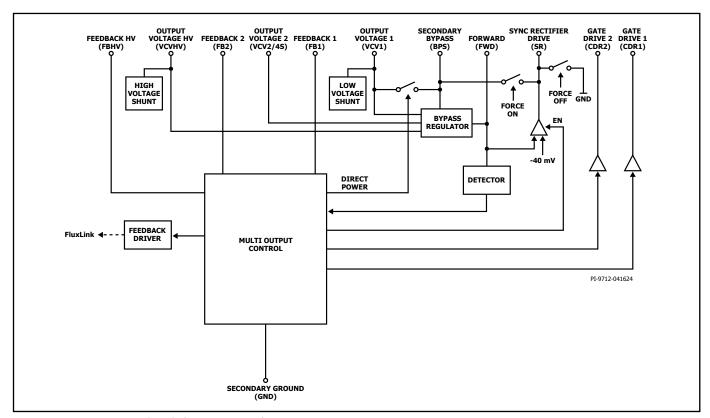

Figure 8. InnoMux2-EP Secondary Block Diagram CV Configuration.

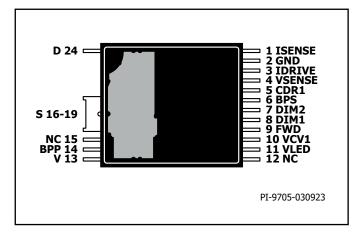

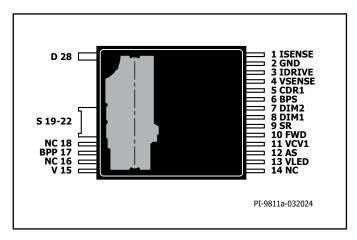

### Pin Functional Description IMX226xC

# InnoMux2-EP InSOP-24B 1CV+1LED Dual Dimming Pin Configuration

### **CURRENT SENSE (ISENSE) Pin (Pin 1)**

Connection to external LED driver MOSFET source terminal for sensing LED current. An external current sense resistor should be connected between this and the GND pin.

### **SECONDARY GROUND (GND) Pin (Pin 2)**

GND for the secondary IC.

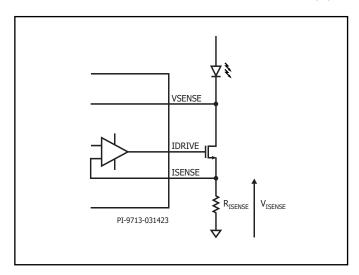

### **CURRENT SOURCE DRIVE (IDRIVE) Pin (Pin 3)**

Connection to external LED driver MOSFET gate terminal for controlling LED current.

### **VOLTAGE SENSE (VSENSE) Pin (Pin 4)**

Connection to external LED driver MOSFET Drain terminal for regulation of voltage to minimise MOSFET power dissipation.

### GATE DRIVE 1 (CDR1) Pin (Pin 5)

Gate driver for external selection MOSFET for the  $V_{\text{CVI}}$  output.

### **SECONDARY BYPASS (BPS) Pin (Pin 6)**

Connection for external bypass capacitor which supplies power to the secondary side of the IC.

### LED DIMMING 2 (DIM2) Pin (Pin 7)

LED dimming control input.

### LED DIMMING 1 (DIM1) Pin (Pin 8)

LED dimming control input.

### FORWARD (FWD) Pin (Pin 9)

The connection point to the switching node of the transformer output winding providing information on primary switch timing. Provides power for the secondary-side controller during start-up.

### **OUTPUT VOLTAGE 1 (VCV1) Pin (Pin 10)**

Connected directly to the  $V_{\rm cv1}$  output voltage, to provide current for the controller on the secondary-side and provide sensing for output voltage regulation and protection.

### **LED OUTPUT VOLTAGE (VLED) Pin (Pin 11)**

Connected directly to the LED output voltage, to provide current for the controller on the secondary-side and provide sensing of LED voltage for overvoltage protection.

Figure 9. InnoMux2-EP InSOP-24B 1CV+1LED Dual Dimming Pin Configuration (Bottom View).

### NC Pin (Pin 12)

Leave open. Should not be connected to any other pins.

### **UNDER/OVER INPUT VOLTAGE (V) Pin (Pin 13)**

A high-voltage pin connected to the AC or DC side of the input bridge for detecting undervoltage and overvoltage conditions at the power supply input. This pin should be tied to the SOURCE pin to disable UV/OV protection.

### PRIMARY BYPASS (BPP) (Pin 14)

The connection point for an external bypass capacitor of the primary-side supply. This is also the  $I_{\text{LIM}}$  selection pin for choosing standard  $I_{_{1\,\text{IM}}}$  or  $I_{_{1\,\text{IM}+1}}.$

### NC Pin (Pin 15)

Leave open or connect to the SOURCE pin or BPP pin.

### SOURCE (S) Pin (Pin 16-19)

These pins are the power switch SOURCE connection. Also ground reference for the primary BYPASS pin.

### DRAIN (D) Pin (Pin 24)

Power switch Drain connection.

### SOURCE (S) Exposed Pad (InSOP-24B Only)

Power switch SOURCE connection. Also ground reference for the primary BYPASS pin. Connect all SOURCE pins together. Used to enhance thermal management.

# InnoMux2-EP InSOP-T28B 1CV+1LED Dual Dimming with SR Pin Configuration IMX227xF

### **CURRENT SENSE (ISENSE) Pin (Pin 1)**

Connection external LED driver MOSFET source terminal for sensing LED current. An external current sense resistor should be connected between this and the GND pin.

### **SECONDARY GROUND (GND) Pin (Pin 2)**

GND for the secondary IC.

### **CURRENT SOURCE DRIVE (IDRIVE) Pin (Pin 3)**

Connection to external LED driver MOSFET gate terminal for controlling LED current.

### **VOLTAGE SENSE (VSENSE) Pin (Pin 4)**

Connection to external LED driver MOSFET Drain terminal for regulation of voltage to minimise MOSFET power dissipation.

### GATE DRIVE 1 (CDR1) Pin (Pin 5)

Gate driver for external selection MOSFET for V<sub>CV1</sub> output.

### **SECONDARY BYPASS (BPS) Pin (Pin 6)**

Connection for external bypass capacitor which supplies power to the secondary side of the IC.

### LED DIMMING 2 (DIM2) Pin (Pin 7)

LED dimming control input.

### LED DIMMING 1 (DIM1) Pin (Pin 8)

LED dimming control input.

### SYNCHRONOUS RECTIFIER DRIVE (SR) Pin (Pin 9)

Gate driver for external SR MOSFET.

### FORWARD (FWD) Pin (Pin 10)

The connection point to the switching node of the transformer output winding providing information on primary switch timing. Provides power for the secondary-side controller during start-up.

### **OUTPUT VOLTAGE 1 (VCV1) Pin (Pin 11)**

Connected directly to the  $V_{\text{cv1}}$  output voltage, to provide current for the controller on the secondary-side and provide sensing for output voltage regulation and protection.

### **ALTERNATIVE SUPPLY (AS) (Pin 12)**

Alternative supply input for the controller on the secondary-side. Can be left open if not in use

### **LED OUTPUT VOLTAGE (VLED) Pin (Pin 13)**

Connected directly to the LED output voltage, to provide current for the controller on the secondary-side and provide sensing of LED voltage for overvoltage protection.

Figure 10. InnoMux2-EP InSOP-T28B 1CV+1LED Dual Dimming with SR Pin Configuration (Bottom View).

### NC Pin (Pin 14)

Leave open. Should not be connected to any other pins.

### **UNDER/OVER INPUT VOLTAGE (V) Pin (Pin 15)**

A high-voltage pin connected to the AC or DC side of the input bridge for detecting undervoltage and overvoltage conditions at the power supply input. This pin should be tied to SOURCE pin to disable UV/OV protection.

### NC Pin (Pin 16)

Leave open or connect to SOURCE pin or BPP pin.

### PRIMARY BYPASS (BPP) (Pin 17)

The connection point for an external bypass capacitor of the primary-side supply. This is also the  $I_{\text{LIM}}$  selection pin for choosing standard  $I_{\text{IIM}}$  or  $I_{\text{IIM}+1}$ .

### NC Pin (Pin 18)

Leave open. Should not be connected to any other pins.

### SOURCE (S) Exposed Pad (InSOP-T28B Only)

Power switch SOURCE connection. Also ground reference for primary BYPASS pin. Connect all SOURCE pins together. Used to enhance thermal management.

### DRAIN (D) Pin (Pin 28)

Power switch Drain connection.

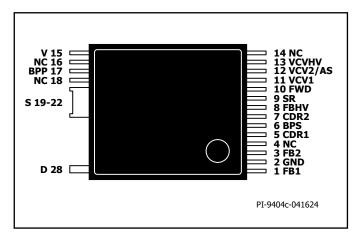

# InnoMux2-EP InSOP-T28D 3CV / 2CV Pin Configuration IMX217xF, IMX237xF

### FEEDBACK 1 (FB1) Pin (Pin 1)

Connection to an external resistor divider to set the power supply output voltage of  $V_{\text{CVI}}$ .

### **SECONDARY GROUND (GND) Pin (Pin 2)**

GND for the secondary IC.

### FEEDBACK 2 (FB2) Pin (Pin 3) / NC for 2CV output

Connection to an external resistor divider to set the power supply output voltage of  $V_{\text{cv2}}$ . Not used for 2CV, leave open should not be connected to any other pins.

### NC Pin (Pin 4)

Leave open. Should not be connected to any other pins.

### GATE DRIVE 1 (CDR1) Pin (Pin 5)

Gate driver for external selection MOSFET for  $V_{\text{CV1}}$  output.

### **SECONDARY BYPASS (BPS) Pin (Pin 6)**

Connection for external bypass capacitor for the secondary IC supply.

### GATE DRIVE 2 (CDR2) Pin (Pin 7) / NC for 2 CV Output

Gate driver for external selection MOSFET for  $V_{\text{CV2}}$  output. Not used for 2CV output, leave open, should not be connected to any other pins.

### FEEDBACK HV (FBHV) Pin (Pin 8)

Connection to an external resistor divider to set the power supply output voltage of  $V_{\text{CVHV}}$

### **SYNCHRONOUS RECTIFIER DRIVE (SR) Pin (Pin 9)**

Gate driver for external SR MOSFET.

### FORWARD (FWD) Pin (Pin 10)

The connection point to the switching node of the transformer output winding providing information on primary switch timing. Provides power for the secondary-side controller during start-up.

### **OUTPUT VOLTAGE 1 (VCV1) Pin (Pin 11)**

Connected directly to the  $V_{\text{CVI}}$  output voltage, to provide current for the controller on the secondary-side and for protection.

### **OUTPUT VOLTAGE 2 (VCV2/AS) Pin (Pin 12)**

Connected directly to the  $V_{cv2}$  output voltage, to provide current for the controller on the secondary-side. Alternative supply as input for 2CV configuration. Can be left open if not in use.

### **OUTPUT VOLTAGE HV (VCVHV) Pin (Pin 13)**

Connected directly to the  $V_{\text{CVHV}}$  output voltage, to provide current for the controller on the secondary-side and for protection.

Figure 11. InnoMux2-EP InSOP-T28D 3CV / 2CV Pin Configuration.

### NC Pin (Pin 14)

Leave open. Should not be connected to any other pins.

### **UNDER/OVER INPUT VOLTAGE (V) Pin (Pin 15)**

A high-voltage pin connected to the AC or DC side of the input bridge for detecting undervoltage and overvoltage conditions at the power supply input. This pin should be tied to SOURCE pin to disable UV/OV protection.

### NC Pin (Pin 16)

Leave open or connect to SOURCE pin or BPP pin.

### PRIMARY BYPASS (BPP) (Pin 17)

The connection point for an external bypass capacitor of the primary-side supply. This is also the  $I_{\text{LIM}}$  selection pin for choosing standard  $I_{\text{I IM}}$  or  $I_{\text{I IM}+1}.$

### NC Pin (Pin 18)

Leave open. Should not be connected to any other pins.

### SOURCE (S) Pin (Pin 19-22)

These pins are the power switch SOURCE connection. Also ground reference for primary BYPASS pin.

### DRAIN (D) Pin (Pin 28)

Power switch Drain connection.

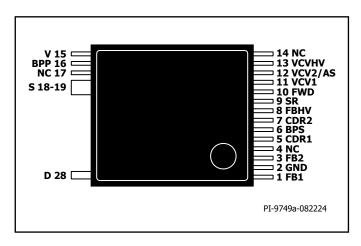

### InnoMux2-EP 2CV/3CV Pin Configuration IMX2353F

### FEEDBACK 1 (FB1) Pin (Pin 1)

Connection to an external resistor divider to set the power supply output voltage of VCV1. Not used with internal feedback\*.

### **SECONDARY GROUND (GND) Pin (Pin 2)**

GND for the secondary IC.

### FEEDBACK 2 (FB2) Pin (Pin 3)

Connection to an external resistor divider to set the power supply output voltage of VCV2. Not used in 2CV configuration or in combination with internal feedback\*.

### NC Pin (Pin 4)

Leave open. Should not be connected to any other pins.

### **GATE DRIVE 1 (CDR1) Pin (Pin 5)**

Gate driver for external selection MOSFET for VCV1 output.

### **SECONDARY BYPASS (BPS) Pin (Pin 6)**

Connection for external bypass capacitor for the secondary IC supply.

### **GATE DRIVE 2 (CDR2) Pin (Pin 7)**

Gate driver for external selection MOSFET for VCV2 output. Not used in 2CV configuration.

### FEEDBACK HV (FBHV) Pin (Pin 8)

Connection to an external resistor divider to set the power supply output voltage of VCVHV.

### SYNCHRONOUS RECTIFIER DRIVE (SR) Pin (Pin 9)

Gate driver for external SR MOSFET.

### FORWARD (FWD) Pin (Pin 10)

The connection point to the switching node of the transformer output winding providing information on primary switch timing. Provides power for the secondary-side controller during start-up.

### **OUTPUT VOLTAGE 1 (VCV1) Pin (Pin 11)**

Connected directly to the VCV1 output voltage, to provide current for the controller on the secondary-side and for protection.

### **OUTPUT VOLTAGE 2 (VCV2/AS) Pin (Pin 12)**

Connected directly to the  $V_{\text{CV2}}$  output voltage, to provide current for the controller on the secondary-side. Alternative supply as input for 2CV configuration. Can be left open if not in use.

### **OUTPUT VOLTAGE HV (VCVHV) Pin (Pin 13)**

Connected directly to the VCVHV output voltage, to provide current for the controller on the secondary-side and for protection.

Figure 12. InnoMux2-EP InSOP-T28G 3CV Pin Configuration.

### NC Pin (Pin 14)

Leave open. Should not be connected to any other pins.

### **UNDER/OVER INPUT VOLTAGE (V) Pin (Pin 15)**

A high-voltage pin connected to the AC or DC side of the input bridge for detecting undervoltage and overvoltage conditions at the power supply input. This pin should be tied to SOURCE pin to disable UV/OV protection.

### PRIMARY BYPASS (BPP) Pin (Pin 16)

The connection point for an external bypass capacitor of the primary-side supply. This is also the ILIM selection pin for choosing standard ILIM or ILIM+1.

### NC Pin (Pin 17)

Leave open. Should not be connected to any other pins.

### **SOURCE (S) Pin (Pin 18-19)**

These Pins are the power switch source connection. Also ground reference for primary BYPASS pin..

### DRAIN (D) Pin (Pin 28)

Power switch drain connection.

### **InnoMux2-EP Functional Description**

The InnoMux2-EP combines a high-voltage power switch, along with both primary-side and secondary-side controllers in one device. The InnoMux2-EP architecture incorporates a novel inductive coupling feedback scheme using the package lead frame and bond wires to provide a safe, reliable, and low-cost means to accurately communicate power requests from the secondary controller to the primary controller.

The primary controller on InnoMux2-EP is a quasi-resonant (QR) flyback controller to operate in continuous conduction mode (CCM) or discontinuous conduction mode (DCM) with Zero voltage switching (ZVS) using advanced SR FET control. The controller uses a variable current control scheme. The primary consists of a jitter oscillator; a receiver circuit magnetically coupled to the secondary controller, a current limit controller, 5 V regulator on the PRIMARY BYPASS pin, audible noise reduction engine, bypass overvoltage detection circuit, a lossless input line sensing circuit, current limit selection circuitry, overvoltage protection, leading edge blanking, secondary output diode / SR MOSFET short protection circuit and a 650 V / 725 V / 750 V and 1700 V power switch.

The secondary controller consists of a transmitter circuit that is magnetically coupled to the primary receiver, multi-output controller for regulating up to three outputs independently, 5 V regulator on the SECONDARY BYPASS pin, synchronous rectifier (SR) MOSFET driver, high-side MOSFET drivers, shunts to prevent individual outputs from rising in abnormal loading conditions, single string LED driver, timing functions and a host of integrated protection features.

Figures 4, 5 and 6 show the functional block diagrams of the primary and secondary controllers with the most important features.

### **Primary Controller**

The InnoMux2-EP IC has variable frequency CCM / CrM / DCM controller plus ZVS operation in DCM for enhanced efficiency and extended output power capability.

For high-voltage input, the 1700 V InnoMUX2-EP (IMX2353F) has a variable frequency DCM only controller plus SR ZVS operation. This DCM ZVS operation achieves zero voltage switching on the primary switch using SR MOSFET. This reduces the capacitive turn on loss and improves efficiency.

### **PRIMARY BYPASS Pin Regulator**

The PRIMARY BYPASS pin has an internal regulator that charges the PRIMARY BYPASS pin capacitor to  $V_{\rm BPP}$  by drawing current from the DRAIN pin whenever the power switch is off. The PRIMARY BYPASS pin is the internal supply voltage node. When the power switch is on, the device operates from the energy stored in the PRIMARY BYPASS pin capacitor.

In addition, a shunt regulator clamps the PRIMARY BYPASS pin voltage to  $V_{\text{SHUNT}}$  when current is provided to the PRIMARY BYPASS pin through an external resistor. This allows the InnoMux2-EP IC to be powered externally through a bias winding, decreasing the no-load consumption and enhancing low-standby-power operation.

### Primary Bypass I, M Programming

InnoMux2-EP ICs allow the user to adjust primary current limit ( $I_{\text{LIM}}$ ) settings through the selection of the PRIMARY BYPASS pin capacitor value. A ceramic capacitor can be used. There are 2 selectable capacitor sizes - 0.47  $\mu\text{F}$  and 4.7  $\mu\text{F}$  for setting standard and increased  $I_{\text{LIM}}$  settings respectively.

### **Primary Bypass Undervoltage Threshold**

The PRIMARY BYPASS pin undervoltage circuitry disables the power switch when the PRIMARY BYPASS pin voltage drops below  ${\sim}4.5~\text{V}$  (=  $\text{V}_{\text{BPP}}-\text{V}_{\text{BPP(H)}}$ ) in steady-state operation. Once the PRIMARY BYPASS pin voltage falls below this threshold, it must rise to  $\text{V}_{\text{BPP(SHUNT)}}$  to re-enable turn-on of the power switch.

### **Primary Bypass Output Overvoltage Function**

The PRIMARY BYPASS pin has an OV protection feature with either a latching or an auto-reset response. A Zener diode in parallel with the resistor in series with the PRIMARY BYPASS pin capacitor is typically used to detect an overvoltage on the primary bias winding and activate the protection mechanism. In the event that the current into the PRIMARY BYPASS pin exceeds  $I_{\text{SD'}}$  the device will latch-off or disable the power switch for a time  $t_{\text{AR}(\text{OFF})'}$  after which time the controller will restart and attempt to return to regulation.

Output OV protection is also included as an integrated feature on the secondary controller.

### **Over-Temperature Protection**

The thermal shutdown circuitry senses the primary switch die temperature. The threshold is set to  $T_{\rm SD}$  with either a hysteretic or latch-off response.

Hysteretic response: If the die temperature rises above the threshold, the power switch is disabled and remains disabled until the die temperature falls by  $T_{\text{SD(H)}}$  at which point switching is re-enabled. A large amount of hysteresis is provided to prevent over-heating of the PCB due to a continuous fault condition.

Latch-off response: If the die temperature rises above the threshold the power switch is disabled. The latching condition is reset by bringing the PRIMARY BYPASS pin below  $V_{BPP(RESET)}$  or by going below the UNDER/OVER INPUT VOLTAGE pin  $UV_{(IUV)}$  threshold.

Over-temperature protection is also included as an integrated feature on the secondary controller.

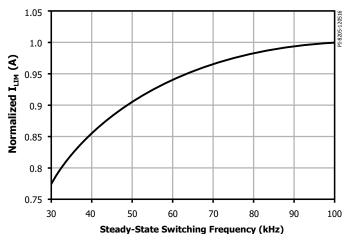

### **Current Limit Operation**

The primary-side controller has a current limit threshold ramp that is inversely proportional to the time from the end of the previous primary switching cycle (i.e. from the time the primary switch turns off at the end of a switching cycle) to the next switching request.

This characteristic produces a primary current limit that increases as the switching frequency (load) increases (Figure 12).

This algorithm enables the most efficient use of the primary switch with the benefit that this algorithm responds to digital feedback information immediately when a feedback switching cycle request is received.

At high load, switching cycles have a maximum current per cycle approaches 100%  $I_{\text{\tiny LM}}.$  This gradually reduces to 30% of the full current limit as load decreases. Once 30% current limit is reached, there is no further reduction in current limit (since this is low enough to prevent audible noise). The time between switching cycles will continue to increase as load reduces.

Figure 13. Normalized Primary Current vs. Switching Frequency.

### **Jitter**

The normalized current limit is modulated between 100% and 95% at a modulation frequency of  $f_{\rm M}$ ; this results in a frequency jitter of ~7 kHz with average frequency of ~100 kHz.

### **Auto-Restart**

In the event a fault condition occurs (such as an output overload, output short-circuit, or external component/pin fault), the InnoMux2-EP enters auto-restart (AR) or latches off. The latching condition is reset by bringing the PRIMARY BYPASS pin below  $\sim\!\!3$  V or by going below the UNDER/OVER INPUT VOLTAGE pin UV $_{\scriptscriptstyle (IUV-)}$  threshold.

In auto-restart, switching of the power MOSFET is disabled for  $t_{\text{AR(OFF)}}$ . There are 2 ways to enter auto-restart:

- 1. Continuous secondary requests received at a rate that is above the overload detection frequency  $(f_{\text{OVL}})$  for longer than 82 ms  $(t_{\text{AR}})$ .

- 2. No requests for switching cycles from the secondary for >t<sub>AR(SK)</sub>.

The secondary controller can initiate an auto-restart by not sending switching request cycles to the primary controller. The primary controller will then restart.

It is also possible that communication is lost, in which case the primary will also try to restart. Although this should never be the case in normal operation, it can be useful when system ESD events(for example) cause a loss of communication due to noise disturbing the secondary controller. The issue is resolved when the primary restarts after an auto-restart off-time.

The auto-restart is reset as soon as an AC reset occurs.

### **SOA Protection**

In the event that there are two consecutive cycles where the  $I_{\text{LIM}}$  is reached within  ${\sim}500$  ns (the blanking time + current limit delay time), the controller will skip 2.5 cycles or  ${\sim}25~\mu s$ . This provides sufficient time for the transformer to reset when operating with large capacitive loads without extending the start-up time.

### **Input Line Voltage Monitoring**

The UNDER/OVER INPUT VOLTAGE pin is used for input undervoltage and overvoltage sensing and protection.

A sense resistor is tied between the high-voltage DC bulk capacitor after the bridge (or to the AC side of the bridge rectifier for fast AC reset) and the UNDER/OVER INPUT VOLTAGE pin to enable this functionality. This function can be disabled by shorting the UNDER/OVER INPUT VOLTAGE pin to primary GND. Please note the maximum voltage for this UNDER/OVER INPUT VOLTAGE pin is 650 V; for above 650 V input DC voltage, an additional external clamp circuit is needed to clamp this pin voltage below 650 V.

At power-up, after the primary bypass capacitor is charged and the  $\rm I_{LIM}$  state is latched, and prior to switching, the state of the UNDER/OVER INPUT VOLTAGE pin is checked to confirm that it is above the brown-in and below the overvoltage shutdown thresholds.

In normal operation, if the UNDER/OVER INPUT VOLTAGE pin current falls below the brown-out threshold and remains below brown-out for longer than  $\mathbf{t}_{\text{UV}}$ , the controller enters auto-restart. Switching will only resume once the UNDER/OVER INPUT VOLTAGE pin current is above the brown-in threshold.

In the event that the UNDER/OVER INPUT VOLTAGE pin current is above the overvoltage threshold, the controller will also enter auto-restart. Again, switching will only resume once the UNDER/OVER INPUT VOLTAGE pin current has returned to within its normal operating range.

The input line UV/OV function makes use of an internal high-voltage MOSFET on the UNDER/OVER INPUT VOLTAGE pin to reduce power consumption. If the cycle off-time  $t_{\mbox{\scriptsize OFF}}$  is greater than 50  $\mu s$ , the internal high-voltage MOSFET will disconnect the external sense resistor from the internal sense circuits to eliminate current drawn through the sense resistor. The line sensing function will reactivate at the beginning of the next switching cycle.

### **Primary-Secondary Handshake**

At start-up, the primary-side initially switches without any feedback information (this is very similar to the operation of a standard TOPSwitch™, TinySwitch™, LinkSwitch™ and other InnoSwitch™ controllers).

If no feedback signals are received during the auto-restart time  $(t_{AR})$ , the primary goes into auto-restart mode. Under normal conditions, the secondary controller will power-up from the FORWARD pin or output voltage and take over control. From this point onwards the secondary controls switching.

If the primary controller stops switching or does not respond to cycle requests from the secondary during normal operation (when the secondary has control), the handshake protocol is initiated to ensure that the secondary is ready to assume control once the primary begins to switch again. An additional handshake is also triggered if the secondary detects that the primary is providing more cycles than were requested.

The most likely event that could require an additional handshake is when the primary stops switching as the result of a momentary line brown-out event. When the primary resumes operation, it will default to a start-up condition and attempt to detect handshake pulses from the secondary.

If secondary does not detect that the primary responds to switching requests, or if the secondary detects that the primary is switching without cycle requests, the secondary controller will initiate a second handshake sequence. This provides additional protection against cross conduction of the SR FET while the primary is switching. This protection mode also prevents an output overvoltage condition in the event that the primary is reset while the secondary is still in control.

### **Wait and Listen**

When the primary resumes switching after initial power-up recovery from an input line voltage fault (UV or OV) or an auto-restart event, it will assume control and require a successful handshake to relinquish control to the secondary controller.

As an additional safety measure the primary will pause for an auto-restart on-time period,  $t_{_{AR}}$  (~82 ms), before switching. During this "wait" time, the primary will "listen" for secondary requests. If it sees two consecutive secondary requests, separated by ~30  $\mu s$ , the primary will infer secondary control and begin switching in slave mode. If no pulses occur during the  $t_{_{AR}}$  "wait" period, the primary will begin switching under primary control until handshake pulses are received.

### **Audible Noise Reduction Engine**

The InnoMux2-EP IC features an active audible noise reduction mode where by the controller (via a "frequency skipping" mode of operation) avoids the resonant band (where the mechanical structure of the power supply is most likely to resonate – increasing noise amplitude) between 7 kHz and 12 kHz – 142  $\mu s$  and 83  $\mu s$ . If a secondary controller switch request occurs within this time window from the last conduction cycle, the gate drive to the power switch is inhibited.

The secondary controller includes an audible-noise-reduction engine.

### **Frequency Soft-Start**

At start-up (before handshake) the primary controller is limited to a maximum switching frequency of  $f_{\text{SW}}$  and 75% of the maximum programmed current limit at the switch-request frequency of 100 kHz.

### **Secondary Controller**

The IC is powered by the 5 V ( $V_{\rm BPS}$ ) regulator which is supplied by either an output or FORWARD pin. The SECONDARY BYPASS pin is connected to an external decoupling capacitor and fed internally from the regulator block.

The FORWARD pin also connects to the detection block used for both handshaking and timing circuit to turn on and regulate the SR FET connected to the SYNCHRONOUS RECTIFIER DRIVE pin. The FORWARD pin voltage is used to determine when to turn off the SR FET in discontinuous mode operation.

In continuous conduction mode (CCM) the SR FET is turned off when a feedback pulse is sent to the primary to demand the next switching cycle, providing excellent synchronous operation, free of any overlap for the FET turn-off.

The FORWARD detector also measures the FORWARD pin voltage during the primary on time, this feeds into the SR zero voltage switching control function.

### **BPS Regulator**

The regulator limits the BPS pin to  $V_{\rm BPS}$ . The BP regulator can use  $V_{\rm CV1}$  or  $V_{\rm CV2/AS}$  as its source. The source is automatically selected as follows:

- V<sub>CV1</sub> is used if VCV1 pin > V<sub>BPS VCV1</sub>, otherwise

- $V_{CV2/AS}$  is used if VCV2 pin >  $V_{BPS\_VCV2}$

$V_{\text{\tiny CVHV}}/V_{\text{\tiny LFD}}$  can only be used as a source for BPS during start-up.During

start-up, the FORWARD pin is also used as a source for BPS. This is provided to support start-up into heavy load and is not intended for continuous operation. The FORWARD pin needs to be a minimum of  $\approx 8$  V when the primary is on in order for this to function correctly.

A 2.2  $\mu$ F or 4.7  $\mu$ F ceramic capacitor on the BPS pin is required. There are no stability requirements on the capacitor; the BPS regulator is unconditionally stable.

### **BPS Regulator - Direct Power**

When  $V_{\text{CVI}}$  is 5 V ( $V_{\text{CVSV\_BPS}}$ ) the BPS pin is automatically connected internally to the VCV1 pin, directly powering BPS instead of using the BPS linear regulator. This reduces power loss in the secondary controller and reduces standby power. This is automatically selected when  $V_{\text{CVI}}$  is  $V_{\text{CVSV\_BPS}}$ .

### **High-Side MOSFET Drive**

The high-side selection MOSFETs are driven with a drive voltage that is 5 V above the given output using a capacitive drive approach. The capacitive drive approach benefits from easy level translation by use of a capacitor CDR capacitor-drive (CDR) . A regular refresh cycle to top up the charge on the CDR is needed when one of the switches has been on for a long time, as the charge on the CDR will otherwise slowly leak away. Refresh is also needed during start-up to allow the CDR to follow the output voltage when the output is being pulled up. The controller will perform refresh cycles when necessary by turning the selection MOSFET off and then back on.

The default refresh time is  $T_{\text{REFRESH'}}$ , which is doubled to  $2 \times T_{\text{REFRESH}}$  during start-up. The longer the refresh time the better, but the MOSFET needs to be turned back on before the end of the primary on time. Once the CV outputs are in regulation the refresh time is reduced to  $T_{\text{REFRESH'}}$ . Because the output is no longer changing, the refresh is only needed to top up CDR and by reducing the refresh time the risk of the primary on time finishing before the refresh is reduced.

A diode is required to be placed between the gate-source of each selection MOSFET to provide a path for charging the capacitor. A low forward voltage diode such as a Schottky diode should be used.

The optimal capacitor value for CDR depends on the gate charge of the selection MOSFET. The selection MOSFET on-level gate voltage is determined by  $V_{\mbox{\tiny BPS}} \times (C_{\mbox{\tiny DR}}/(C_{\mbox{\tiny G}} + C_{\mbox{\tiny DR}})$ , so it is essential that the gate charge (at 5 V gate voltage) is much smaller than the charge in the CDR capacitor. A typical value for the CDR capacitor is 100 nF. For higher CDR capacitor values, the refresh time might be insufficient and the capacitor will not be able to follow the output during start-up. It is therefore important to select low gate-charge devices for the selection MOSFETs to minimise the required CDR capacitor value as well as to minimise energy required to drive the MOSFETs.

### **High-Side MOSFET Static Pull-Down**

To ensure that the selection MOSFET gates are held low when the secondary is not in control, the CDR1 and CDR2 pins have an internal pull down circuit "ON" feature to pull the pin low and reduce any voltage on the gate due to capacitive coupling.

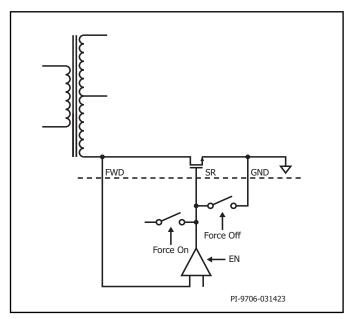

### **Synchronous Rectifier Driver**

The SR driver on the InnoMux2-EP IC is not an "on/off" driver. The SR MOSFET's gate-source voltage is modulated to regulate the FORWARD pin voltage to roughly -40 mV while the discharge current is flowing in the SR MOSFET. The regulated approach allows for improved noise immunity, removing the possibility of the MOSFET being turned off too early causing increased power loss.

A force-on signal provides a boost when turning on the SR MOSFET to charge the gate-source capacitance quickly. A force off signal is used to quickly discharge the gate-source capacitance when operating in CCM and also ensure the MOSFET is held off when the secondary is not conducting.

Figure 14. Synchronous Rectifier Driver Diagram.

For optimum performance, an SR MOSFET with a gate-source capacitance of less than 10 nF is recommended.

### **SR Disable Protection**

In each cycle the SR is only engaged if a new cycle is requested by the secondary controller and the negative edge is detected on the FORWARD pin.

### **SR Static Pull-Down**

To ensure that the SR gate is held low when the secondary is not in control, the SYNCHRONOUS RECTIFIER DRIVE pin has internal pull down circuit "ON" device to pull the pin low and reduce any voltage on the SR gate due to capacitive coupling from the FORWARD pin.

### **Short/Open SR Protection**

In order to protect against the SYNCHRONOUS RECTIFIER DRIVE pin system faults, (an SR pin short to ground or SR pin open), the secondary controller has a protection mode that ensures that the SYNCHRONOUS RECTIFIER DRIVE pin is connected to an external FET. If the external capacitance on the SYNCHRONOUS RECTIFIER DRIVE pin is less than 200 pF, the device will assume that the SYNCHRONOUS RECTIFIER DRIVE pin is "open". If the external capacitance on the SYNCHRONOUS RECTIFIER DRIVE pin is above 20 nF, the device will assume the SYNCHRONOUS RECTIFIER DRIVE pin is "short". In either of these two cases a fault is detected otherwise the controller will assume an SR FET is connected.

In the event SYNCHRONOUS RECTIFIER DRIVE pin fault is detected the secondary controller will stop requesting pulses from the primary and initiate auto-restart.

### **Multi-Output Control**

The multi-output control regulates each output independently by requesting pulses from the primary based on the FB pin voltages of each output. The transformer energy is then directed to the output that needs the energy on a cycle-by-cycle basis. This is accomplished by turning on the appropriate selection MOSFET in series with either the CV1 or the CV2 output. The transformer shall be designed such that the  $V_{\rm OR}$  increases between  $V_{\rm CV1}$  and  $V_{\rm CV2}$  and between  $V_{\rm CVHV}/V_{\rm LED}$ . This guarantees that the current through the  $V_{\rm LED}$  diode is negligible when the selection MOSFET for either  $V_{\rm CV1}$  or  $V_{\rm CV2}$  is turned on, disabling both MOSFETs will direct the energy delivery to the LED output.

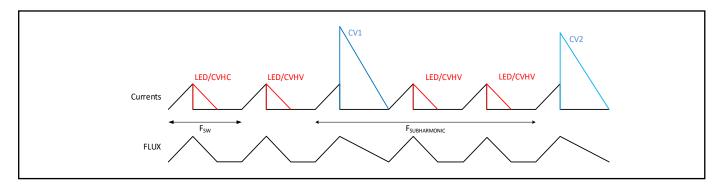

### **InnoMux2-EP Enhanced Audible Noise Reduction**

The InnoMux2-EP IC has enhanced features for audible noise reduction.

Multi-output control can create sub-harmonic frequencies of the switching frequency in the flux of the transformer. These sub-harmonics can fall in the audible range. THE InnoMux2-EP IC avoids such conditions by sharing fractions of discharge pulses between outputs.

This is achieved by allowing the first part of the discharge pulse to the V $_{\rm CVHV}/V_{\rm LED}$  output and then turning on the selection MOSFET part way through the discharge and allowing the second part of the discharge to flow via the V $_{\rm CV1}$  or V $_{\rm CV2}$  output. The point at which the MOSFET is turned on to switch over from the L $_{\rm ED}/C_{\rm VHV}$  output to the CV1 or CV2 output is dependent on the relative loading of the outputs.

This provides an added benefit of reducing the RMS currents in the secondary windings, reducing power loss. The operating frequency of each output is increased (while the power switch frequency remains the same) reducing the output ripple for a given filter capacitance.

Figure 15. Multi-Output Control Switching Pattern.

Figure 16. InnoMux2-EP Switching Pattern.

### **Output Capacitance Requirement**

The InnoMux2-EP IC has a minimum output capacitance requirement for each output to ensure optimum operation. This is given by the following equation:

$$C_{\text{outses}} = \frac{L_{\text{PRI}} \times I_{\text{LIMIT}}^2}{4 \times \frac{V_{\text{OUT}}^2}{V_{\text{FB(REG)}}} \times V_{\text{SHTHR}}}$$

Where:

$L_{_{PRI}}$  is the primary inductance  $I_{_{LIMIT}}$  is the primary peak current  $V_{_{OUT}}$  is the output voltage for the given output  $V_{_{SHTHR}}$  is 10 mV for CV outputs and  $\,$  5 mV for  $V_{_{LED}}$  output  $V_{_{FB(REG)}}$  internal voltage comparator reference voltage

### **Minimum Off-Time**

The secondary controller initiates a cycle request using the FluxLink magneto-inductive connection to the primary. The maximum frequency of secondary cycle requests is limited by the minimum cycle off-time of  $t_{\rm OFF(MIN)}.$  This ensures that there is sufficient reset time after primary conduction to deliver energy to the load.

### **Maximum Switching Frequency**

The maximum switch-request frequency from the secondary controller is  $f_{\mbox{\tiny SRFO}}.$

### **Maximum Secondary Inhibit Period**

Secondary requests to initiate primary switching are inhibited when necessary to maintain operation below maximum frequency and ensure minimum off-time. Secondary-cycle requests are also inhibited during the "ON" time cycle of the primary switch (time between the cycle request and detection of FORWARD pin falling edge). The maximum time-out in the event that a FORWARD pin falling edge is not detected after a cycle request is  $\sim 30~\mu s$ .

### **Feedback**

For applications with CV only outputs, output voltage feedback is provided by the FEEDBACK pins (FB1, FB2, FBHV) and is used for  $\,$

output voltage regulation of each output. The internal voltage comparator reference voltage is  $V_{\text{FB(REG)}}$ .

The FB pins are noise sensitive so the feedback resistor networks need to be placed close to the IC. The FORWARD pin signal path must not be placed near the FB nodes. The resistor between the FB pins and GND should be 1-5 k $\Omega$ . A 100 pF capacitor may also be placed between the FB pins and GND to reduce noise.

### **FEEDBACK Pin Short/Open Detection**

At start-up the sensed FB pin voltage is below  $V_{\text{FB(OFF)}}$  after a number switching cycles, the secondary controller will complete the handshake to take control but will stop requesting cycles to initiate auto-restart (no cycle requests made to primary for longer than  $t_{\text{AR(SK)}}$  second triggers auto-restart).

A weak internal pull-down for the FB pins allows FB pin-open to be detected.

When using the internal feedback (as is the case for applications with the LED output), this protection mechanism also applies. This protects against faults with the VCV1 and VLED pins.

### **Output Voltage Protection**

If the output voltage is 12% higher than the regulation threshold for  $\rm V_{CV1}$ , or  $\rm V_{CV2}$ , 20% higher than the regulation threshold for  $\rm V_{CVHV}$  or 16% higher than the regulation threshold for  $\rm V_{LED}$  a command is sent to the primary to either latch-off or begin an auto-restart sequence. This integrated output OVP can be used in conjunction or independently to the primary sensed OVP.

### **Shunts**

The LV shunt is designed to limit the voltage lift on the  $V_{\text{CVI}}$  output. Voltage lift on the  $V_{\text{CVI}}$  output will typically occur due to its lower  $V_{\text{OR}}$ . At turn-on of the  $V_{\text{CVI}}$  selection MOSFET after delivery of a pulse to one of the other outputs, a small amount of energy is delivered to the  $V_{\text{CVI}}$  output from the higher idle ring voltage. The LV shunt is turned on when the sensed voltage exceeds  $V_{\text{LV(SHUNT)}}$ .

In practical applications it is unlikely that the  $V_{\text{CV1}}$  output will lift;  $V_{\text{CV1}}$  output lift typically only occurs when the  $V_{\text{CV1}}$  output is unloaded while the other outputs are running at high load. It is likely  $V_{\text{CV1}}$  is powering the secondary controller and this alone is sufficient to prevent lift.

The HV shunt is used to limit the voltage on the  $V_{\text{CVHV}}/V_{\text{LED}}$  rail to the maximum allowed voltage in case of peak-charging of the  $V_{\text{CVHV}}/V_{\text{LED}}$  output when the  $V_{\text{CVHV}}/V_{\text{LED}}$  output is not loaded. This peak charging is predominantly caused by leakage in the transformer; the  $V_{\text{CVHV}}/V_{\text{LED}}$  output typically has lowest leakage and thus will receive a small amount of energy from switching cycles that are destined for  $V_{\text{CV1}}$  or  $V_{\text{CV2}}$ . The HV shunt is turned on when the sensed voltage exceeds  $V_{\text{HV(SHUNT)}}$ .

Note that the  $\rm V_{\rm cv2}$  output does not need a shunt as this output is not susceptible to peak charging or unintended energy delivery.

### **Overload / Short-Circuit Protection**

The  $V_{\text{CVI}}$ ,  $V_{\text{CV2}}$  and  $V_{\text{CVHV}}/V_{\text{LED}}$  outputs have a maximum power protection feature. The controller determines whether the output is more than 10% (CV outputs) or more than 1% ( $V_{\text{LED}}$  output) below the set point. If this condition persists for multiple switching cycles, then the output is assumed to be overloaded – either the output has a short-circuit, or the output power capability of the power supply has been exceeded and it cannot maintain regulation.

### **Over-Temperature Latch-Off**

The thermal shutdown circuitry senses the secondary die temperature. The threshold is set to  $T_{\rm SD/SEC}$ .

Primary control over-temperature is the main temperature protection feature and includes hysteresis. The secondary controller also has over temperature protection but once reached creates a latch-off condition as hysteresis is not available.

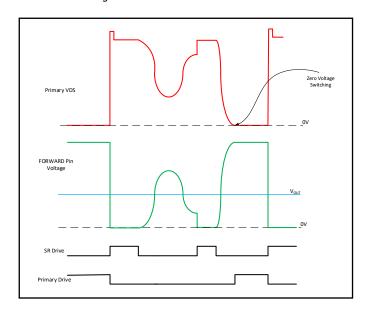

### **DCM ZVS Mode Switching**

The InnoMux2-EP IC features Zero Voltage Switching (ZVS) in the primary switch while the converter is operating in discontinuous conduction mode (DCM). This is achieved using the synchronous rectifier (SR) MOSFET. This mode of operation is disabled in continuous conduction mode (CCM). IMX2353F (1700 V) exclusively operates in DCM ZVS mode.

Before turning on the primary switch, the SR MOSFET is turned on at the valley of the idle ring on the FORWARD Pin. The SR MOSFET is kept on to charge the transformer's magnetizing inductance. The SR MOSFET is turned off and the voltage on the primary is allowed to ring down to near zero volts at which point the primary switch is turned on.

The SR MOSFET on-time for achieving ZVS is automatically calculated by the InnoMux2-EP controller. This corrects for design parameters, input voltage and output voltage. The calculation is based on the FORWARD Pin voltage during the primary on-time. To sample the FORWARD Pin voltage correctly the primary on-time needs to be at least 500 ns and FORWARD Pin voltage needs to be less than 100 V.

ZVS is not available when the LED is disabled or when operating below 15 kHz for output IMX2267 – IMX2268. In this case quasi-resonant switching is used.

Figure 17. DCM ZVS Mode Switching.

### **DCM Only Mode**

With PFC input or for a high-line (only) input design, DCM is always preferred due to the lower SR voltage spike when the primary turns on. The InnoMux2-EP IC has an option to only allow DCM switching. To ensure power delivery in a corner case condition, a  $K_p > 1.2$  is recommended to enable this feature. This DCM ZVS mode is applied to IMX2353F (1700 V).

### **LED Current Control Operation**

The InnoMux2-EP IC features an LED driver for controlling the current through an LED string. To provide application flexibility with regard to voltage and current, an extra MOSFET and sense resistor are used.

The LED driver uses the sense resistor to monitor LED current and adjusts the MOSFET gate voltage to control it. The maximum LED current is given by:

$$I_{\text{led(MAX)}} = \frac{V_{\text{ISENSE(MAX)}}}{R_{\text{ISENSE}}}$$

The external MOSFET must be a logic level type with a low gatesource threshold voltage. The maximum drive voltage is V<sub>IDRIVE(SAT)</sub>.

Figure 18. InnoMux2-EP LED Driver.

Output Voltage Regulation for  $V_{\text{LED}}$  Output To maximize efficiency the InnoMux2-EP IC keeps the voltage drop across the current source as low as possible. The output voltage for driving the LED string  $(V_{LED})$  is therefore regulated according to the minimum required voltage drop across the current source. The low voltage drop across the current source is maintained for any LED current by changing the  $V_{\text{\tiny LED}}$  output voltage set point.

The minimum voltage setting is configurable to accommodate a range of LED requirements and MOSFET characteristics.

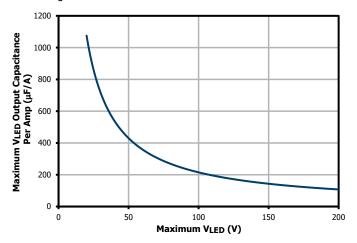

To ensure stability of the LED voltage regulation a maximum  $\boldsymbol{V}_{\text{\tiny LED}}$ output capacitance is recommended which depends on the maximum LED voltage and the maximum LED current.

Figure 19. Maximum LED Output Capacitance.

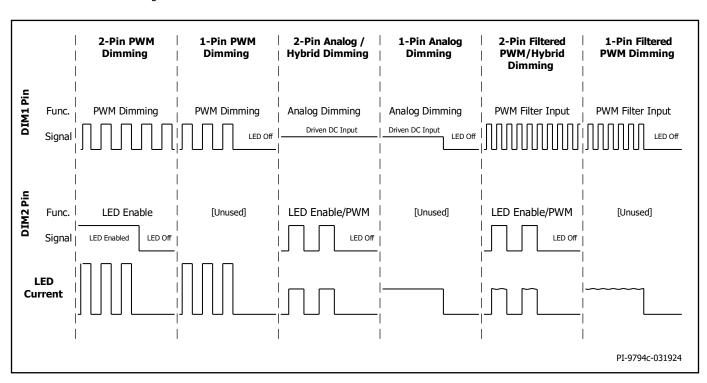

### **LED Dimming**

The current through the LED strings can be varied to change the LED brightness.

The InnoMux2-EP IC supports multiple dimming modes, the choice of which depends on whether 1 or 2 dimming pins are available. The dimming mode is also configurable.

Figure 19 provides an overview of the available dimming modes in the InnoMux2-EP IC.

### **PWM Dimming**

In this mode, the LED current steps from zero to  $I_{\mbox{\tiny LED(MAX)}}$  at a frequency given by the PWM input. The LED average current is controlled by the duty cycle of the PWM input.

PWM dimming is supported by applying a PWM signal with desired duty cycle to the DIM1 pin. The allowed PWM frequency range is given by PWM<sub>F(RANGE)</sub>. Pulling the DIM1 pin low disables the LEDs.

When the DIM2 pin is available this also acts as an enable/disable signal, pulling the DIM2 pin low disables the LEDs. In this case both DIM1 and DIM2 need to be high to enable the LEDs.

Pulling DIM1 or DIM2 low is intended to disable the LEDs during a 'screen-off' mode. Disabling the LED regulator will reduce the InnoMux2-EP IC current consumption.

The LED driver is limited to a minimum on-time  $(\underline{t}_{\text{\tiny LED(ON)MIN}})$  which limits the minimum duty cycle and a minimum off time  $t_{\text{LED(OFF)MIN}}$  which limits the maximum duty cycle before reaching 100%. 100% duty is achievable.

### **Analog Dimming**

In this mode, the LED current is continuous and is proportional to the DIM1 pin voltage.  $V_{\text{ADIM}(\text{MAX})}$  on DIM1 pin corresponds to  $I_{\text{LED}(\text{MAX})'}$  reducing the DIM1 pin voltage reduces the LED current in a linear fashion. Pulling DIM1 pin below  $V_{\text{ADIM}(\text{DISABLE})}$  disables the LEDs and they remain disabled until DIM1 pin is above  $V_{\text{ADIM}(\text{ENABLE})}$ .

When the DIM2 pin is available this also acts as an enable/disable signal, pulling the DIM2 pin low disables the LEDs. In this case both DIM1 and DIM2 need to be high to enable the LEDs.

Additionally, when the DIM2 pin is available this pin can be used as a PWM input. This allows the LED brightness to be controlled by adjusting both the current duty cycle and the current level. This is described further in the Hybrid Dimming section.

### **Filtered PWM Dimming**

In this mode, the LED current is continuous (as in Analog Dimming). The LED current level is proportional to the DIM1 pin duty cycle. This avoids the need for generating an accurate analog voltage, instead a regular PWM signal can be used and the controller converts the duty cycle to an analog current level.

100% duty cycle on the DIM1 pin corresponds to  $I_{\text{LED(MAX)}'}$  reducing the DIM1 pin duty cycle reduces the LED current in a linear fashion from 100% down to 3%. The allowed PWM frequency range is FPWM  $_{\text{F(RANGE)}}$ . Pulling DIM1 pin low disables the LEDs.

When the DIM2 pin is available this also acts as an enable/disabled signal, pulling the DIM2 pin low disables the LEDs. In this case both DIM1 and DIM2 need to be high to enable the LEDs.

Additionally, when the DIM2 pin is available this pin can be used as a PWM input. This allows the LED brightness to be controlled by adjusting both the current duty cycle and the current level. Described further in the Hybrid Dimming section.

### **Hybrid Dimming**

Hybrid dimming combines adjusting the LED current by adjusting the peak level in an analog fashion and by pulsing the LED current where by the duty cycle is adjusted.

Hybrid dimming is only possible when both DIM1 and DIM2 pins are available. DIM1 is either an analog voltage input or a PWM input which is internally converted to an analog level. DIM2 is a PWM input. The analog, filtered PWM and PWM inputs behave as described in previous sections.

The combined LED dimming level from both inputs is not intended to go below 1% of  $I_{\text{I-FD(MAX)}}$  (i.e. 10% analog and 10% PWM).

### **LED Faults**

The InnoMux2-EP IC features LED fault protection. LED open, LED driver MOSFET Drain short to  $\rm V_{LED}$  and LED short to ground are all protected against.

If LED open is detected, the power supply will continue to operate but with the LED output disabled until restart. The other faults result in restart or latch-off.

Figure 20. InnoMux2-EP Dimming Modes.

# Design Considerations When Using PowiGaN Devices (IMX2353F)

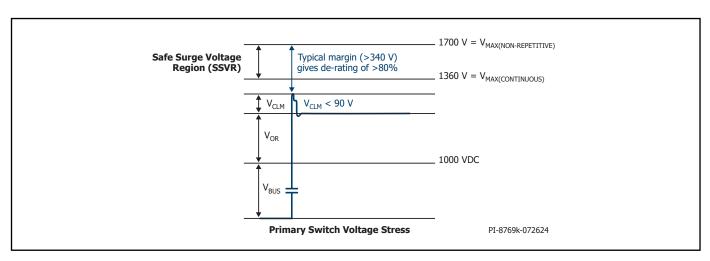

For a flyback converter configuration, typical voltage waveform at the DRAIN pin of the IC is shown in Figure 20. VOR is the reflected output voltage across the primary winding when the secondary is conducting. VBUS is the DC voltage connected to one end of the transformer primary winding. In addition to VBUS+VOR, the drain also sees a large voltage spike at turn off that is caused by the energy stored in the leakage inductance of the primary winding. To keep the drain voltage from exceeding the rated maximum continuous drain voltage, a clamp circuit is needed across the primary winding. The forward recovery of the clamp diode will add a spike at the instant of turn-OFF of the primary switch.

VCLM in Figure 20 is the combined clamp voltage including the spike. The peak drain voltage of the primary switch is the total of VBUS, VOR and VCLM. VOR and the clamp voltage VCLM should be selected such that the peak drain voltage is lower than 1450 V for all normal operating conditions. This provides sufficient margin to ensure that occasional increase in voltage during input transients will maintain the peak drain voltage well below 1700 V.

Due to DCM operation only for IMX2353F, set reflected output voltage (VOR) to main  $K_{\circ} \geq 1$  for all input range conditions.

Figure 21. Peak Drain Voltage for 1000 VDC Input Voltage.

### Absolute Maximum Ratings1,2

| - 1 0 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1                                       |

|-----------------------------------------------------------------------------|

| DRAIN Pin Voltage: IMX2267-IMX2268                                          |

| BPP/BPS Pin Voltage0.3 V to 6 V                                             |

| BPP Pin Current                                                             |

| FWD Pin Voltage1.5 V to 250 V                                               |

| SR Pin Voltage0.3 V to 6 V                                                  |

|                                                                             |

| VCV1, VCV2/AS Pin Voltage0.3 V to 30 V VCVHV/VLED Pin Voltage0.3 V to 250 V |

|                                                                             |

| CDR1, CDR2 Pin Voltage0.3 V to 6 V                                          |

| DIM1, DIM2 Pin Voltage0.3 V to 6 V                                          |

| ISENSE Pin Voltage0.3 V to 6 V                                              |

| IDRIVE Pin Voltage0.3 V to 6 V                                              |

| VSENSE Pin Voltage0.3 V to 250 V                                            |

| Storage Temperature                         | -65 to | 150 °C |

|---------------------------------------------|--------|--------|

| Operating Junction Temperature <sup>3</sup> |        |        |

| Operating Ambient Temperature               |        |        |

| Lead Temperature <sup>4</sup>               |        | 260 °C |

### Notes:

- 1. All voltages referenced to SOURCE and secondary GROUND,  $\rm T_{\rm a} = 25~^{\circ}C.$

- Maximum ratings specified may be applied one at a time without causing permanent damage to the product. Exposure to Absolute Maximum Ratings conditions for extended periods of time may affect product reliability.

- 3. Normally limited by internal circuitry.

- 4. 1/16" from case for 5 seconds.

- Maximum Drain voltage (non-repetitive pulse) .....-0.3 V to 750 V Maximum continuous Drain voltage.....-0.3 V to 650 V

- Maximum Drain voltage (non-repetitive pulse) ... -0.3 V to 1700 V Maximum continuous Drain voltage.....-0.3 V to 1360 V

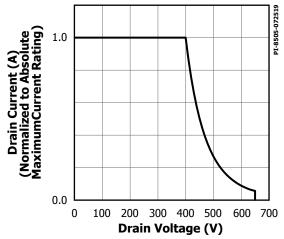

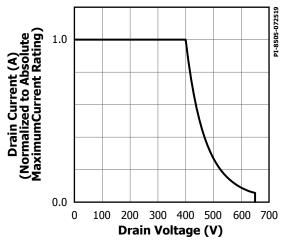

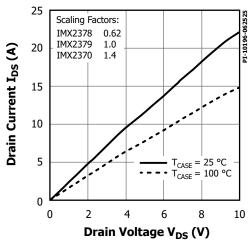

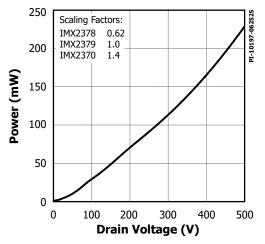

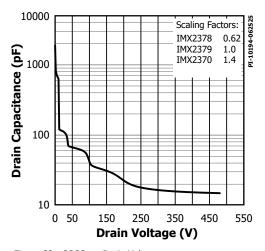

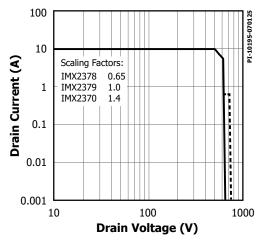

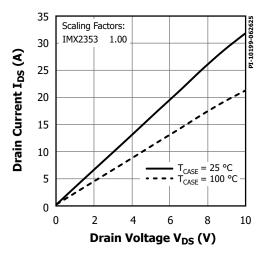

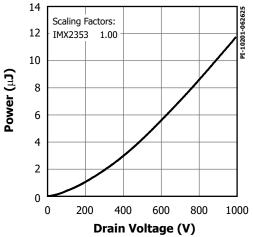

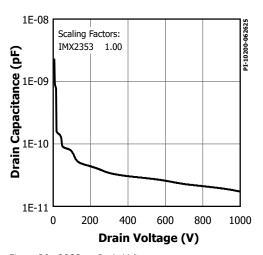

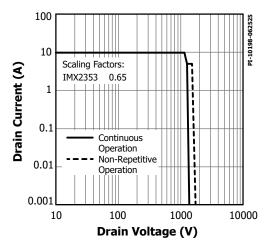

- Higher peak Drain current is allowed while Drain voltage is simultaneously less than 400 V. Please refer to Figure 21 and Figure 26.

- 8. Please refer to Figure 33 and Figure 37 about maximum voltage and current combinations.

### **Thermal Resistance**

Thermal Resistance: IMX2267 - IMX2268 InSOP-24B

| $(\theta_{1\Delta})$ | 48 °C/W <sup>2</sup> , | 43 °C/W <sup>3</sup> |

|----------------------|------------------------|----------------------|

|                      |                        |                      |

### IMX2278 - IMX2270 InSOP-T28B

| $(\theta_{1A})$ | 71-60 °C/W <sup>2,4</sup> , 63-55 °C/W <sup>3,4</sup> |

|-----------------|-------------------------------------------------------|

| $(\theta_{1C})$ | 8-3 °C/W <sup>2,4,5</sup>                             |

### IMX2174 - IMX2177 InSOP-T28D

| $(\theta_{JA})$ | )55-52 °C/W <sup>2,4</sup> , 50-42 °C/W <sup>3,4</sup> |

|-----------------|--------------------------------------------------------|

| $(\theta_{10})$ | ) 10-7 °C/W <sup>2,4,5</sup>                           |

### IMX2378 - IMX2370 InSOP-T28D

| $(\theta_{1\Delta})$ | 71-68 | °C/W <sup>2,4</sup> , | 65-57 | °C/W <sup>3,4</sup>  |

|----------------------|-------|-----------------------|-------|----------------------|

| (A )                 | 1     |                       | 19-9  | C/W <sup>2,4,5</sup> |

### IMX2353 InSOP-T28G

| $(\theta_{1\Delta})$ | )71-68 °C/W <sup>2</sup> , 65-57 | °C/W <sup>3</sup> |

|----------------------|----------------------------------|-------------------|

| $(\theta_{10})$      | ) 19-9                           | °C/W <sup>2</sup> |

### Notes:

- The case temperature is measured on the top of the package.

- 2. Soldered to 0.36 sq. inch (232 mm $^2$ ), 2 oz. (610 g/m $^2$ ) copper clad.

- 3. Soldered to 1.0 sq. inch (645 mm $^2$ ), 2 oz. (610 g/m $^2$ ) copper clad.

- Highest thermal resistance corresponds to controllers with highest primary switch R<sub>DS(ON)</sub> and then reduces for controllers with lower R<sub>DS(ON)</sub> due to the larger device size.

- 5. The  $\theta_{\rm Jc}$  is measured to the bottom of the package for exposed pad packages (InSOP-24B, InSOP-T28B) and to the top of the package for overmolded packages (InSOP-24D, InSOP-T28D, InSOP-T28G).

| Parameter                                      | Symbol                  | Conditions  SOURCE = 0 V $T_{_{J}}$ = -40 °C to 125 °C  (Unless Otherwise Specified)          |                    |                                   | Min   | Тур   | Max                   | Units |

|------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------|--------------------|-----------------------------------|-------|-------|-----------------------|-------|

| Control Functions                              |                         |                                                                                               |                    |                                   |       |       |                       |       |

| Start-Up Switching<br>Frequency                | f <sub>sw</sub>         | T <sub>3</sub> = 25 °C                                                                        |                    |                                   | 23    | 25    | 27                    | kHz   |

| Jitter Modulation<br>Frequency                 | f <sub>M</sub>          | $T_{j} = f_{SW} = 1$                                                                          | Z                  | 0.8                               | 1.25  | 1.70  | kHz                   |       |

| Maximum On-Time                                | t <sub>on(MAX)</sub>    | T <sub>3</sub> = 25 °C                                                                        |                    |                                   | 12.4  | 14.6  | 16.9                  | μS    |

| Minimum Primary<br>Feedback Block-Out<br>Timer | t <sub>BLOCK</sub>      |                                                                                               |                    |                                   |       |       | t <sub>OFF(MIN)</sub> | μS    |

|                                                |                         | $V_{BPP} = V_{BPP} + 0.1 V$                                                                   |                    | 2174 – IMX2177,<br>2267 – IMX2268 |       | 200   | 300                   |       |

|                                                | $I_{S1}$                | (MOSFET not<br>Switching) T <sub>1</sub> = 25 °C                                              | IMX                | 2x78, IMX2x79,<br>(2x70, IMX2353  |       | 375   | 460                   | μΑ    |

|                                                |                         |                                                                                               |                    | IMX2174                           | 0.44  | 0.58  | 0.83                  |       |

|                                                |                         |                                                                                               |                    | IMX2175                           | 0.59  | 0.79  | 1.10                  | -     |

|                                                |                         |                                                                                               |                    | IMX2176                           | 0.77  | 1.02  | 1.38                  |       |

| BPP Supply Current                             | I <sub>52</sub>         | $V_{BPP} = V_{BPP} + 0.1 \text{ V}$ (MOSFET Switching at $f_{SREC}$ ) $T_{J} = 25 \text{ °C}$ |                    | IMX2177                           | 0.90  | 1.20  | 1.73                  | mA    |

|                                                |                         |                                                                                               |                    | IMX2267                           | 0.77  | 1.03  | 1.38                  |       |

|                                                |                         |                                                                                               |                    | IMX2268                           | 0.90  | 1.20  | 1.75                  |       |

|                                                |                         |                                                                                               |                    | IMX2x78<br>IMX2353                |       | 2.10  |                       |       |

|                                                |                         |                                                                                               |                    | IMX2x79                           |       | 2.95  |                       |       |

|                                                |                         |                                                                                               |                    | IMX2x70                           |       | 2.96  |                       |       |

|                                                | I <sub>CH1</sub>        | V <sub>BP</sub> = 0 V, T <sub>J</sub> = 25 °C                                                 |                    |                                   | -1.75 | -1.35 | -0.88                 |       |

| BPP Pin Charge Current                         | I <sub>CH2</sub>        | V <sub>BP</sub> = 4 V,                                                                        | T <sub>1</sub> = 2 | 5 °C                              | -5.98 | -4.65 | -3.32                 | mA    |

| BPP Pin Voltage                                | V <sub>BPP</sub>        | $T_{j} = 1$                                                                                   | 25 °C              |                                   | 4.8   | 5     | 5.16                  | V     |

| BPP Pin Voltage<br>Hysteresis                  | V <sub>BPP(H)</sub>     | $T_{j} = 1$                                                                                   | 25 °C              |                                   |       | 0.39  |                       | V     |

| BPP Shunt Voltage                              | V <sub>SHUNT</sub>      | $I_{BPP} =$                                                                                   | 2 mA               |                                   | 5.15  | 5.36  | 5.65                  | V     |

| BPP Power-Up Reset<br>Threshold voltage        | V <sub>BPP(RESET)</sub> | $T_{j} = 1$                                                                                   | 25 °C              |                                   | 2.80  | 3.15  | 3.50                  | V     |

| UV/OV Pin Brown-In<br>Threshold                | I <sub>UV+</sub>        | $T_j = 1$                                                                                     | 25 °C              |                                   | 23.6  | 25.8  | 28                    | μА    |

| UV/OV Pin Brown-Out<br>Threshold               | I <sub>UV-</sub>        | $T_j = 1$                                                                                     | 25 °C              |                                   | 20    | 23    | 24.5                  | μА    |

| Brown-Out Delay Time                           | t <sub>uv-</sub>        | T <sub>1</sub> = 25 °C                                                                        |                    |                                   |       | 35    |                       | ms    |

| UV/OV Pin Line<br>Overvoltage Threshold        | I <sub>OV+</sub>        | $T_{j} = 1$                                                                                   |                    | 106                               | 115   | 118   | μΑ                    |       |

| UV/OV Pin Line<br>Overvoltage Hysteresis       | I <sub>OV(H)</sub>      | $T_{j} = 1$                                                                                   | 25 °C              |                                   |       | 7     |                       | μΑ    |

| Parameter                                              | Symbol               | Condition<br>SOURCE = 0<br>$T_1 = -40$ °C to 1<br>(Unless Otherwise         | Min      | Тур   | Max   | Units |    |

|--------------------------------------------------------|----------------------|-----------------------------------------------------------------------------|----------|-------|-------|-------|----|

| Control Functions (cont.)                              |                      |                                                                             |          |       |       |       |    |

| UV/OV Pin Line<br>Overvoltage Recovery<br>Threshold    | I <sub>ov-</sub>     | T <sub>3</sub> = 25 °C                                                      |          | 100   |       |       | μА |

| Line Fault Protection                                  |                      |                                                                             |          |       |       |       |    |

| UV/OV Pin Overvoltage<br>Deglitch Filter               | t <sub>ov+</sub>     | T <sub>1</sub> = 25 °C                                                      |          |       | 3     |       | μS |

| Circuit Protection                                     |                      |                                                                             |          |       |       |       |    |

|                                                        |                      | di/dt = 500 mA/ $\mu$ s<br>T $_{_{\mathrm{J}}}$ = 25 °C                     | IMX2267C | 1.84  | 2.0   | 2.16  | А  |

|                                                        |                      | $di/dt = 575 \text{ mA/}\mu\text{s}$ $T_{_{J}} = 25 \text{ °C}$             | IMX2268C | 2.08  | 2.3   | 2.52  |    |

|                                                        |                      | di/dt = 650 mA/μs<br>T <sub>1</sub> = 25 °C                                 | IMX2278F | 2.39  | 2.6   | 2.81  |    |

|                                                        |                      | di/dt = 725 mA/μs<br>T <sub>1</sub> = 25 °C                                 | IMX2279F | 2.63  | 2.9   | 3.19  |    |

|                                                        |                      | di/dt = 848 mA/μs<br>T <sub>1</sub> = 25 °C                                 | IMX2270F | 3.13  | 3.39  | 3.67  |    |

|                                                        |                      | di/dt = 188 mA/μs<br>T <sub>1</sub> = 25 °C                                 | IMX2174F | 0.697 | 0.750 | 0.803 |    |

| Standard Current Limit<br>(BPP) Capacitor =<br>0.47 µF | I <sub>LIMIT</sub>   | di/dt = 288 mA/μs<br>T <sub>1</sub> = 25 °C                                 | IMX2175F | 1.06  | 1.15  | 1.24  |    |