# **HiperPFS-5** Family

# Power Factor Correction (PFC) Controller with Integrated 750 V PowiGaN Switch

# **Product Highlights**

- · High efficiency and power factor across load range

- >98% efficient from 10% to 100% load

- 0.96 PF at 20% load

- Quasi-resonant Discontinuous Conduction Mode (DCM) control

- Up to 250 W output without heat sink

- · PFC stages can be paralleled for increased output power

- · Smallest boost inductor and simple boost diode

- · Low switching loss

- PF enhancement compensates for EMI filter and bridge rectifier distortion

- Operates with distorted input voltage signature of UPS or generators

- <40 mW no-load consumption at 230 VAC</li>

- Integrated automatic X capacitor discharge

- 750 V PowiGaN™ switch

- High power factor at 305 VAC with 80% derating

- Easily withstands 460 VAC line swells

- · Highly integrated, compact footprint

- · Self-bias for high-voltage start-up

- · Source-potential cooling reduces EMI

- · Programmable Power Good (PG) signal for active inrush control

- · Selectable power limit enables rapid prototyping

- Safety certified to IEC62368

#### **Applications**

- PC

- PrinterLCD TV

- Video game consoles

- 80 Plus™ Platinum

- High-power adaptors and USB PD 3.1 rapid charging

- High-power LED lighting

- · Industrial and appliance

- · Generic PFC converters

#### **Description**

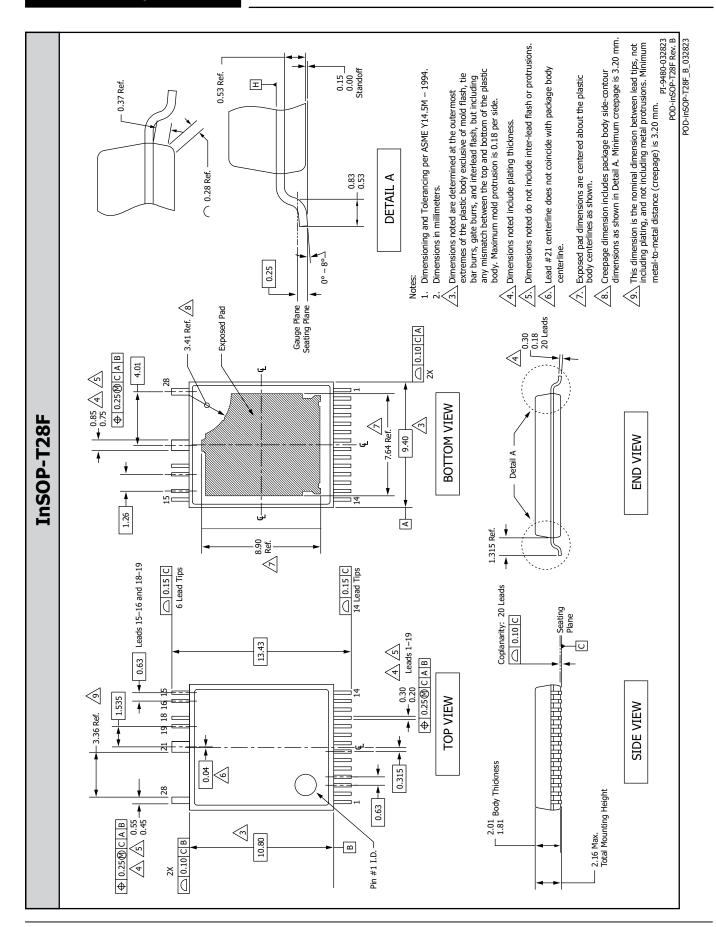

The HiperPFS<sup>™</sup>-5 family of advanced power factor correction ICs leverages the low switching losses of the 750 V PowiGaN switch to optimize efficiency. High integration and advanced control minimizes system footprint by reducing component count and inductor size. Mounted in the low profile, surface mount InSOP-T28F package, HiperPFS-5 ICs pass heat directly to the PCB, eliminating the need for bulky heat sinks.

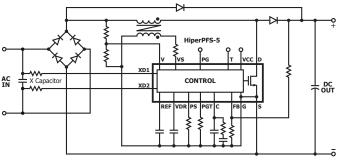

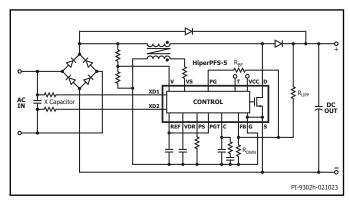

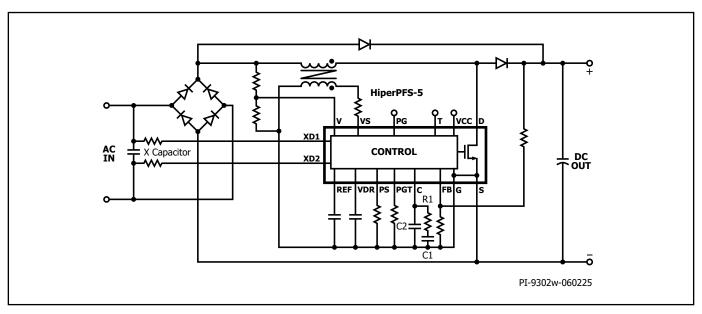

Figure 1. Typical Application Circuit.

PI-9302g-013023

#### **Output Power Table**

#### **Maximum Continuous Output Power at 90 VAC**

|                        | •                        |

|------------------------|--------------------------|

| Product <sup>1,2</sup> | Self Biased              |

| PFS5173F               | 77 W                     |

| PFS5174F               | 115 W                    |

| PFS5175F               | 130 W                    |

| PFS5176F               | 165 W                    |

| PFS5177F               | 185 W                    |

| PFS5178F               | 250 W                    |

| Product <sup>1,2</sup> | Non Self-Biased (USB PD) |

| PFS5274F               | 115 W                    |

| PFS5275F               | 130 W                    |

| PFS5276F               | 165 W                    |

| PFS5277F               | 185 W                    |

| PFS5278F               | 250 W                    |

|                        |                          |

Table 1. Output Power Table.

#### Notes:

- Maximum output power is dependent on the design. With condition that package temperature < 125 °C.</li>

- Package: InSOP-T28F.

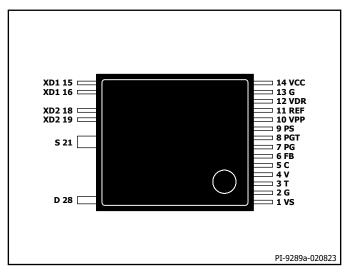

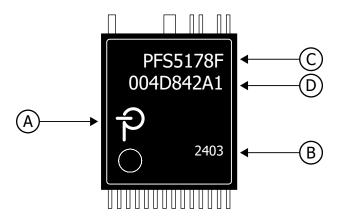

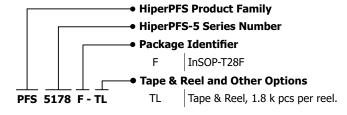

Figure 2. InSOP-T28F Package.

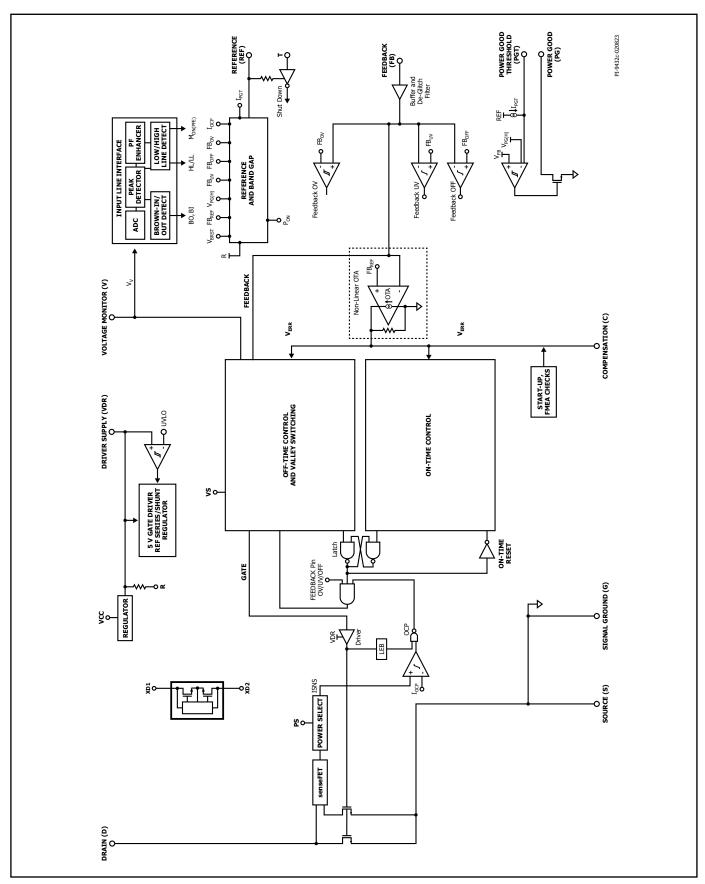

Figure 3. Functional Block Diagram.

#### **Pin Functional Description**

#### **VALLEY SENSING (VS) Pin (Pin 1)**

This pin is used to sense voltage on the auxiliary winding of the PFC inductor. The VS pin is connected to the auxiliary winding on a PFC inductor through an external resistor. The voltage on the auxiliary winding on a PFC inductor provides the controller information about the drain voltage. The external resistor is used to limit the current through VS pin and for fine adjustment of timing for valley switching.

#### SIGNAL GROUND (G) Pin (Pin 2, 13)

Discrete components used in the feedback circuit, including loop compensation, decoupling capacitors for the BIAS POWER (VCC), REFERENCE (REF) and VOLTAGE MONITOR (V) must be referenced to the SIGNAL GROUND (G) pin. The SIGNAL GROUND pin is also connected to the exposed pad of the device. The SIGNAL GROUND pin should not be tied directly to the SOURCE pin external to the IC.

#### T Pin (Pin 3)

This pin is used to shut down the HiperPFS-5 IC when it is pulled down (to SIGNAL GROUND potential). This can be used to turn off the PFC stage which improves overall system efficiency at light load. When an external bias is not applied, an internal resistor pulls the T pin up (to REF pin voltage). The T pin can be left floating during normal circuit operation, however, an external pull-up resistor (e.g.  $50~\text{k}\Omega$ , the value depends on the type of transistor used to pull down the T pin) from the VDR pin is recommended when the shut down mode is used for this device.

#### **VOLTAGE MONITOR (V) Pin (Pin 4)**

The VOLTAGE MONITOR pin is tied to the rectified high-voltage DC rail through a 100:1, 1% high-impedance resistor divider to minimize power consumption in standby. The recommended resistance value is between 8 M $\Omega$  and 16 M $\Omega$ . Changing this divider ratio affects the input current waveform, reduces power factor and increases THD. A small ceramic capacitor forming an 80  $\mu s$  time constant must be connected between the VOLTAGE MONITOR pin and the SIGNAL GROUND pin to bypass any switching noise present on the rectified DC bus. This pin also features brown-in/out detection thresholds and incorporates a weak current source that acts as a pull-down in the event of an open-circuit condition.

#### **COMPENSATION (C) Pin (Pin 5)**

This pin is used for loop pole/zero compensation of the OTA error amplifier via a network of capacitors and a resistor between the COMPENSATION pin and SIGNAL GROUND pin.

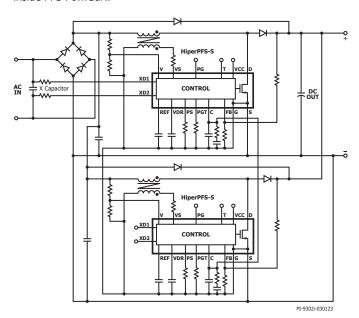

Two or more PFC stages can be connected together via the C pin (and the outputs) to enable parallel operation. The trace connecting the C pins together should be routed to avoid noise pickup, as this is a high impedance node. (See Figure 4)

#### FEEDBACK (FB) Pin (Pin 6)

This pin is connected to the main voltage regulation feedback resistor divider network and is also used for fast over and undervoltage protection. This pin also detects the presence of the feedback voltage divider network at start-up. The divider ratio should be the 400/3.85 to ensure that nominal PFC output voltage is 400 V. Positioning a large upper resistor between 8 M $\Omega$  and 16 M $\Omega$  ±1% is recommended. A small ceramic capacitor between FEEDBACK and SIGNAL GROUND, forming a 80  $\mu s$  time-constant with the bottom resistor, is required.

#### POWER GOOD (PG) Pin (Pin 7)

Use of the PG function is optional for PFS517xF. The POWER GOOD pin is an active low, open-drain connection which sinks current when the output voltage is in regulation. At start-up, once the FEEDBACK pin voltage has risen to  $\sim\!\!95\%$  of the internal reference voltage, the POWER GOOD pin is asserted low. After start-up, the output voltage threshold at which the PG signal becomes high-impedance and depends on the threshold programmed by the POWER GOOD THRESHOLD pin resistor. When not used, the POWER GOOD pin should be left floating.

For PFS527xF this pin is used to implement the boost follower feature. This is an active low, open-drain connection which sinks current when the peak detected input voltage is determined to be high-line. Connect an additional feedback resistor  $R_{\rm BF}$  between PG pin and the FB pin to change the output voltage between low-line and high-line inputs. This feature improves efficiency particularly at low-line AC input.

#### **POWER GOOD THRESHOLD (PGT) Pin (Pin 8)**

This pin is used to program the output voltage threshold at which the PG signal becomes high-impedance representing the PFC stage falling out of regulation. The low threshold for the PG signal is programmed with a resistor between the POWER GOOD THRESHOLD and SIGNAL GROUND pins. Tying the POWER GOOD THRESHOLD to the REFERENCE pin disables the power good function (i.e. POWER GOOD pin remains high impedance). In boost follower mode, the PGT pin has no function and should be connected to REFERENCE pin.

#### **POWER SELECTION (PS) Pin (Pin 9)**

This pin is used to program the output power of the HiperPFS-5. The power is programmed with a resistor connected to the SIGNAL GROUND pin. The power is programmed in 10% steps, between 70% to 100% of nominal power.

#### VPP Pin (Pin 10)

Should be connected to REF pin or left open.

#### **REFERENCE (REF) Pin (Pin 11)**

This pin is connected to an external bypass capacitor. The voltage on this pin is nominally 5 V and is used to supply the control circuitry inside PFS PowiGaN.

Figure 4. Compensation Pin Connection for Parallel Operation.

#### **DRIVER VCC DECOUPLING (VDR) Pin (Pin 12)**

This pin is connected to an external bypass capacitor. There is an internal linear regulator which supplies the VDR pin with a regulated voltage of (5.25 V nominally). This voltage is used to supply the driver section of the PFS PowiGaN controller.

#### **BIAS POWER (VCC) Pin (Pin 14)**

This is the input for the 7-35 VDC bias supply used to power the IC. The maximum operating voltage must be externally clamped to prevent the BIAS POWER pin from exceeding 35 VDC.

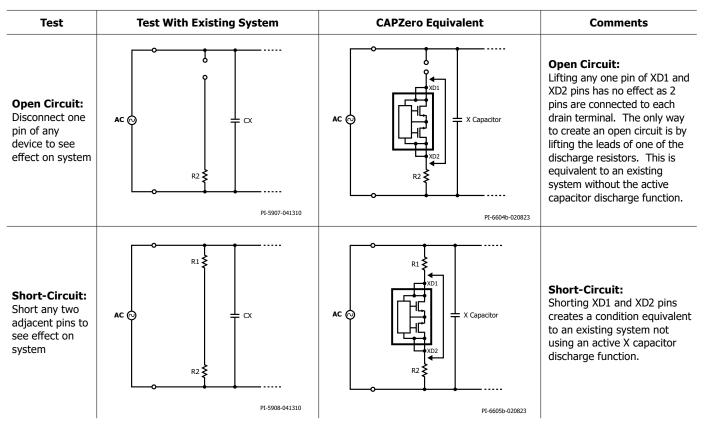

#### X CAPACITOR DISCHARGE TERMINAL XD1 (Pin 15-16)

Connected together internally to one terminal of the X capacitor. These two pins are connected together with a bond wire inside package. For selection of the discharge resistors follow the recommendations in CAPZero-2 data sheet.

#### X CAPACITOR DISCHARGE TERMINAL XD2 (Pin 18-19)

Connect one pair of pins via a series resistor to each side of the X capacitor. These two pins are connected together internally with a bond wire inside package. To select the values for the discharge resistors follow the recommendations in the CAPZero-2 data sheet.

#### SOURCE (S) Pin (Pin 21)

This pin is the source connection for the power switch as well as the negative bulk capacitor terminal connection.

#### DRAIN (D) Pin (Pin 28)

This is the drain connection for the internal power switch.

#### **SOURCE (S) Exposed Pad**

The exposed pad is the source connection for the power switch as well as the negative bulk capacitor terminal connection. It also provides a thermal path for cooling of the power switch.

Figure 5. Pin Configuration.

#### **Functional Description**

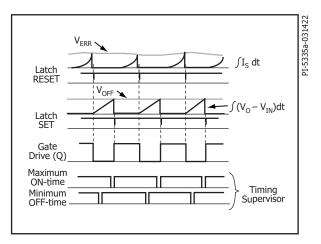

The HiperPFS-5 family are variable switching frequency boost PFC devices. It employs a constant amp-second on-time and constant volt-second off-time control algorithm. This algorithm is used to regulate the output voltage and shape the input current to comply with regulatory harmonic current limits and (high power factor). Integrating the switch current and controlling it to have a constant amp-second product over the on-time of the switch allows the average input current to follow the input voltage. Integrating the difference between the output and input voltage maintains a constant volt-second balance dictated by the boost inductance, regulated output voltage and power. The controller sets the amount of charge delivered during each on-cycle. The charge per cycle is altered gradually over many switching cycles in response to load changes and can be considered constant across a given half line cycle. With this constant charge (or amp-second) control:

$$I_{IN} \times t_{ON} = K_2 \tag{1}$$

The control technique also sets constant volt-second for the off-time ( $t_{\text{OFF}}$ ). The off-time is controlled such that:

$$(V_O - V_{IN}) \times t_{OFF} = K_1 \tag{2}$$

Since the volt-seconds during the on-time must equal the volt-second during the off-time, (to maintain flux equilibrium in the PFC choke), the on-time  $(t_{\text{ON}})$  is controlled such that:

$$V_{IN} \times t_{ON} = K_1 \tag{3}$$

Substituting  $t_{ON}$  from (3) into (1) gives:

$$I_{IN} = V_{IN} \times K_2 / K_1 \tag{4}$$

The relationship of (4) demonstrates that by controlling a constant amp-second on-time and constant volt-second off-time, the input current  $I_{\scriptscriptstyle IN}$  is proportional to the input voltage  $V_{\scriptscriptstyle IN}$ , satisfying the fundamental requirement for power factor correction.

At the end of volt-second integration for the off-time, the control engine waits for the valley of the Drain voltage, and turns on the PowiGaN at the minimum. In order to compensate for this delay, the HiperPFS-5 IC also measures the difference between desired OFF-time (controlled by volt-second integration) and actual OFF-time (synchronized with Drain voltage valley). The control engine then adjusts the next On-time period to account for this difference. This valley-correction ensures the same average current in each switching cycle.

This control produces a discontinuous mode power-switch current waveform (during normal operation) that varies both in frequency and peak current value across a line half-cycle to produce an input current proportional to the input voltage.

#### **Control Engine**

The controller features a low bandwidth, high gain OTA error-amplifier of the non-inverting terminal of which is connected to an internal voltage reference of 3.85 V. The inverting terminal of the error-amplifier is fed from the external FEEDBACK pin which connects to the output voltage divider network with a divider ratio of 3.85:400 to regulate the output voltage to 400 V (nominal). The FEEDBACK pin connects directly to the divider network to ensure fast transient load response.

The difference between the input and output voltage is derived internally, and the result is scaled, integrated, and compared to a voltage reference ( $V_{\text{OFF}}$ ) to determine the point of off-time termination. The controller delays this request and terminates the off-time at a point to coincide with the nearest valley of the ring on the drain voltage.

The internally sensed FET switch current is scaled by the input-voltage peak detector current-sense gain ( $M_{\mbox{\scriptsize oN}}$ ) then integrated and compared with the error-amplifier signal ( $V_{\mbox{\tiny ERR}}$ ) to determine the on-time termination point. The valley correction block adjusts this to compensate for the delay imposed by the valley switching adjustment in the off-time.

Line Feed-Forward Scaling Factor ( $M_{oN}$ ) and PF Enhancer The VOLTAGE MONITOR (V) pin voltage is sampled and converted by a  $\Delta$ - $\Sigma$  ADC to a quantized digital value. A digital line-cycle peak detector, with dynamic time constants and multi-cycle filtering, derives and averages the peak of the input line voltage. This peak is used internally to scale the gain of the current sense signal through the  $M_{ON}$  variable. This contribution is required to reduce the dynamic range of the control feedback signal as well as flatten the loop gain over the operating input line voltage. The line-sense feed-forward gain adjustment is proportional to the square of the peak rectified AC line voltage and is adjusted as a function of the VOLTAGE MONITOR pin voltage.

At high-line, the feed-forward  $\rm M_{\rm oN}$  variable is dynamically adjusted across the line cycle in order to compensate for the line current distortion caused by the EMI filter and full bridge network, and improve power factor.

The line-sense feed-forward gain is also important in providing a switch power limit over the input line range.

Beyond the specified maximum power rating of the device, the internal power limit will regulate the output voltage below the set regulation threshold as a function of output overload to maintain constant output power.

Figure 6. Idealized Converter Waveforms.

#### **Valley Synchronization**

In a normal operation, the PowiGaN switch is turned-on at the valley of the drain voltage of the PowiGaN power switch. The Valley Synchronisation Block ensures turn-on in the valley to minimize turn-on losses.

The voltage measured across the auxiliary (sense) winding of the PFC inductor is connected to the VALLEY SENSING (VS) pin through an external resistor. This voltage of auxiliary (sense) winding of the PFC inductor represents the difference between of the voltage on the drain of the PowiGaN switch and the rectified voltage. The valleys of this voltage coincide with valleys of the voltage on the drain of the PowiGaN switch.

In certain cases, where valley switching is not possible, such as during operation in CCM, or when the amplitude of oscillations of the drain voltage becomes too small, the controller enables the No Valley Switching (NVS) mode. In this condition, the controller does not wait for the valley to appear. When the volt-second integration circuit requests a turn-on, it immediately turns on the PowiGaN switch.

#### **Valley Correction**

Valley correction reduces the input current distortion coming from the valley switching operation in discontinuous mode (DCM) and critical mode (CrM). Valley correction is enabled in DCM and CrM operation when more than one valley is detected.

In a DCM PFC converter with valley switching, the PowiGaN switch can be turned on only at the V $_{DS}$  valley instants. The relaxation frequency of the V $_{DS}$  voltage ring is  $\leq 1$  MHz, which means that the time between two valleys are more than 1  $\mu s$  apart. There is a delay between the instant when the OFF controller requests the turn-on and the point when the PowiGaN power switch is actually turned on.

This delay changes the average input current from what was originally requested by the controller, and the input current becomes distorted. The deviation in average cycle current from the desired current is proportional to this delay. In such cases, the switching period instantly changes by a significant value (could be in the range of  $1~\mu s$ ) and distortion of the input current is the most pronounced.

## **Controller Supplying Circuitry**

#### **Parts Without Self-Supply Circuit**

Parts without the self-supply circuit are supplied only through the BIAS POWER (VCC) pin. Inside the IC there is a linear regulator between the VCC pin and the VDR pin. This linear regulator regulates the voltage on the VDR pin to 5.25 V.

The voltage on the VDR pin is used to supply the internal controller. A decoupling capacitor is connected to the VDR pin to provide a low high-frequency impedance path to ground.

#### Parts With the Self-Supply Circuit

Parts with the self-supply feature generate the internal supply voltage for the control circuitry. The converter operates with the control circuitry being supplied through the internal PowiGaN until the voltage on the VCC pin form the external bias circuit is established.

Once the voltage on the VCC pin appears, and is greater than the minimum voltage needed to operate the internal linear regulator (VCC > 7 V), the internal linear regulator will start supplying the control circuitry and disable the self-supply circuit.

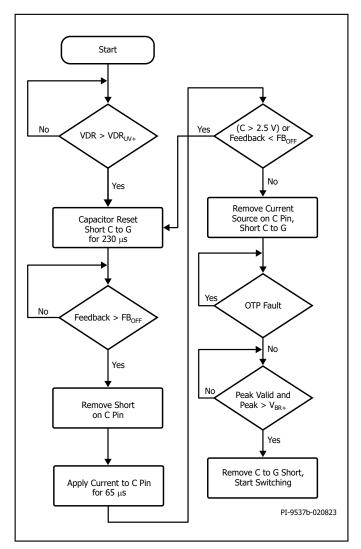

#### **Start-Up With Pin-to-Pin Short-Circuit Protection**

At start-up and prior to the commencement of switching, the engine performs a sequence of operational pin short/open checks, as shown in Figure 7. If no faults are detected, when the input voltage peak is above the brown-in threshold, the engine enables switching.

The OTA error amplifier provides a non-linear amplifier (NLA) mechanism to overcome the inherently slow feedback loop response when the sensed output voltage on the FEEDBACK pin is outside its regulation window. This allows the error amplifier function to limit the maximum overshoot and undershoot during load transient events.

To reduce switch and output diode current stress at start-up, the HiperPFS-5 calculates the off-time based on the output voltage ( $V_o$ ) during start-up, resulting in a soft controlled start-up.

Additionally, the Over-Current Protection (OCP) threshold is ramped up from 60% to 100% of its nominal value. This reduces flux swing in the PFC inductor if the control loop requires larger duty cycle.

At power-up, the controller first determines whether the appropriate supply voltage is applied by checking that the voltage on the VDR pin is greater than the VDR  $_{\text{VDR}(UV+)}$  threshold. Once the voltage on the VDR pin is above the  $V_{\text{VDR}(UV+)}$  threshold, pin open/short tests are performed, and if the FEEDBACK pin voltage is valid, the overtemperature status is confirmed to be false.

Once these checks are confirmed, the input voltage is monitored via the VOLTAGE MONITOR pin until it exceeds the  $V_{BR+}$  threshold (but the peak detector is not saturated). This is the point at which the value of the resistor on the POWER SELECTION (PS) pin is determined and the maximum output power is set. After the maximum power is determined the switching is enabled.

Figure 7. Start-Up Flow Chart.

#### **Timing Supervisor and Operating Frequency Range**

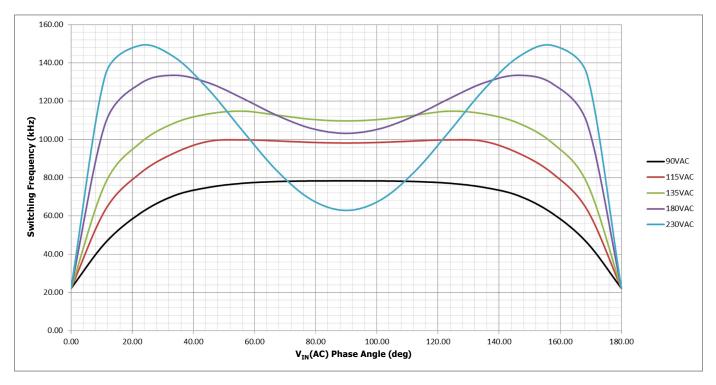

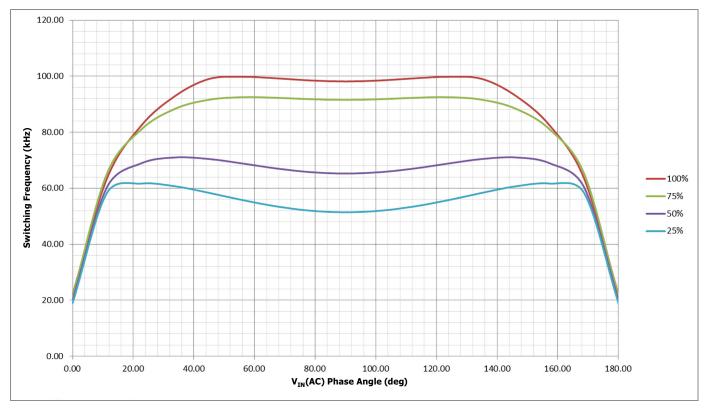

The controller operates with a variable switching frequency over the line frequency half-cycle, typically spanning a range of 22 – 145 kHz. The controller also features a timing supervisor function which

monitors and limits the maximum switch on-time and off-time as well and ensures minimum cycle on-time. Figure 8 shows the typical half-line frequency profile of the device switching frequency as a function of input voltage at maximum load.

Figure 8. Frequency Variation Over Line Half-Cycle as a Function of Input Voltage.

Figure 9. Frequency Variation Over Line Half-Cycle as a Function of load ( $V_{IN} = 115$  VAC).

# EcoSmart (Frequency Sliding and Spread-Spectrum Switching)

The HiperPFS-5 IC's include an EcoSmart function whereby the internal error signal ( $V_{\text{ERR}}$ ) is used to detect the converter output power. This is used to set the average switching frequency as a function of output power.

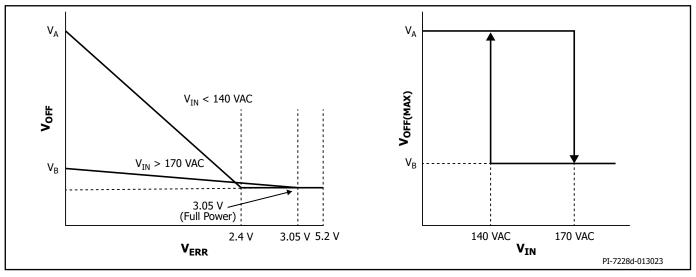

As shown in the Figure 10 below, the off-time integrator control reference ( $V_{\rm OFF}$ ) is set by the internal error-voltage level (output

power) to allow the converter to maintain output voltage regulation and flat conversion efficiency from 20% to 100% of rated load, which is essential to meet many efficiency directives. The degree of frequency slide is also controlled which is a function of input line voltage. The lower  $V_{\rm OFF}$  slope as a function of input voltage reduces the average frequency range for high input line operation. Using this approach, the HiperPFS-5 IC enables the use of a smaller PFC inductor, while still keeping the switching frequency below 150 kHz across line and load to minimize the burden on EMI components.

Figure 10. EcoSmart Frequency Sliding  $V_{\text{OFF}}$  vs.  $V_{\text{ERR}}$  and  $V_{\text{OFF(MAX)}}$  vs. Input Voltage.

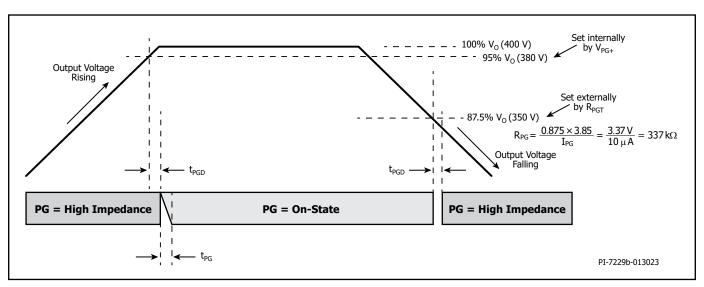

#### **Power Good Signal For PFS517xF**

The HiperPFS-5 features a power good (PG) circuit which comprises an internal comparator that turns an open-drain switch on during start-up when the sensed output voltage on the FEEDBACK pin rises to  ${\sim}95\%$  (V  $_{\rm PG+}$ ) of the output voltage threshold. During start-up, prior to the output voltage reaching V  $_{\rm PG+}$  the PG signal is in a high-impedance state (internal switch is in off-state).

The power good signal transitions from on to off-state when the sensed output voltage on the FEEDBACK pin falls to a user selected threshold, programmed via resistor on the POWER GOOD THRESHOLD (PGT) pin. The POWER GOOD THRESHOLD pin sources a fixed current  $I_{\text{PG(T)}}.$  This current in combination with the power good threshold resistor sets the threshold at which the power good signal transitions from the on-state to the high-impedance off-state as the PFC output falls out of regulation.

The power good comparator has an internal 81  $\mu s$  de-glitch filter  $(t_{_{PGD}})$  to prevent noise events from falsely triggering the programmed VPG-threshold.

In the event a load fault prevents the boost from achieving regulation (above  ${\sim}95\%$  of the set output voltage threshold) the PG function will remain in the high-impedance state and so will not indicate when an output voltage has fallen below the user programmed  $V_{\text{PG-}}$  threshold. The  $V_{\text{PG-}}$  user programmed threshold is only enabled once the  $V_{\text{PG+}}$  threshold has been reached.

If the POWER GOOD THRESHOLD programming pin is tied to REFERENCE pin, the power good function is disabled and PG remains in the high-impedance (off) state. This is the preferred configuration when PG is not used. If the POWER GOOD THRESHOLD pin is shorted to the SIGNAL GROUND pin, the PG signal will transition to the on-state at  $V_{\rm PG+}$  and remain low (on) until the PFC output voltage has fallen below the  $V_{\rm FB(UV)}$  threshold for greater than  $t_{\rm FB(UV)}$  seconds.

Similar to the disable condition described above, if the value of the PGT resistor is such that the  $V_{\text{pG-}}$  threshold is greater than the  $V_{\text{pG-}}$  threshold, the PG signal will latch off and remain in the high-impedance off-state.

The Power Good function is not valid under the following conditions:

- A. VCC or VDR are not in a valid range of operation. VCC below UVLO- or VDR below  $V_{\text{VDR}(UV-)}$  the power good function is not valid with the POWER GOOD pin in a high-impedance state.

- B. POWER GOOD pin will go to high-impedance state when a soft shutdown is initiated by an over-temperature fault to provide early indication to secondary circuits of an OT (over-temperature) fault.

- C. PGT is outside the valid programming range of between 225 V and 360 V. PGT voltages above this range, including PGT floating, will prevent PG from transitioning to active pull-down. PGT voltages below this range result in PG de-assertion at the output undervoltage ( $V_{\text{FB(UV)}}$ ) threshold.

- D. Once the start-up sequence check has passed and the converter goes into start-up, if PGT is opened, then the PG signal will remain latched in the high-impedance state until the controller is reset.

Figure 11. Power Good Function Description.

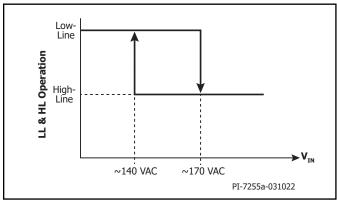

#### **Boost-Follower For PFS527xF**

The HiperPFS-5 IC's feature a Boost Follower (BF) circuit which controls the output voltage as a function of input voltage. This feature improves efficiency at low-line by reducing the target output voltage. When the input peak voltage indicates low-line, the PG/BF pin is in a high impedance state (internal switch is in off-state). When the input peak voltage is sensed to be in high-line, the PG/BF pin is turned on (low impedance state) (internal switch is switched to ground). The low-line and high-line hysteresis is set at 140 VAC and 170 VAC.

As shown in Figure 13, at high-line input, the output voltage is equal to:

$$V_{\text{O}} = V_{\text{FB}} \times \left( \frac{R_{\text{UPP}} + R_{\text{BF}} / / R_{\text{DWN}}}{R_{\text{BF}} / / R_{\text{DWN}}} \right)$$

and at low-line input, the output voltage is equal to:

$$V_{\text{o}} = V_{\text{\tiny FB}} \! \times \! \left( \frac{R_{\text{\tiny UPP}} + R_{\text{\tiny DWN}}}{R_{\text{\tiny DWN}}} \right)$$

Figure 12. Boost Follower Low-Line and High-Line operation vs. Input Voltage.

Figure 13. System Schematic with a Line Dependent V<sub>OUT</sub> (Boost Follower).

#### **Selectable Power Limit**

The PS (Power Selection) pin is used to program the output power of the HiperPFS-5. The power is programmed with a resistor connected to the G pin, in 10% steps, between 70% to 100% of the nominal output power.

#### **Turns Ratio For Auxiliary Winding**

The VS pin is connected to the auxiliary winding of the PFC inductor through a resistor to detect the valley switching. This resistor can adjust the proper delay for a given application so that the turn-on of the PowiGaN happens at the valley of the voltage on the DRAIN pin. The delay depends on the resistance of this resistor and the effective capacitance on the VS pin. If the resistor is closer to the VS pin, the effective capacitance on the VS pin is smaller with a shorter delay.

Oppositely, if the resistor is put far from the VS pin, then the effective capacitance on the VS pin is larger with a longer delay. The initial design recommended value for the resistor is 10 k $\Omega$  and put this resistor close to VS pin.

The maximum turns ratio (N<sub>MAX</sub>) of auxiliary winding is calculated as N<sub>MAX</sub> = (V<sub>OMIN</sub> – V<sub>ACPEAK</sub>)/ V<sub>VS1</sub>. Here, the V<sub>OMIN</sub> is minimum output voltage considering the ripple tolerance. If V<sub>O</sub> = 400 V and assuming 3% tolerance, the V<sub>OMIN</sub> is 388 V; V<sub>ACPEAK</sub> is the peak voltage of maximum high-line input. For universal AC input, V<sub>ACPEAK</sub> =  $\sqrt{2}$  × 265  $\approx$  375 V; V<sub>VS1</sub> is the valley sensing positive threshold with typical value 0.88 V. From the above equation, it can calculate the maximum turn ratio (N<sub>MAX</sub>) is about 15. The recommended turns ratio for auxiliary winding is ranged from 10 to 15.

| Resistor (Ohms) | Power Selection | Comments                                     |

|-----------------|-----------------|----------------------------------------------|

| >400 k          | 100%            | Leaving pin open is acceptable               |

| 100 k – 200 k   | 90%             |                                              |

| 25 k – 50 k     | 80%             |                                              |

| <6 k            | 70%             | Connecting pin short to G node is acceptable |

Table 2. Power Programming Resistances (Resistor Between PS Pin and G Pin).

#### **Protection Modes**

#### **Brown-In Protection**

The VOLTAGE MONITOR pin has an input line undervoltage detection feature to limit the minimum start-up voltage. This detection threshold will inhibit the device from starting at input voltages below brown-in point and above input peak voltages of 400  $V_{\rm pg}$ .

#### **Brown-Out Protection**

The VOLTAGE MONITOR pin features a brown-out protection mode whereby the HiperPFS-5 will turn-off when the VOLTAGE MONITOR pin voltage is below the line undervoltage threshold (VBR-) for a period exceeding  $t_{\text{BROWN-OUT}}$  (brown-out debounce period). In the event that a single half-line cycle is missing (normal operating line frequency is in the range of 47 Hz to 63 Hz) the brown-out protection feature will not be activated.

Once brown-out has been triggered, the HiperPFS-5 IC's soft-shutdown gradually reduces the internal error-voltage to zero over a period of 1 ms which ramps the power PowiGaN on-time to zero. The onset of this soft-shutdown is aligned to the next line cycle zero crossing to minimize reactive component di/dt transients and allow time for the energy stored within the boost choke as well as the input EMI filter to dissipate. This helps minimize voltage transients after the bridge rectifier and prevent false restarts.

The device will enter an auto-restart, including FMEA pin fault checks and other start-up qualifications prior to checking that the line voltage is above the brown-in threshold (VOLTAGE MONITOR pin voltage above  $V_{\text{RR+}}$ ).

After a brown-in event, and once the  $t_{\text{START-UP}}$  timer expires, the line voltage brown-out threshold is reduced to  $V_{\text{BR(NTC)}}$  and the brown-out timer is extended to  $t_{\text{BROWN-OUT(NTC)}}$  to allow for the drop in line voltage caused by the voltage drop across the in-rush limiting negative temperature coefficient (NTC) thermistor in series with the input line.

If the  $t_{BROWN-OUT(NTC)}$  debounce timer is triggered by the sensed line voltage dropping below the  $V_{BR(NTC)}$  threshold but the line voltage recovers to above the  $V_{BR(NTC)}$  threshold before the  $t_{BROWN-OUT(NTC)}$

expires, then the  $t_{\text{START-UP}}$  timer will be re-started. If the line does not recover above the  $V_{\text{BR(NTC)}}$  threshold before the  $t_{\text{BROWN-OUT(NTC)}}$  debounce timer expires a shutdown will occur.

After the  $t_{\text{STARTUP}}$  timer has expired, if the VOLTAGE MONITOR pin voltage rises above  $V_{\text{BR-NTC'}}$ , the brown-out debounce timer will switch to normal period  $(t_{\text{BRWN\_OUT}})$  and the brown-out threshold will switch to  $V_{\text{BR}}$ . If the VOLTAGE MONITOR pin voltage is not above  $V_{\text{BR}}$  after the subsequent  $t_{\text{BRWN\_OUT}}$  timer has expired then a brown-out shutdown will occur.

HiperPFS-5 IC's incorporates input waveform discrimination to determine if the line signal peak-to-average voltage ratio is representative of a sine wave or a high-duty-cycle square wave. The brown-out threshold is reduced to  $V_{\text{BR(SQ)}}$  when a high duty cycle (UPS) square wave is detected.

#### VCC Undervoltage Protection (UVLO) for PFS527x Parts

The BIAS POWER (VCC) pin has an undervoltage lock-out protection which inhibits the IC from starting unless the applied VCC voltage is above the VCC<sub>IMO+</sub> threshold.

The IC initiates a start-up once the BIAS POWER pin voltage exceeds the VCC $_{\rm UVLO+}$  threshold. After start-up the IC will continue to operate until the BIAS POWER pin voltage has fallen below the VCC $_{\rm UVLO-}$  level.

PFS517x parts are using VDR for UVLO protection.

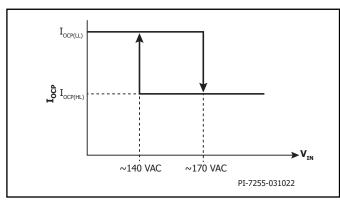

#### **Line Dependent Over-Current Protection (OCP)**

The device includes a cycle-by-cycle over-current protection mechanism which protects the device in the event of a fault. The OCP circuit protects the internal power switch. This intends to protect the converter from output short-circuit or overload fault conditions.

The OCP limit is set as a function of the input line voltage. This helps to restrict power limit due to short-circuits as well as minimize the stress on the switch due to current overloads at higher input line conditions.

Figure 14 below illustrates the hysteretic adjustment of the OCP levels as a function of VOLTAGE MONITOR pin line sense.

The low-line OCP (the greater of the two settings) is selected when the peak of the input line voltage drops below 140 VAC for 3 less consecutive half-cycles and the high-line OCP level (the less of the two settings)is selected when the input line voltage rises above 170 VAC for 1 half-cycle, (except in follower mode, as described in the subsequent sections).

The HiperPFS-5 IC implements a high input line OCP after detecting the VOLTAGE MONITOR pin voltage being above the high-line threshold,  $V_{_{\text{V(HIGH+)}}}$ . The controller reverts back to low-line OCP (as well as low-line frequency slide) only after 3 consecutive half-line cycle peak values that are below the low-line threshold  $V_{_{\text{V(HIGH+)}}}$ . In the event of a line drop-out, the controller may revert from high-line to low-line set-points if the drop-out exceeds 37 ms (nominal).

A feed-forward feature updates the controller to high-line status rapidly, as soon as the input voltage exceeds  $V_{\mbox{\tiny HIGH+}}$ . This feature has particular benefit for high-line hard-start conditions after a long AC line drop-out where the peak detector may initially indicate a low input line condition.

Figure 14. Line Dependent OCP.

#### Safe Operating (SOA) mode

Since the cycle-by-cycle OCP mechanism described above does not prevent the possibility of inductor current 'stair-casing', and an SOA mode is also featured.

Rapid build-up of the switch current can occur in the event of inductor saturation or when the input and output voltage differential is small resulting in too little inductor reset time.

The SOA mode is triggered whenever the switch current reaches current limit ( $I_{\text{OCP}}$ ) and the on-time is less than  $t_{\text{ON(SOA)}}$ . The SOA mode forces an off-time equal to  $t_{\text{OFF(SOA)}}$  and pulls the internal error-voltage ( $V_{\text{ERR}}$ ) down by 1/2 of its maximum value in order to ensure the switch remains within its SOA.

#### **Fast Output Voltage Overvoltage Protection**

The HiperPFS-5 features a voltage feedback threshold comparator on the FEEDBACK pin which detects an output overvoltage condition to allow rapid response, (independent of the COMPENSATION pin response), to prevent hazardous voltage conditions from occurring. The overvoltage protection is hysteretic – the voltage on the FEEDBACK pin must drop by 0.1 V (equating to an output voltage drop of 10 V) before switching is re-started.

#### **FEEDBACK to COMPENSATION Pin Short Detection Safeguard**

The PFC controller continuously monitors the FEEDBACK and COMPENSATION pins to ensure that there are no potential short conditions between the adjacent FEEDBACK and COMPENSATION pins, which could result in output overvoltage conditions. In the event a potential short is detected, a rapid short check is performed and a shutdown is executed in the event that a suspected short is validated.

#### **Open FEEDBACK Pin Protection**

The FEEDBACK pin continuously sinks a static current of  $I_{\text{FBPD}}$  ([VCC >VCC $_{\text{UVLO}+}$ ]) to protect against a fault related to an open FEEDBACK pin or invalid feedback divider network. The internal current sink introduces a small static offset to the output regulation which can be accounted for in selecting the output feedback regulation components (FEEDBACK pin divider).

#### **Hysteretic Thermal Protection**

The thermal shutdown circuit senses the controller die temperature which is well coupled to the power switch through the exposed, source pad and PCB copper cooling plane. The OTP (over-temperature protection) threshold is set at 130 °C typical with 49 °C hysteresis.

When the controller die temperature rises above this threshold (OTP), the controller initiates a soft-shutdown and remains disabled until the controller die temperature falls by  $\sim$ 49 °C, at which point the device will re-initiate the start-up sequence.

## **Safety of X Capacitor Discharge**

X capacitor discharge function can be implemented by connecting XD1 to one AC line input through an external series resistor and XD2 to the other AC input line input through a separate external resistor.

X capacitor discharge function meets safety requirements even if connection is placed before the system input fuse. If a short-circuit is placed between XD1 and XD2 terminals, the system is identical to existing systems where X capacitor discharge function is not used.

With regard to open circuit tests, it is not possible to create a fault condition through a single pin fault (for example lifted pin test) since

there are two pins connected to both XD1 and XD2. If several pins are lifted to create an open-circuit, the condition is identical to an open circuit X capacitor discharge resistor in existing systems where X capacitor discharge function is not disabled.

| Total X Capacitance | Total Series Resistance |

|---------------------|-------------------------|

| 100 nF to 6 μF      | 7.5 MΩ to 142 kΩ        |

Table 3. X Capacitance and Discharge Resistance.

Table 4. Single Point of Failure (SPOF) Tests as Pertaining to Failure Modes of the X Capacitor Discharge. HiperPFS-5 Device Passes Both Tests.

#### **Application Example 1**

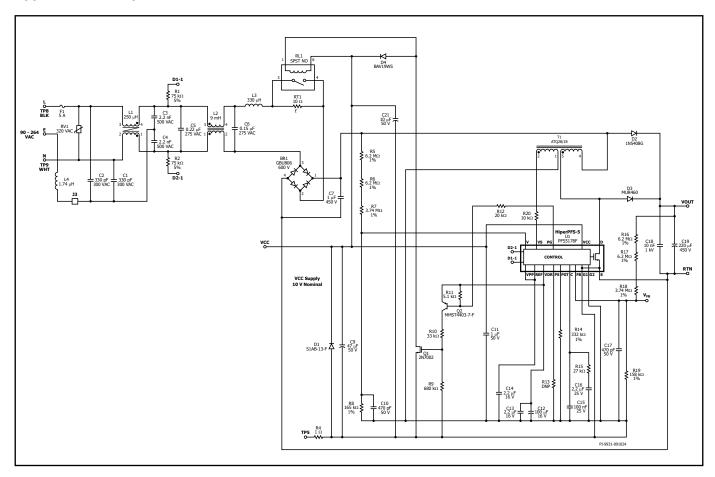

Figure 15. Schematic of a 250 W, 400 VDC Output PFC Circuit using PFS5178F Device.

The circuit shown in Figure 15 is a power factor correction circuit that uses a PFS5178F IC. This design delivers a continuous output power of 250 W with a regulated nominal output voltage of 400 V. It maintains a high input power factor and system efficiency across line and load without the need for external heatsinking.

Fuse F1 provides input over-current protection and isolates the circuit from the AC line in the event of a fault. Metal oxide varistor RV1 protects the circuit during surge events by clamping the input voltage. Diode bridge BR1 rectifies the AC input voltage. Capacitors C1, C2, C3, C4, C5, and C6 and inductors L1, L2, L3, and L4 form the EMI filter. Resistors R1 and R2 are used to discharge the X capacitors via the integrated automatic X capacitor discharge feature of the HiperPFS-5 controller U1. The discharge resistors are connected across the X capacitors only when the AC line is disconnected, eliminating the losses that would occur with conventional circuits.

Thermistor RT1 limits the inrush input current at startup. The electromechanical relay RL1 is used to bypass the thermistor once the output voltage reaches nominal (indicated by the POWER GOOD signal from the PG pin of integrated controller U1). Resistors R9, R10, R11, and R12 along with transistors Q1 and Q2, drive the relay RL1. Diode D4 clamps the voltage when the relay is turned off. Resistor R14 sets the POWER GOOD signal threshold via the PGT pin.

Film capacitor C7 provides input decoupling and charge storage to reduce input current ripple. The boost converter is formed by inductor

T1, boost diode D3, output capacitor C19, and the integrated 750 V PowiGaN switch. The HiperPFS-5 device controls the input current to the power supply and maintains regulation of the output DC voltage. Diode D2 provides an inrush current bypass path when AC line is first applied before PFC operation starts. An auxiliary winding on the inductor T1 is used to sense the voltage difference between the Drain of the PowiGaN switch and the rectified voltage, providing the information necessary for valley switching. Resistor R20 limits the current through the VS pin, providing fine timing adjustment for the valley-switching circuit. Capacitor C18 provides a bypass path to the ground for high frequency switching noise.

Capacitors C9 and C11 provide bypass and filtering for the VCC pin of the HiperPFS-5 controller while diode D1 provides reverse polarity protection. Capacitors C12 and C13 provide bypass and filtering for the internal regulator on the VDR pin used to supply the driver circuitry of the HiperPFS-5 controller. Capacitor C14 provides bypass and filtering for the internal regulator on the REF pin used to supply the control circuitry of the HiperPFS-5 controller.

Resistor R13 sets the maximum continuous output power of the HiperPFS-5 and is left unpopulated for full power operation. Resistors R5, R6, R7, and R8 along with capacitor C10 provide input voltage information to the V pin. Resistors R16, R17, R18, and R19 along with capacitor C17 provide output voltage information to the FB pin. Capacitors C15 and C16 along with resistor R15 shape the loop response of the PFC circuit.

#### **Application Example 2**

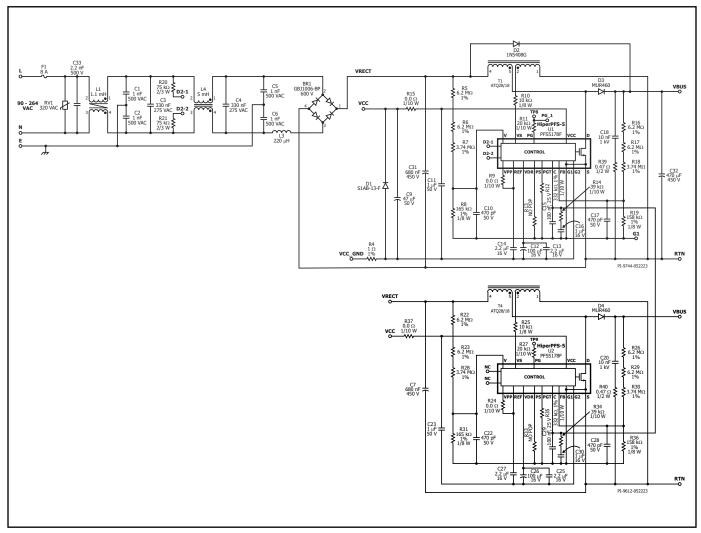

Figure 16. Schematic of a 500 W, 400 VDC Output Parallel PFC Circuit using PFS5178F Devices.

The circuit shown in Figure 16 is a power factor correction circuit using 2 PFS5178F devices in parallel. This design delivers a continuous output power of 500 W with a regulated nominal output voltage of 400 V, maintaining a high input power factor and system efficiency across line voltages and load without external heatsinking.

Fuse F1 provides input over-current protection to the circuit and isolates it from the AC line in the event of a fault. Metal oxide varistor RV1 protects the circuit during surge events by clamping the input voltage. Diode bridge BR1 rectifies the AC input voltage. Capacitors C1, C2, C3, C4, C5, C6, and C33 and inductors L1, L3, and L4 form the EMI filter. Resistors R20 and R21 are used to discharge the X capacitors via the integrated automatic X capacitor discharge feature of the HiperPFS-5 controller U1. The discharge resistors are connected across the X capacitors only when the AC line is disconnected, eliminating the losses that would occur with conventional circuits.

Film capacitors C7 and C31 provide input decoupling and charge storage to reduce input current ripple. Two boost converters are formed by inductors T1 and T2, boost diodes D3 and D4, output capacitor C32, and the integrated 750 V PowiGaN switches. The HiperPFS-5 devices control the input current to the power supply and maintain regulation of the output DC voltage. Diode D2 provides an inrush current bypass

path when AC line is first applied before PFC operation starts. Auxiliary windings on the inductors T1 and T2 are used to sense the voltage difference between the Drain of the PowiGaN switches and the rectified voltage, providing information for valley switching. Resistors R10 and R25 limit the current through the VS pins of the HiperPFS-5 controllers U1 and U2 respectively, providing fine timing adjustment for the valley-switching circuit. Capacitor C18 and C20 along with resistors R39 and R40 provide bypass paths to the ground for high frequency switching noise.

Capacitors C11 and C23 provide bypass and filtering for the VCC pins of the respective HiperPFS-5 controllers while diode D1 provides reverse polarity protection for the VCC pins. Capacitors C12, C13, C25, and C26 provide bypass and filtering for the internal regulators on the VDR pins used to supply the driver circuitry. Capacitors C14 and C27 provide bypass and filtering for the internal regulator on the REF pins used to supply the control circuitry for the respective HiperPFS-5 controllers.

Resistors R13 and R33 set the maximum continuous output power for each of the HiperPFS-5 devices and are left unpopulated for full power operation. Resistors R5, R6, R7, R8, R22, R23, R28, and R31 along with capacitors C10 and C22 provide the rectified input voltage

information to the V pins. Resistors R16, R17, R18, R19, R26, R29, R30, and R36 along with capacitors C17 and C28 provide output voltage information to the FB pins. Capacitors C15, C16, C29, and C30 along with resistors R14 and R34 shape the loop response of each PFC circuit. Resistor R12 and R35 sets the POWER GOOD signal threshold via the PGT pins.

Parallel operation and power sharing are accomplished by connecting the C pins of the U1 and U2 together. The C pin is used to scale the output power of the PFC circuit. By connecting the C pins together, output power information is shared between the two PFC circuits.

## **Recommended Compensation Values**

Figure 17. Typical Application Circuit.

For most designs, to achieve an appropriate phase margin with a gain crossover frequency of < 10 Hz, the recommended compensation values are: R1 = 27 k $\Omega$ , C1 = 2.2  $\mu$ F, C2 = 100 nF. These values were chosen for a 250 W design using an output capacitance of 220  $\mu$ F.

For boost follower configurations, the recommended compensation values are: R1 = 18 k $\Omega$ , C1 = 4.7  $\mu$ F, C2 = 470 nF. These values were chosen for a 250 W design using an output capacitance of 220  $\mu$ F.

Adjusting output capacitance will necessitate changes to compensation values in order achieve the desired gain crossover frequency and phase margin at low input voltages.

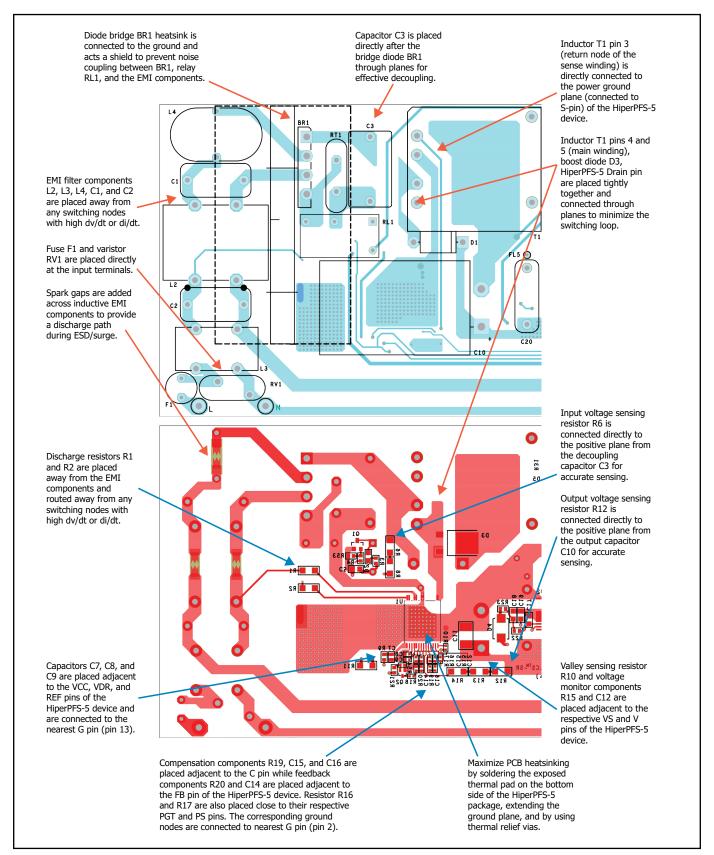

#### **Layout Example**

Figure 18. Typical Application Circuit.

#### **Quick Design Checklist**

As with any power supply design, all HiperPFS-5 family designs should be verified on the bench to make sure that component specifications are not exceeded under worst-case conditions. The following minimum set of tests is strongly recommended:

- 1. Maximum Drain Voltage Verify that peak VDS does not exceed 650 V at lowest input voltage and maximum overload output power. Maximum overload output power occurs when the output is overloaded to a level above the highest rated load and before the power supply output voltage starts falling out of regulation. When measuring Drain-Source voltage of the PowiGaN switch, a high-voltage probe should be used. When the probe's sprung hook is removed, a metallic ring surrounding the probe tip can be seen. This ring is at ground potential and the best ground connection point for making noise-free measurements. Wrapping bare wire around the ground ring and then connecting that ground wire into the circuit with the shortest possible wire length, then connecting the probe tip to the point being measured, ensures error-free measurement. Probe should be compensated according to probe manufacturer's guidelines to ensure error-free measurement.

- Maximum Drain Current Drain current can be measured indirectly by monitoring inductor current. A current probe should be inserted between the bridge rectifier and inductor connection. At maximum ambient temperature, minimum input voltage and maximum output load, verify Drain current waveforms at start-up for any signs of inductor saturation. When performing this measurement with Sendust inductor, it is typical to see inductor waveforms that show exponential increase in current due to permeability drop. This should not be confused with hard saturation.

- 3. Thermal Check At maximum output power, minimum input voltage and maximum ambient temperature; verify that temperature specifications are not exceeded for the HiperPFS-5 device, PFC inductor, output diodes and output capacitors. Thermal margin should be enough to allow for the part-to-part variation of the RDS(ON) of HiperPFS-5 device, as specified in the data sheet. A maximum package temperature of 100 °C is recommended to allow for these variations.

- Input PF should improve with load, if performance is found to progressively deteriorate with loading, it is a sign of possible noise pick-up by the VOLTAGE MONITOR pin circuit, the FEED-BACK pin circuit, and the COMPENSATION pin circuit.

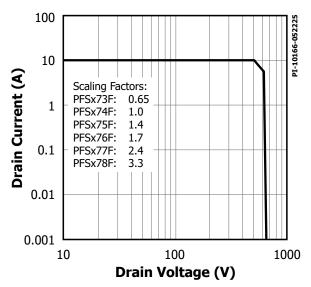

#### Absolute Maximum Ratings1,2

| DRAIN Pin Voltage (non-repet<br>DRAIN Pin Voltage (continuou | s)         | 0.3 V to 6503 V     |

|--------------------------------------------------------------|------------|---------------------|

| DRAIN Pin Peak Current: PFS5                                 |            |                     |

| PFS                                                          | ix74F      | 10.0 A <sup>8</sup> |

| PFS5                                                         | x75F       | 14.0 A <sup>8</sup> |

| PFS                                                          | x76F       | 17.0 A <sup>8</sup> |

| PFS                                                          | x77F       | 24.0 A <sup>8</sup> |

| PFS!                                                         | x78F       | 33.0 A <sup>8</sup> |

| VCC Pin                                                      |            | 0.3 V to 35 V       |

| V <sub>s</sub> , V, FB, PG, PGT, PS, REF, VI                 | OR, C Pins | 0.3 V to 5.6 V      |

| XD1/XD2 Pin Voltage <sup>7</sup>                             |            | 1000 V              |

| XD1/XD2 Pin Current8                                         |            | 5 mA                |

| Storage Temperature                                          |            | 65 to 150 °C        |

| Operating Junction Temperatu                                 | re4        | 40 to 150 °C        |

| Ambient Temperature                                          |            | 40 to 105 °C        |

| Lead Temperature <sup>5</sup>                                |            | 260 °C              |

| p                                                            |            |                     |

#### Notes:

- 1. All voltages referenced to SOURCE, T<sub>A</sub> = 25 °C

- Maximum ratings specified may be applied one at a time without causing permanent damage to the product. Exposure to Absolute Maximum Ratings conditions for extended periods of time may affect product reliability.

- 3. Self-supply not active.

- 4. Normally limited by internal circuitry.

- 5. 1/16" from case for 5 seconds.

- 6. Non-repetitive pulse.

- 7. Voltage of XD1 pin relative to XD2 pin in either polarity.

- 8. The peak current is allowed while the XD1/XD2 voltage is simultaneously less than 400 V.

#### **Thermal Resistance**

Thermal Resistance: PFS5x73F

#### Notes:

- 1. Soldered to 0.36 sq. inch (232 mm2) 2 oz. (610 g/m2) copper clad.

- 2. Soldered to 1 sq. inch (645 mm2), 2 oz. (610 g/m2) copper clad.

- The case temperature is measured at the bottom of the package body on the exposed pad.

| Parameter                                              | Symbol                          | Conditions SOURCE = 0 V, $T_{J} = -40 \text{ to } +125 \text{ °C}$ (See Note C)                                            | Pin              | Min | Тур  | Max | Units |

|--------------------------------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------|-----|------|-----|-------|

| Currents                                               | _                               |                                                                                                                            |                  |     |      | ,   | ,     |

| Current Consumption —<br>In Burst Mode<br>No Switching | $\mathbf{I}_{\text{CC(BURST)}}$ | $VCC = 12 \text{ V, V}_{FB} = 3.85 \text{ V, C} < V_{ERR(MIN)}$<br>$0 \text{ °C} < T_{J} < 100 \text{ °C}$<br>V = 1.414  V | VCC              |     | 700  | 850 | μА    |

| Leakage Current in                                     | т                               | 0 V < Pin Voltage < REF $T_{J} = 25 \text{ °C}$ $V_{DR} < V_{DR(UV+)}$                                                     | V, FB, C,<br>PGT |     | ±10  |     | nA    |

| UVLO State                                             | I <sub>oz</sub>                 | $V_{PG} = REF$ $T_{J} = 25  ^{\circ}C$ $V_{PG} = V$                                                                        | PG               |     | ±0.1 |     | μΑ    |

| Pull-Down Current on<br>Feedback                       | I <sub>FB(PD)</sub>             | 0 °C < T <sub>J</sub> < 100 °C<br>V <sub>FB</sub> = 5 V                                                                    | FB               |     | 100  | 150 | nA    |

|                                                                                         |                         | Cond                                                                       | itions                                      |      |      |      |               |

|-----------------------------------------------------------------------------------------|-------------------------|----------------------------------------------------------------------------|---------------------------------------------|------|------|------|---------------|

| Parameter                                                                               | Symbol                  | SOURCE = 0 V, $V_{cc}$ = 12 V,<br>$T_{J}$ = -40 to +125 °C<br>(See Note C) |                                             | Min  | Тур  | Max  | Units         |

| <b>Control Functions</b>                                                                |                         |                                                                            |                                             |      |      |      |               |

| Maximum Operating<br>"On-Time" Controller                                               | t <sub>on(MAX)</sub>    |                                                                            |                                             |      | 34   |      | μS            |

| Maximum Operating<br>"Off-Time" Controller                                              | t <sub>off(MAX)</sub>   |                                                                            | ted on the VS pin<br>n CCM mode)            |      | 250  | 300  | μS            |

| Feedback                                                                                |                         |                                                                            |                                             | '    |      |      |               |

| Internal Feedback Error<br>Voltage Reference                                            | $V_{_{FB(REF)}}$        | T <sub>1</sub> =                                                           | 25 ℃                                        | 3.82 | 3.85 | 3.88 | V             |

| Feedback Error-Amplifier<br>Transconductance Gain                                       | Gm                      | 3.75 V < V<br>0 °C < T,<br>C =                                             | Y <sub>FB</sub> < 3.95 V<br>< 100 °C<br>4 V | 75   | 90   |      | μ <b>A</b> /V |

| Soft Shutdown Time                                                                      | t <sub>shutdwn</sub>    | See N                                                                      | lote A                                      |      | 1.00 |      | ms            |

| FEEDBACK Pin Start-Up/<br>Fault Threshold                                               | $V_{FB(OFF)}$           | 0 °C < T <sub>1</sub>                                                      |                                             | 0.64 | 0.71 | V    |               |

| FEEDBACK Pin<br>Undervoltage Assertion<br>Threshold                                     | V <sub>FB(UV)</sub>     | 0 °C < T,                                                                  | 2.09                                        | 2.25 | 2.36 | V    |               |

| FEEDBACK Pin<br>Overvoltage Assertion<br>Threshold                                      | $V_{\text{FB(OV+)}}$    | 0 °C < T,                                                                  | < 100 °C                                    | 4.00 | 4.10 |      | V             |

| FEEDBACK Pin<br>Overvoltage<br>Deassertion Threshold                                    | V <sub>FB(OV-)</sub>    | 0 °C < T,                                                                  | < 100 °C                                    |      | 4.00 | 4.10 | V             |

| FEEDBACK Pin<br>Overvoltage Hysteresis                                                  | $V_{\text{FB(OVHYST)}}$ | 0 °C < T <sub>3</sub>                                                      | < 100 °C                                    |      | 0.1  |      | V             |

| Voltage on C Pin That<br>Triggers Switching<br>During a Burst-Mode<br>Recovery, or When | V                       | 0 °C < T, < 100 °C                                                         | V <sub>IN</sub> < 140 VAC                   |      | 0.39 |      | V             |

| Commencing Soft-Start<br>(COMPENSATION Pin<br>Burst Disable<br>Threshold)               | $V_{ERR(MIN+)}$         | 0.66 (1) (100 6                                                            | V <sub>IN</sub> > 170 VAC                   |      | 0.19 |      | v             |

| Voltage on C Pin That<br>Suppresses Switching,                                          | V                       | 0.00 4 T 4 100.00                                                          | V <sub>IN</sub> < 140 VAC                   |      | 0.34 |      | V             |

| Causing the Device to<br>Enter Burst-Mode<br>(Burst Enable Threshold)                   | V <sub>ERR(MIN-)</sub>  | 0 °C < T <sub>1</sub> ≤ 100 °C                                             | V <sub>IN</sub> > 170 VAC                   |      | 0.13 |      | V             |

| Hysteresis of V <sub>ERR(MIN)</sub><br>(COMPENSATION Pin                                | V                       | V <sub>ERR(MIN+)</sub> - V <sub>ERR(MIN-)</sub>                            | V <sub>IN</sub> < 140 VAC                   |      | 0.05 |      | V             |

| Burst Threshold<br>Hysteresis)                                                          | V <sub>ERR(HYST)</sub>  | 0 °C < T <sub>1</sub> < 100 °C                                             | V <sub>IN</sub> > 170 VAC                   |      | 0.06 |      | V             |

|                                                                                                                             | I                           |                                                                                                                                                                                                                                                             |      |       |      |       |

|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|-------|

| Parameter                                                                                                                   | Symbol                      | Conditions  SOURCE = 0 V, $V_{CC}$ = 12 V, $T_{J}$ = -40 to +125 °C  (See Note C)                                                                                                                                                                           | Min  | Тур   | Max  | Units |

| Line Sense / Peak Detecto                                                                                                   | or                          |                                                                                                                                                                                                                                                             |      |       |      |       |

| Line Sense and Peak<br>Detector Input Voltage<br>(Line-Sense Input<br>Voltage Range)                                        | $V_{_{V(RANGE)}}$           | The voltage on V may exceed the upper specification, however the line sense function is saturated at its full scale. Not tested.                                                                                                                            |      |       | 4    | V     |

| Brown-In<br>Threshold Voltage                                                                                               | V <sub>BR+</sub>            | 0 °C < T <sub>J</sub> < 100 °C                                                                                                                                                                                                                              |      | 1.102 |      | V     |

| Brown-Out<br>Threshold Voltage                                                                                              | V <sub>BR-</sub>            | 0 °C < T <sub>J</sub> < 100 °C                                                                                                                                                                                                                              | 0.86 | 0.895 | 1.12 | V     |

| Brown-Out Threshold for<br>Square Wave (Brown-Out<br>Threshold for High Duty<br>Cycle Square Wave)                          | $V_{BR(SQ)}$                | 0 °C < T <sub>3</sub> < 100 °C<br>See Note A                                                                                                                                                                                                                |      | 0.86  |      | V     |

| Soft-Start Brown-Out<br>Threshold Voltage<br>(Start-Up Brown-Out<br>Threshold Voltage<br>(During NTC Warm-Up<br>Time))      | V <sub>BR(NTC)</sub>        | 0 °C < T <sub>J</sub> < 100 °C<br>See Note A                                                                                                                                                                                                                |      | 0.74  |      | V     |

| Brown-In/Out Hysteresis<br>(V <sub>BR+</sub> - V <sub>BR-</sub> ) (Brown-In /<br>Out Hysteresis (After<br>NTC Warm-Up Time) | $V_{\text{BR(HYST)}}$       | 0 °C < T <sub>J</sub> < 100 °C                                                                                                                                                                                                                              | 190  | 207   | 220  | mV    |

| Brown-Out<br>Debounce Timer                                                                                                 | t <sub>BROWN-OUT</sub>      | See Note A                                                                                                                                                                                                                                                  |      | 54    |      | ms    |

| Brown-Out Debounce<br>Timer During Start-Up<br>with VBR_NTC Threshold                                                       | t <sub>BROWN-OUT(NTC)</sub> | Triggered during startup (while $t_{\text{STARTUP}}$ is active) if the peak of the V pin is lower than $V_{\text{BR-NTC}}$ . See Note A                                                                                                                     |      | 1000  |      | ms    |

| Start-Up Timer for Using<br>Lower Brown-Out<br>Threshold (V <sub>BR-NTC</sub> )                                             | t <sub>start-up</sub>       | The timer is triggered when switching starts. The timer aborts when a peak $< V_{\text{BR-NTC}}$ . The timer restarts at zero when a peak $> V_{\text{BR-NTC}}$ . When timer expires, the higher brown-out threshold $V_{\text{BR}}$ is applied. See Note A |      | 1000  |      | ms    |

| VOLTAGE MONITOR Pin<br>High-Line Threshold                                                                                  | $V_{V(HIGH+)}$              | (170 VAC)<br>See Note A                                                                                                                                                                                                                                     |      | 2.42  |      | V     |

| VOLTAGE MONITOR Pin<br>High-Line Deassertion<br>Threshold                                                                   | V <sub>V(HIGH-)</sub>       | (140 VAC)<br>See Note A                                                                                                                                                                                                                                     |      | 2.00  |      | V     |

| Parameter                                     | Symbol                     | Conditions<br>SOURCE = 0 V, $V_{cc}$ = 12 V,<br>$T_{J}$ = -40 to +125 °C<br>(See Note C) |                         |                         | Min                     | Тур | Max | Units    |

|-----------------------------------------------|----------------------------|------------------------------------------------------------------------------------------|-------------------------|-------------------------|-------------------------|-----|-----|----------|

| <b>Current Limit / Circuit</b>                | Protection                 | ı                                                                                        |                         |                         |                         |     |     |          |

|                                               |                            | Full Power                                                                               |                         |                         |                         | Ι   |     | -        |

|                                               |                            | di/dt =                                                                                  | PFS5x73F                | V <sub>v</sub> < 2 V    | 2.8                     | 3.1 | 3.3 | -        |

|                                               |                            | 293 mA/μs                                                                                |                         | V <sub>v</sub> > 2.42 V |                         | 2.1 |     |          |

|                                               |                            | di/dt =                                                                                  | PFS5x74F                | V <sub>v</sub> < 2 V    | 4.5                     | 4.8 | 5.1 |          |

|                                               |                            | 437 mA/μs                                                                                | 1133%                   | V <sub>v</sub> > 2.42 V |                         | 3.3 |     |          |

|                                               | _                          | di/dt =                                                                                  | DECE-7FF                | V <sub>v</sub> < 2 V    | 5.0                     | 5.3 | 5.6 |          |

| Over-Current<br>Protection Limit <sup>1</sup> | $I_{OCP}$                  | 494 mA/μs                                                                                | PFS5x75F                | V <sub>v</sub> > 2.42 V |                         | 3.6 |     | A        |

| Protection Limit                              | T <sub>1</sub> = 25 °C     | di/dt =                                                                                  |                         | V <sub>v</sub> < 2 V    | 6.0                     | 6.4 | 6.8 |          |

|                                               | di/dt = PFS5x<br>627 mA/μs | PFS5x76F                                                                                 | V <sub>v</sub> > 2.42 V |                         | 4.3                     |     |     |          |

|                                               |                            | di/dt =<br>703 mA/μs                                                                     |                         | V <sub>v</sub> < 2 V    | 7.0                     | 7.5 | 7.9 |          |

|                                               |                            |                                                                                          |                         | V <sub>v</sub> > 2.42 V |                         | 5.0 |     |          |

|                                               |                            | di/dt —                                                                                  |                         | V <sub>v</sub> < 2 V    | 8.5                     | 9.0 | 9.5 | -        |

|                                               |                            | di/dt =<br>836 mA/μs                                                                     |                         | V <sub>v</sub> > 2.42 V |                         | 6.1 |     | -        |

|                                               |                            | 90% Full Pov                                                                             | ver                     | V                       |                         |     |     |          |

|                                               |                            | di/dt =                                                                                  |                         | V <sub>v</sub> < 2 V    | 2.6                     | 2.8 | 3.1 |          |

|                                               |                            | 263 mA/μs                                                                                | PFS5x73F                | V <sub>v</sub> > 2.42 V |                         | 1.9 |     |          |

|                                               |                            | di/dt =                                                                                  |                         | V <sub>v</sub> < 2 V    | 4.1                     | 4.4 | 4.8 |          |

|                                               |                            | 393 mA/μs                                                                                | PFS5x74F                | V <sub>v</sub> > 2.42 V |                         | 3.0 |     | -        |

|                                               |                            | J:/JL                                                                                    |                         | V <sub>v</sub> < 2 V    | 4.5                     | 4.9 | 5.3 | -        |

| Over-Current                                  | I <sub>OCP</sub>           | di/dt =<br>445 mA/μs                                                                     | PFS5x75F                | V <sub>v</sub> > 2.42 V |                         | 3.3 |     | Α        |

| Protection Limit <sup>1</sup>                 | T <sub>3</sub> = 25 °C     | 11/1                                                                                     |                         | V <sub>V</sub> < 2 V    | 5.4                     | 5.9 | 6.4 | <b>A</b> |

|                                               |                            | di/dt =<br>564 mA/μs                                                                     | PFS5x76F                | V <sub>V</sub> > 2.42 V | 5.1                     | 4.0 | J., | -        |

|                                               |                            |                                                                                          |                         | V <sub>v</sub> > 2.42 V | 6.3                     | 6.9 | 7.4 | -        |

|                                               |                            | di/dt =<br>633 mA/μs                                                                     | PFS5x77F                |                         | 0.5                     |     | /.7 |          |

|                                               |                            |                                                                                          |                         | V <sub>v</sub> > 2.42 V | 7.                      | 4.6 | 0.0 |          |

|                                               |                            | di/dt =                                                                                  | PFS5x78F                | V <sub>V</sub> < 2 V    | 7.6                     | 8.3 | 8.9 | -        |

|                                               |                            | 752 mA/μs                                                                                | 752 mA/μs               |                         | V <sub>v</sub> > 2.42 V |     | 5.6 |          |

| Parameter                                  | Symbol                   | SOUR<br>T <sub>3</sub> | Min                                  | Тур                     | Max | Units |     |    |

|--------------------------------------------|--------------------------|------------------------|--------------------------------------|-------------------------|-----|-------|-----|----|

| Current Limit / Circuit Pr                 | otection (con            | T.                     |                                      |                         |     |       |     |    |

|                                            |                          | 80% Full Pov           | ver                                  |                         |     |       |     | -  |

|                                            |                          | di/dt =<br>234 mA/μs   | PFS5x73F                             | V <sub>v</sub> < 2 V    | 2.4 | 2.6   | 2.8 | -  |

|                                            |                          | Σ5 1 111 γ μο          |                                      | V <sub>v</sub> > 2.42 V |     | 1.7   |     | -  |

|                                            |                          | di/dt =<br>350 mA/μs   | PFS5x74F                             | V <sub>v</sub> < 2 V    | 3.7 | 4.1   | 4.4 | -  |

|                                            |                          | 78-3                   |                                      | V <sub>v</sub> > 2.42 V | 4.1 | 2.7   | 4.0 | -  |

| Over-Current                               | I <sub>OCP</sub>         | di/dt =<br>395 mA/μs   | PFS5x75F                             | V <sub>v</sub> < 2 V    | 4.1 | 4.5   | 4.8 | -  |

| Protection Limit <sup>1</sup>              | T <sub>1</sub> = 25 °C   | 78-3                   |                                      | V <sub>v</sub> > 2.42 V | 4.0 | 3.0   | F.0 | Α  |

|                                            |                          | di/dt =<br>500 mA/μs   | PFS5x76F                             | V <sub>v</sub> < 2 V    | 4.9 | 5.4   | 5.8 | _  |

|                                            |                          | ,,                     |                                      | V <sub>v</sub> > 2.42 V | го. | 3.6   | 6.7 | _  |

|                                            |                          | di/dt =<br>562 mA/μs   | PFS5x77F                             | V <sub>V</sub> < 2 V    | 5.8 | 6.3   | 6.7 | -  |

|                                            |                          | ,,                     | PFS5x78F                             | VV > 2.42 V             | 7.0 | 4.2   | 0.1 |    |

|                                            |                          | di/dt =<br>669 mA/μs   |                                      | V <sub>v</sub> < 2 V    | 7.0 | 7.6   | 8.1 |    |

|                                            |                          | 70% Full Pov           | VOT                                  | V <sub>v</sub> > 2.42 V |     | 5.1   |     |    |

|                                            |                          |                        | /dt = DESEX73E                       | V <sub>v</sub> < 2 V    | 2.2 | 2.3   | 2.5 |    |

|                                            |                          | 205 mA/μs              |                                      | V <sub>v</sub> > 2.42 V |     | 1.6   |     |    |

|                                            |                          | di/dt _                |                                      | V V < 2 V               | 3.4 | 3.7   | 4.0 |    |

|                                            |                          | di/dt =<br>306 mA/μs   | PFS5x74F                             | V <sub>v</sub> > 2.42 V |     | 2.5   |     |    |

|                                            |                          | di/dt =<br>346 mA/μs   | PFS5x75F                             | V V < 2 V               | 3.7 | 4.0   | 4.3 |    |