# **Application Note AN-58 LinkSwitch-HP** Family

Design Guide

#### Introduction

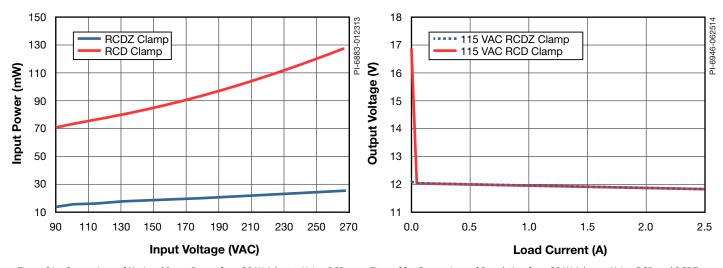

The LinkSwitch<sup>TM</sup>-HP family is a highly integrated monolithic switcher IC designed for off-line power supplies. Output regulation is achieved using primary-side sense regulation (PSR) that gives accurate output regulation for designs up to 90 W / 117 W. PSR eliminates secondary-side components including the optocoupler while still achieving output regulation of  $\pm 5\%$  or better at the supply output. Other key technical performance parameters are listed in Table 1.

The controller is simple to use, utilizing a combination of variable frequency and current mode control. Loop compensation is provided by a single RC network. The input line and output overvoltage and loss of regulation sensing is all accomplished through the feedback resistor sense network which minimizes component count and eliminates the need for lossy direct high-voltage sensing. There is also the function of programming the maximum peak drain current with a single external resistor to give flexibility in both device and transformer core size selection to optimize size, cost and efficiency.

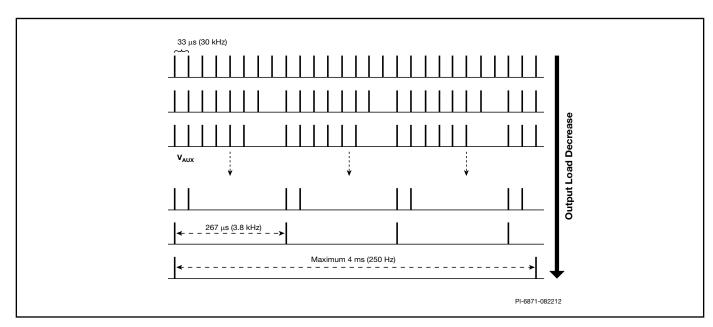

Two maximum MCM (multi-cycle-mode) off-time (related tominimum switching frequency) and MOSFET voltage rating options are available as shown in Table 2.

The maximum switching cycle off period  $T_{\text{MCM(OFF)}}$  determines the minimum switching frequency and both the no-load input power performance and no-load to a high load output transient response. For lowest no-load input power 4 ms should be selected or for faster transient response 0.5 ms should be selected. The 650 V MOSFET BV<sub>DSS</sub> rating offers a lower cost option in applications with less stringent de-rating requirements.

| Part Number | BV <sub>DSS</sub> | T <sub>MCM(OFF)</sub> | P <sub>NC</sub> |

|-------------|-------------------|-----------------------|-----------------|

| LNK677x     | 725 V             | 4 ms                  | <30 mW          |

| LNK676x     | 650 V             | 4 ms                  | <30 mW          |

| LNK666x     | 650 V             | 0.5 ms                | <100 mW         |

x = Device Size (3, 4, 5, 6, 7)

Table 2. LinkSwitch-HP Device Family Options.

| Power range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ≤90 W (85 VAC – 265 VAC)       |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--|--|--|

| Power range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ≤117 W (195 VAC – 265 VAC)     |  |  |  |

| Law as lead in the same                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <30 mW (LNK67xx devices)       |  |  |  |

| Low no-load input power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <100 mW (LNK66xx devices)      |  |  |  |

| High southers and a second of the second of | >0.75 W output for <1 W input  |  |  |  |

| High available output power in standby                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | >50 mW output for <0.1 W input |  |  |  |

| High full load efficiency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | >86.5% (115 VAC, 12 V, 30 W)   |  |  |  |

| Protection and reliability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                |  |  |  |

| Output short-circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Auto-restart or latching       |  |  |  |

| Output overload/over-current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Auto-restart or latching       |  |  |  |

| Open-loop*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Auto-restart                   |  |  |  |

| Output overvoltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Auto-restart or latching       |  |  |  |

| Line brown-in/out (line UV)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Auto-restart                   |  |  |  |

| Line overvoltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Shut down                      |  |  |  |

| Accurate thermal shutdown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Hysteretic or latching         |  |  |  |

| Device open-circuit / adjacent pin short                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Yes                            |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                |  |  |  |

<sup>\*</sup>Open-loop: Open connection between the feedback winding and feedback divider network R<sub>FB2</sub>, or the FEEDBACK pin to the feedback divider network R<sub>FB2</sub>.

Table 1. LinkSwitch-HP Family Key Technical Performance Parameters.

www.power.com August 2017

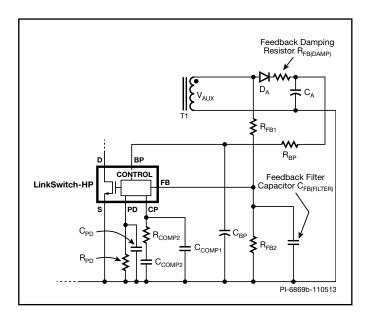

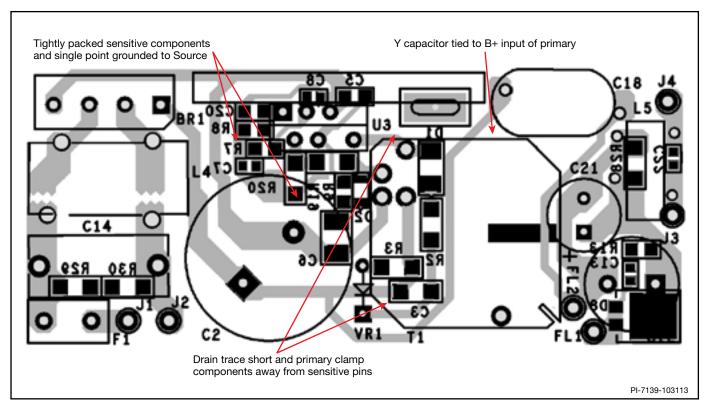

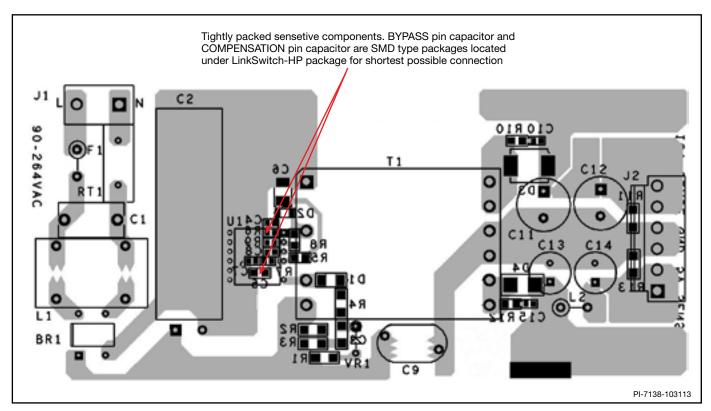

#### **Basic Circuit Configuration**

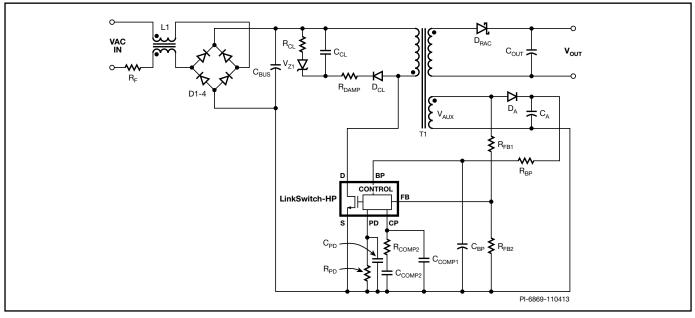

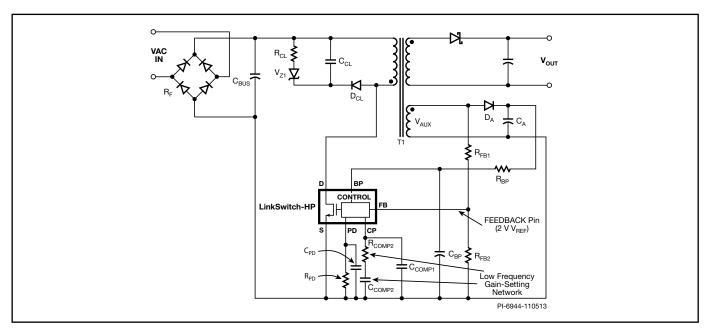

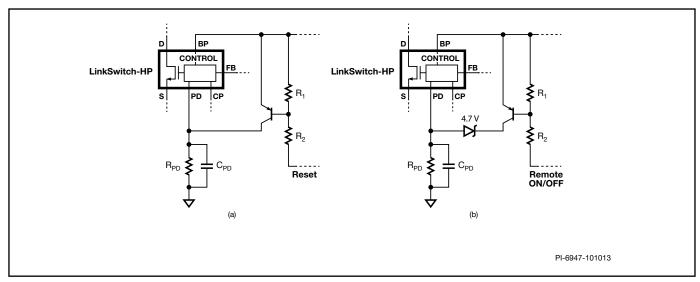

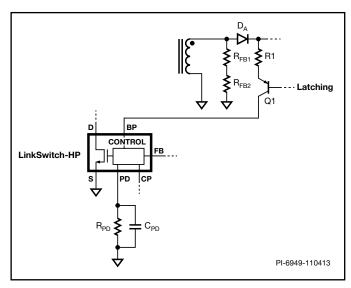

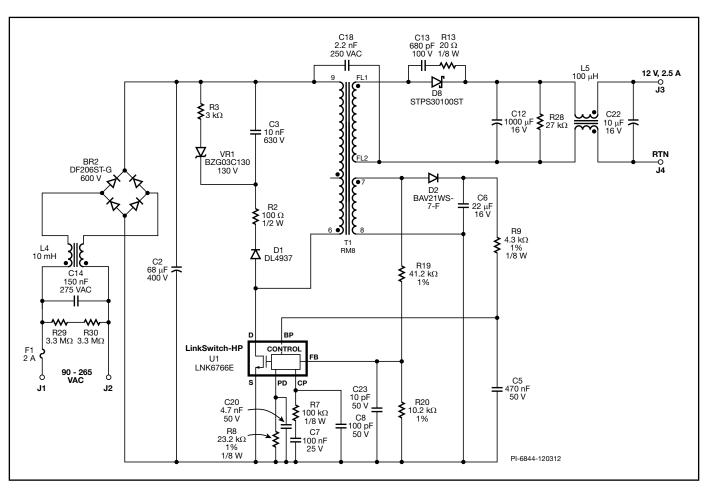

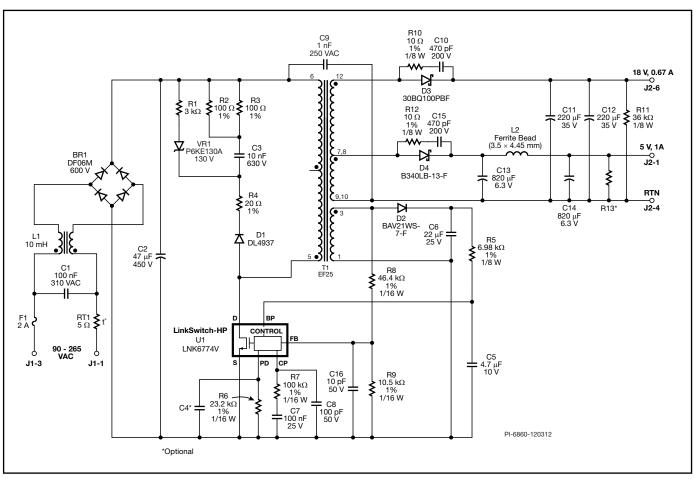

The circuit shown in Figure 1 shows the basic configuration of a flyback power supply designed using LinkSwitch-HP. Because of the high level integration of LinkSwitch-HP, many power supply design challenges are resolved in the IC. Far fewer issues are left to be addressed externally, resulting in one common circuit configuration for all applications. Different output power levels may require different values for some circuit components, but the circuit configuration stays unchanged. Advanced features like line

#### **Quick Start**

Readers willing to start immediately can use the following information to quickly design the transformer and select the components for a first prototype. Only the information described below needs to be entered into the PIXIs spreadsheet, other parameters will be automatically selected based on a typical design.

Enter AC input voltage range VAC<sub>MIN</sub> (VAC<sub>MAX</sub> (Table 5) and line frequency f<sub>L</sub>. Generally using a nominal line frequency of 50 Hz for a universal input design gives sufficient design margin.

Figure 1. Typical LinkSwitch-HP Single Output Flyback Power Supply with Primary Sensed Voltage Regulation.

undervoltage and overvoltage, external current limit programming, line feed-forward, and remote ON/OFF are easily implemented with a minimal number of external components, but do involve additional design considerations. For specific detail of how each of these features operates please refer to the LinkSwitch-HP data sheet.

#### Scope

This application note is intended for engineers designing an isolated AC-DC flyback power supply using the LinkSwitch-HP family of devices. It provides guidelines to enable an engineer to quickly select key components and also complete a suitable transformer design. To simplify the task this application note refers directly to the PIXIs design spreadsheet that is part of the PI Expert™ design software suite. The basic configuration used in LinkSwitch-HP flyback power supplies is shown in Figure 1, which also serves as the reference circuit for component identifications used in the description throughout this application note.

In addition to this application note the reader may also find the LinkSwitch-HP Reference Design Kit (RDK) containing an engineering prototype board and device samples useful as an example of a working power supply. Further details on downloading PI Expert, obtaining a RDK and updates to this document can be found at www. powerint.com.

- Enter Nominal or Main Output Voltage Vo.

- Enter output power, P<sub>o</sub>. If there is a peak power requirement then enter this value.

- Enter efficiency estimate, η, using Table 3 as a guide.

| Input Voltage<br>(VAC) | Output Voltage<br>(V) | Efficiency<br>Estimate (%) |

|------------------------|-----------------------|----------------------------|

|                        | 3.3                   | 77                         |

| 85-265 or 85-132       | 5                     | 82                         |

|                        | ≥12                   | 86                         |

|                        | 3.3                   | 77.5                       |

| 190-265                | 5                     | 82.5                       |

|                        | ≥12                   | 87                         |

|                        |                       |                            |

Table 3. Efficiency Estimate vs. Input and Output Voltage.

Adjust the number accordingly after measuring the efficiency of the first prototype-board at maximum load and  $VAC_{\text{Min}}$ .

- · Enter loss allocation factor Z

- 0.5 for typical application.

- Enter C<sub>IN</sub> input capacitance

- $2~\mu\text{F/W}\sim 3~\mu\text{F/W}$  for universal (85-265 VAC) or single (100/115 VAC) line.

- Use 1  $\mu$ F/W single 230 VAC for single (185-265 VAC) line. • Select LinkSwitch-HP from drop down list or leave as Auto. Auto selects device based on output power and line input voltage.

Select the device in the Table 4 according to output power and line input voltage.

• Enter core type (if desired) from drop down menu. A suggested core size will be selected automatically if none is entered.

**Output Power Table1** 230 VAC ±15% 85-265 VAC Heat Product<sup>4</sup> Open Open Sink Adapter Adapter Frame Frame LNK67x3K/V PCB-W1 15 W 25 W 9 W 15 W LNK67x3K PCB-R<sup>2</sup> 21 W 35 W 12 W 21 W LNK67x3E Metal 21 W 35 W 13 W 27 W LNK67x4K/V PCB-W1 16 W 28 W 11 W 20 W PCB-R<sup>2</sup> LNK67x4K 22 W 39 W 15 W 28 W LNK67x4E Metal 30 W 47 W 20 W 36 W PCB-W1 19 W 30 W 13 W 22 W LNK67x5K/V PCB-R<sup>2</sup> LNK67x5K 26 W 42 W 18 W 31 W LNK67x5E Metal 40 W 593 W 26 W 45 W PCB-W<sup>1</sup> LNK67x6K/V 21 W 34 W 15 W 26 W LNK67x6K PCB-R<sup>2</sup> 30 W 48 W 22 W 37 W 883 W 683 W LNK67x6E Metal 60 W 40 W LNK67x7K/V PCB-W1 25 W 41 W 19 W 30 W LNK67x7K PCB-R<sup>2</sup> 59 W 27 W 43 W 36 W LNK67x7E Metal 853 W 1173 W 55 W 903 W

Table 4. Output Power Table.

#### Notes:

- 1. PCB heat sink with wave soldering.

- 2. PCB heat sink with IR reflow soldering (exposed pad thermally connected to PCB).

- 3. Maximum power specified based on proper thermal dissipation/heat sink size.

- Packages: E: eSIP-7C, K: eSOP-12B, V: eDIP-12B. See Table 2 for all device options.

If any warnings are generated, make changes to the design by following instructions in spreadsheet column 6 (farthest to the right).

- · Build transformer

- Select key components

- Build prototype and iterate design as necessary, entering measured values into spreadsheet where estimates were used (e.g. efficiency, V<sub>vm</sub>).

### **Step-by-Step Design Procedure Introduction**

The design flow allows for design of power supplies either with or without a peak output power requirement. This is of particular relevance when using the V package with no heat sink attached, using the PCB as the heat sink. This results in a design which is thermally rather than device power capability limited. The power supply is then capable of delivering peak power for durations determined by the temperature rise of the LinkSwitch-HP and other power components in the circuit. The programmable shutdown delay feature (via the PROGRAM (PD) pin) may be used to trigger shutdown after a specified duration in applications where an output voltage droop is acceptable during peak power operation.

As average power increases, based on the measured transformer, device and output diode temperatures, it may be necessary to select a larger transformer to allow increased copper area for the windings, increase the amount of device and output diode heat sinking.

The output power table (Table 4) provides guidance for peak and continuous (average) power levels for both sealed adapters and open frame thermal conditions. For the eSIP (E) package it is assumed that an external heat sink is fitted and power delivery is limited by the device current limit. For the eDIP (V) and eSOP (K) packages, it is assumed that only the PCB is used for heat sinking and the device is thermally limited. As the current limit values are the same regardless of package the continuous values for the V and K package can be increased to those of the E package by improving heat sinking, for example placing a heat sink on the exposed pad on top of the package.

When using the design spreadsheet whenever an input cell is changed any changes in output calculations are highlighted in yellow. This is helpful in aiding understanding of the dependencies between parameters.

| ENTER TRANSFORMER   | CORE/CONSTRUCTI  | ON VARIABLES |        |                                                                       |

|---------------------|------------------|--------------|--------|-----------------------------------------------------------------------|

| Select Core Size    | Auto             | EF25         |        |                                                                       |

| Core                |                  | EF25         |        | Selected Core                                                         |

| Custom Core         |                  |              |        | Enter name of custom core is applicable                               |

| AE                  |                  | 0.518        | cm^2   | Core Effective Cross Sectional Area                                   |

| LE                  |                  | 5.78         | cm     | Core Effective Path Length                                            |

| AL                  |                  | 2000         | nH/T^2 | Ungapped Core Effective Inductance                                    |

| 3W                  |                  | 15.6         | mm     | Bobbin Physical Winding Width                                         |

| М                   |                  | 0.00         | mm     | Safety Margin Width (Half the Primary to Secondary Creepage Distance) |

| L                   |                  | 2            |        | Number of Primary Layers                                              |

| NS                  |                  | 10           |        | Number of Secondary Turns                                             |

| DC INPUT VOLTAGE PA | RAMETERS         |              |        |                                                                       |

| VMIN                |                  | 93           | V      | Minimum DC Input Voltage                                              |

| VMAX                |                  | 375          | V      | Maximum DC Input Voltage                                              |

| CURRENT WAVEFORM    | SHAPE PARAMETERS | S            |        |                                                                       |

| DMAX                |                  | 0.55         |        | Maximum Duty Cycle                                                    |

| AVG                 |                  | 0.40         | Α      |                                                                       |

| P                   |                  | 1.05         | Α      | Peak Primary Current                                                  |

| R                   |                  | 0.63         | Α      | Primary Ripple Current                                                |

| IRMS                |                  | 0.56         | Α      | Primary RMS Current                                                   |

| TRANSFORMER PRIMA   | RY DESIGN PARAME | TERS         |        |                                                                       |

| LP TYP              |                  | 670          | uH     | Typical Primary Inductance                                            |

| LP_TOL              |                  | 10           | %      | Primary inductance Tolerance                                          |

| NP                  |                  | 87           |        | Primary Winding Number of Turns                                       |

| NB                  |                  | 8            |        | Bias Winding Number of Turns                                          |

| ALG                 |                  | 89           | nH/T^2 | Gapped Core Effective Inductance                                      |

| BM                  |                  | 1571         | Gauss  | Maximum Flux Density at PO, VMIN (BM<3100)                            |

| BP                  |                  | 3422         | Gauss  | Peak Flux Density (BP<3700)                                           |

| BAC                 |                  | 471          | Gauss  | AC Flux Density for Core Loss Curves (0.5 X Peak to Peak)             |

| ur                  |                  | 1776         |        | Relative Permeability of Ungapped Core                                |

| LG                  |                  | 0.70         | mm     | Gap Length (Lg > 0.1 mm)                                              |

| BWE                 |                  | 31.2         | mm     | Effective Bobbin Width                                                |

| OD                  |                  | 0.36         | mm     | Maximum Primary Wire Diameter including insulation                    |

| INS                 |                  | 0.06         |        | Estimated Total Insulation Thickness (= 2 * film thickness)           |

| DIA                 |                  | 0.30         |        | Bare conductor diameter                                               |

| AWG                 |                  |              | AWG    | Primary Wire Gauge (Rounded to next smaller standard AWG value)       |

| CM                  |                  |              | Cmils  | Bare conductor effective area in circular mils                        |

| CMA                 |                  |              |        | Primary Winding Current Capacity (200 < CMA < 500)                    |

Figure 2. Highlighting Changes to Calculated Results, in this Example NS Input was Changed Resulting in Highlighted Output Changes in Yellow.

| Nominal Input Voltage (VAC) | VAC | VAC <sub>MAX</sub> |

|-----------------------------|-----|--------------------|

| 100/115                     | 85  | 132                |

| 230                         | 195 | 265                |

| Universal                   | 85  | 265                |

Table 5. Standard Worldwide Input Line Voltage Ranges.

AN-58 Application Note

### Step 1 – Enter Application Variables $VAC_{MIN'}$ $VAC_{MAX'}$ $f_{L'}$ $V_{O'}$ $P_{O(AVE)'}$ $P_{O(PEAK)'}$ $\eta$ , Z, $V_{B'}$ $t_{C'}$ $C_{IN}$

| ENTER APPLICATION VARIABLES |      |    | Customer                                  |

|-----------------------------|------|----|-------------------------------------------|

| VACMIN                      | 85   | V  | Minimum AC Input Voltage                  |

| VACMAX                      | 265  | V  | Maximum AC Input Voltage                  |

| fL                          | 50   | Hz | AC Mains Frequency                        |

| VO                          | 12   | V  | Output Voltage (main)                     |

| PO                          | 30   | W  | Specified Output Power                    |

| n                           | 0.80 |    | Efficiency Estimate                       |

| Z                           | 0.50 |    | Loss Allocation Factor                    |

| VB                          | 10   | V  | Bias Voltage                              |

| tC                          | 3    | ms | Bridge Rectifier Conduction Time Estimate |

| CIN                         | 90   | uF | Input Filter Capacitor                    |

Figure 3. Application Variable Inputs.

#### Line Voltage, $VAC_{MIN}$ , $VAC_{MAX}$

Determine the input voltage range from Table 3. For DC input applications, for example where the supply is fed from a PFC generated DC bus, and provides a housekeeping / auxiliary supply in a larger system, enter the values for  $V_{\text{MIN}}$  and  $V_{\text{MAX}}$  directly.

#### Line Frequency, f,

50 Hz for universal or single 100 VAC, 60 Hz for single 115 VAC input. 50 Hz for single 230 VAC input. These values represent typical line frequencies rather than minimums. For most

#### Power Supply Loss Allocation Factor, Z

This factor represents the proportion of losses between the primary and the secondary of the power supply. Z factor is used together with the efficiency number to determine the actual power that must be delivered by the power stage. For example, losses in the input stage (EMI filter, rectification, etc) are not processed by the power stage (transferred through the transformer) and therefore, although they reduce efficiency, the transformer design is not affected by their effect on efficiency.

| DC INPUT VOLTAGE PARAMETE | RS |     |   |                          |

|---------------------------|----|-----|---|--------------------------|

| VMIN                      |    | 93  | V | Minimum DC Input Voltage |

| VMAX                      |    | 375 | V | Maximum DC Input Voltage |

Figure 4. DC Input Voltage Parameters.

applications this gives adequate overall design margin. For absolute worst-case or based on the product specification, reduce these numbers by 6% (47 Hz or 56 Hz). For half-wave rectification, use  $\rm f_{_L}/2$ . The value of  $\rm f_{_L}$  is used to calculate the value of  $\rm V_{_{MIN}}$ .

#### Nominal Output Voltage, Vo (V)

Enter the nominal output voltage of the main output during the continuous load condition. Generally the main output is the output with the highest output power.

#### Output Power, Po (W)

Enter the average output power of the power supply. If the power supply is a multiple output power supply, enter the sum total power of all the outputs.

#### Power Supply Efficiency, $\boldsymbol{\eta}$

Enter the estimated efficiency of the complete power supply measured at the output terminals under full load conditions and worst-case line (generally the lowest input voltage). Table 3 provides typical efficiency numbers for a single 5 V or 12 V output design. For multiple outputs calculate the proportion of the output power at lower voltage (<12 V) and higher voltage ( $\geq$ 12 V) and pick an efficiency estimate between the 5 V and 12 V numbers proportionally.

Examples of primary-side losses are losses incurred in the input rectifier and EMI filter, MOSFET conduction losses and primary-side winding losses. Examples of secondary-side losses include the losses in secondary diode, secondary windings and core losses, losses associated with the primary-side clamp circuit and the bias winding. For designs that do not have a peak power requirement, a value of 0.5 is recommended. For designs with a peak power requirement, enter 0.65. This difference accounts for increased input stage losses under peak power loading when the input stage components (common mode chokes, differential inductors, thermistor, diode bridge) are sized for the average rather than the peak power.

#### Bias Winding Output Voltage $(V_{_{\rm B}})$

Enter the voltage at the output of the bias winding output. A starting value of 10 V is recommended. Higher voltages increase no-load input power while values below 9 V are not recommended as at light load there may be insufficient voltage to bias the controller causing higher no-load power. As the output load increases the IC switching frequency increases, causing the bias voltage to rise. This is useful as it compensates the increase in IC consumption causes by MOSFET drive increase with frequency.

#### Bridge Diode Conduction Time, t<sub>c</sub> (ms)

Enter a bridge diode conduction time of 3 ms if there is no better data (from measurement) available.

#### Total Input Capacitance, $C_{IN}$ ( $\mu F$ )

Table 6 suggests suitable multiplication factors to be used for calculating input capacitance for different AC input voltage ranges. Select the next largest standard value (or combination where two input capacitors are used). Using smaller values will result in a lower capacitor voltage and therefore higher primary RMS currents which will increases losses, device dissipation and reduce efficiency.

| AC Input<br>Voltage (VAC) | Total Input Capacitance Per Watt Output Power ( $\mu F/W$ ) Full Wave Rectification |  |  |  |  |

|---------------------------|-------------------------------------------------------------------------------------|--|--|--|--|

| 100/115                   | 2-3                                                                                 |  |  |  |  |

| 230                       | 1                                                                                   |  |  |  |  |

| 85-265                    | 2-3                                                                                 |  |  |  |  |

Table 6. Suggested Total Input Capacitance for Different Input Voltage Ranges.

## Step 2 – Enter LinkSwitch-HP Variables: Device, Current Limit, V<sub>OR</sub>, V<sub>DS</sub>, V<sub>D</sub>, Select the Correct LinkSwitch-HP Device

#### **Device Selection**

First, refer to LinkSwitch-HP output power table (Table 4). Then compare the continuous power to adapter column number, for enclosed designs, or compare to open-frame column number if the power-supply is open-frame design. If the column number is smaller than continuous power, then select the next larger device or choose a different device package type. Similarly, if the continuous power is close to the adapter power levels given in the power table, then it may be necessary to switch to a larger device based on the measured

thermal performance of the prototype. In general, device thermals determine the maximum continuous power for adapter (enclosed) designs and device current limits for open-frame designs.

| Output I | Power | Table <sup>1</sup> |

|----------|-------|--------------------|

|----------|-------|--------------------|

|            | Heat               | 230 VA  | C ±15%        | 85-26   | 85-265 VAC    |  |

|------------|--------------------|---------|---------------|---------|---------------|--|

| Product⁴   | Sink               | Adapter | Open<br>Frame | Adapter | Open<br>Frame |  |

| LNK67x3K/V | PCB-W <sup>1</sup> | 15 W    | 25 W          | 9 W     | 15 W          |  |

| LNK67x3K   | PCB-R <sup>2</sup> | 21 W    | 35 W          | 12 W    | 21 W          |  |

| LNK67x3E   | Metal              | 21 W    | 35 W          | 13 W    | 27 W          |  |

| LNK67x4K/V | PCB-W <sup>1</sup> | 16 W    | 28 W          | 11 W    | 20 W          |  |

| LNK67x4K   | PCB-R <sup>2</sup> | 22 W    | 39 W          | 15 W    | 28 W          |  |

| LNK67x4E   | Metal              | 30 W    | 47 W          | 20 W    | 36 W          |  |

| LNK67x5K/V | PCB-W <sup>1</sup> | 19 W    | 30 W          | 13 W    | 22 W          |  |

| LNK67x5K   | PCB-R <sup>2</sup> | 26 W    | 42 W          | 18 W    | 31 W          |  |

| LNK67x5E   | Metal              | 40 W    | 59³ W         | 26 W    | 45 W          |  |

| LNK67x6K/V | PCB-W <sup>1</sup> | 21 W    | 34 W          | 15 W    | 26 W          |  |

| LNK67x6K   | PCB-R <sup>2</sup> | 30 W    | 48 W          | 22 W    | 37 W          |  |

| LNK67x6E   | Metal              | 60 W    | 88³ W         | 40 W    | 68³ W         |  |

| LNK67x7K/V | PCB-W <sup>1</sup> | 25 W    | 41 W          | 19 W    | 30 W          |  |

| LNK67x7K   | PCB-R <sup>2</sup> | 36 W    | 59 W          | 27 W    | 43 W          |  |

| LNK67x7E   | Metal              | 85³ W   | 117³ W        | 55 W    | 90³ W         |  |

Table 7. Output Power Table.

#### Notes:

- 1. PCB heat sink with wave soldering.

- 2. PCB heat sink with IR reflow soldering (exposed pad thermally connected to PCB).

- 3. Maximum power specified based on proper thermal dissipation/heat sink size.

- 4. Packages: E: eSIP-7C, K: eSOP-12B, V: eDIP-12B. See Table 2 for all device options.

| <b>ENTER LinkSwitch-HP VARIABL</b> | ES   |          |       |                                                                                           |

|------------------------------------|------|----------|-------|-------------------------------------------------------------------------------------------|

| LinkSwitch-HP                      | Auto | LNK6766E |       | Selected LinkSwitch-HP                                                                    |

| ILIMITMIN                          |      | 1.814    | Α     | Minimum Current limit                                                                     |

| ILIMITMAX                          |      | 2.087    | Α     | Maximum current limit                                                                     |

| ILIMITMIN_EXT                      |      | 1.814    | Α     | External Minimum Current limit                                                            |

| ILIMITMAX_EXT                      |      | 2.087    | Α     | External Maximum current limit                                                            |

| KI                                 | Auto | 1.000    | Α     | Current limit reduction factor                                                            |

| Rpd                                |      | 124.00   | k-ohm | Program delay Resistor                                                                    |

| Cpd                                |      | 33.00    | nF    | Program delay Capacitor                                                                   |

| Total programmed delay             |      | 0.86     | sec   | Total program delay                                                                       |

| fS                                 |      | 132      | kHz   | LinkSwitch-HP Switching Frequency: Choose between 132 kHz and 66 kHz                      |

| fSmin                              |      | 124      | kHz   | LinkSwitch-HP Minimum Switching Frequency                                                 |

| fSmax                              |      | 140      | kHz   | LinkSwitch-HP Maximum Switching Frequency                                                 |

| KP                                 |      | 0.60     |       | Ripple to Peak Current Ratio (0.4 < KP < 6.0)                                             |

| VOR                                |      | 108.40   | V     | Reflected Output Voltage                                                                  |

| Voltage Sense                      |      |          |       |                                                                                           |

| VUVON                              |      | 102.11   | V     | Undervoltage turn on                                                                      |

| VUVOFF                             |      | 43.19    | V     | Undervoltage turn off                                                                     |

| VOV                                |      | 462.09   | V     | Overvoltage threshold                                                                     |

| FMAX_FULL_LOAD                     |      | 135.55   | kHz   | Maximum switching frequency at full load                                                  |

| FMIN_FULL_LOAD                     |      | 120.06   | kHz   | Minimum switching frequency at full load                                                  |

| TSAMPLE_FULL_LOAD                  |      | 3.23     | us    | Minimum available Diode conduction time at full load. This should be greater than 2.7 us  |

| TSAMPLE_LIGHT_LOAD                 |      | 2.52     | us    | Minimum available Diode conduction time at light load. This should be greater than 1.4 us |

| VDS                                |      | 3.29     | V     | LinkSwitch-HP on-state Drain to Source Voltage                                            |

| VD                                 |      | 0.50     | V     | Output Winding Diode Forward Voltage Drop                                                 |

| VDB                                |      | 0.70     | V     | Bias Winding Diode Forward Voltage Drop                                                   |

Figure 5. LinkSwitch-HP Variables Section of Design Spreadsheet.

AN-58 Application Note

#### **External Current Limit Reduction Factor, KI**

The user entered factor KI indicates which device current limit will be selected. There are seven discrete current limit settings between 40% and 100% (=default) in incremental steps of 10%. Each is set via the value of the external programming resistor  $R_{\rm pD}$  (Cell [A35]) as shown in Table 8. In some countries like Korea, the 1% standard resistor value is different than the standard E96 value. To make it easy for resistor selection for the users, the adjusted external programming resistor  $R_{\rm pD}$  provided in Table 9 that is compliant with 1% standard resistor values in Korea. This value is measured at start-up and latched internally until the IC is reset at power-down. In most cases the current limit level should be set slightly above (15%) the minimum peak current ( $I_{\rm p}$ ) required for power delivery. This optimizes the transformer design by limiting the peak flux density (BP) during overload and start-up when the primary and MOSFET current will reach current limit.

| Ι <sub>ΡD</sub> (μΑ) | R <sub>PD</sub> (kΩ) | I <sub>LIMIT_NORM</sub> (%) | Ι <sub>ΡD</sub><br>(μ <b>A</b> ) | R <sub>PD</sub> (kΩ) | I <sub>LIMIT_NORM</sub> (%) |

|----------------------|----------------------|-----------------------------|----------------------------------|----------------------|-----------------------------|

| 10                   | 124                  | 100                         | 54                               | 23.2                 | 60                          |

| 16                   | 78.7                 | 90                          | 83                               | 15                   | 50                          |

| 24                   | 52.3                 | 80                          | 125                              | 10                   | 40                          |

| 36                   | 34.8                 | 70                          |                                  |                      |                             |

Table 8. Current Limit Reduction vs. Value of  $R_{pp}$ .

| Ι <sub>ΡD</sub> (μΑ) | R <sub>PD</sub> (kΩ) | I <sub>LIMIT_NORM</sub> (%) | Ι <sub>ΡD</sub><br>(μ <b>A</b> ) | R <sub>PD</sub> (kΩ) | I <sub>LIMIT_NORM</sub> (%) |

|----------------------|----------------------|-----------------------------|----------------------------------|----------------------|-----------------------------|

| 9.5                  | 130                  | 100                         | 51.6                             | 24                   | 60                          |

| 16.5                 | 75                   | 90                          | 82.7                             | 15                   | 50                          |

| 24.3                 | 51                   | 80                          | 125                              | 10                   | 40                          |

| 37.5                 | 33                   | 70                          |                                  |                      |                             |

Table 9. Current limit Reduction vs. Value of  $R_{\rm pp}$  Adjusted to be Compliant with Korea 1% Standard Resistor Value.

For higher efficiency and improved thermal performance, KI also allows the selection of a larger LinkSwitch-HP device to be used than required for power delivery by reducing KI, such that the current limit of the larger device is set to still be slightly above the calculated value for  $I_{\mbox{\tiny PK}}.$

Setting the current limit significantly higher (for instance 50%) than the value of  $I_{p_K}$  for power delivery can improve efficiency, especially for single AC input high-line only (190–265 VAC) designs. At high input voltages switching losses, as opposed to conduction losses, become dominant, are proportional to switching frequency. Setting the current limit 50% higher than required for power delivery reduces the device switching frequency. This is due to the control behavior of LinkSwitch-HP devices, when the primary peak current reduces to below 50% of the set current limit the switching frequency of the device reduces. (Note that the maximum output power of the power supply will be increased accordingly).

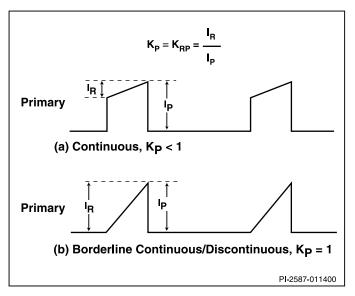

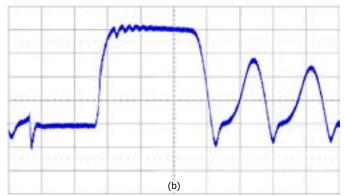

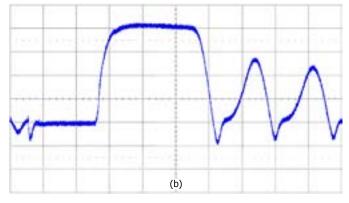

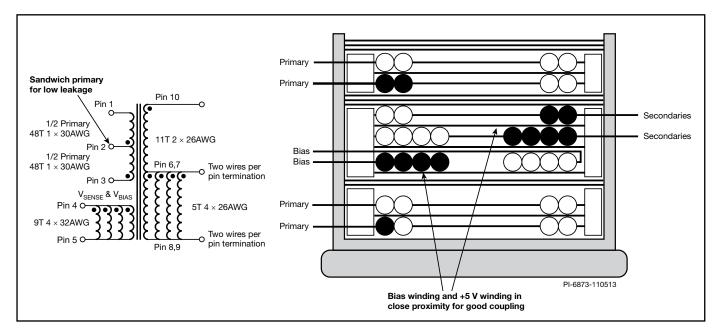

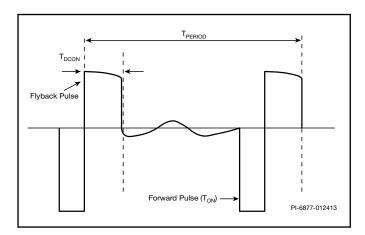

Figure 6. CCM and DCM Operation Waveform.

#### **Switching Frequency**

Typical switching frequency is 132 kHz. (Please refer to LinkSwitch-HP data sheet Figure 5 for explanation of multimode operation).

#### Ripple to Peak Current Ratio, K.

$\rm K_{\rm p}$  is the ratio of ripple to peak primary current. Generally,  $\rm K_{\rm p}\!>\!1$  for DCM (Discontinuous Conduction Mode) operation and  $\rm K_{\rm p}\!<\!1$  for CCM (Continuous Conduction Mode) operation and relates to the primary current waveshape.

DCM operation is not suitable for LinkSwitch-HP based designs due to the requirement that output current is still flowing in the output diode at the time point where the feedback is sampled. Hence there is a  $\rm K_p$  restriction and it is recommended that the  $\rm K_p$  value remains in the range of 0.5 to 0.6 for universal input voltage.

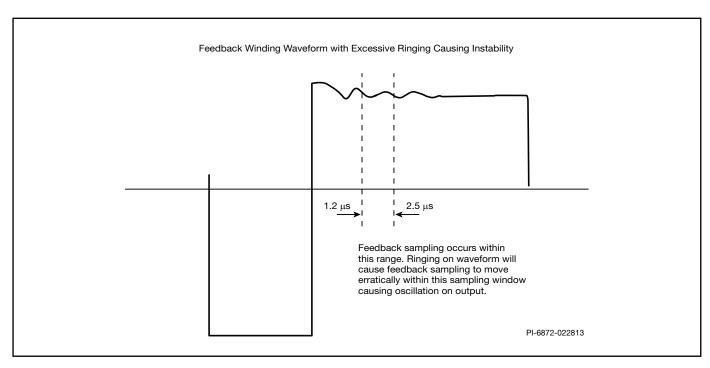

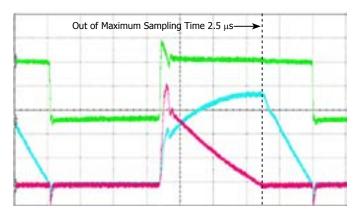

Lower  $K_p$  values leads to larger primary inductance values ( $L_p$ ). This results in a higher number of turns, increasing leakage inductance and reducing allowable cross section of copper that will fit in the bobbin window. Higher  $K_p$  values mean shorter secondary diode conduction times which can approach to 1.2  $\mu s$  which is the minimum sampling time requirement for the device to maintain regulation at no-load. For robust designs  $K_p$  needs to be in the recommended range. Cell D34 and D33 reports the calculated minimum secondary diode conduction time at light load/no-load and full load respectively, for a chosen  $K_p$  and  $V_{OR}$ .

#### Reflected Output Voltage, V<sub>OR</sub> (V)

This parameter is the secondary winding voltage during diode conduction, reflected back to the primary through the turn's ratio of the transformer.

For LinkSwitch-HP based designs, the  $V_{\text{OR}}$  value is restricted by the secondary diode conduction time and maximum duty cycle. Recommended  $V_{\text{OR}}$  values are in the range of 80 V to 125 V.

For design optimization purposes, the following trade-offs should be considered:

- 1. Higher  $V_{OR}$  allows increased power delivery at  $V_{MIN}$ , which minimizes the input capacitance value and maximizes power delivery from a given LinkSwitch-HP device.

- 2. Higher  $V_{OR}$  reduces the voltage stress on the output diodes, which in some cases may allow the use of a lower forward drop Schottky diode for higher efficiency.

- Higher V<sub>OR</sub> can increase leakage inductance and increase clamp losses that reduces efficiency of the power supply and degrades cross regulation in multiple output designs.

- 4. Higher  $V_{\rm OR}$  increases peak and RMS current on the secondary-side, which may increase secondary-side copper and diode losses.

Optimal selection of the  $\rm V_{OR}$  value depends on the specific application and is based on a compromise between the factors mentioned above. For lower voltage outputs (approximately 5 V or multiple output designs) a lower  $\rm V_{OR}$  of approximately 100 V - 110 V is recommended. For higher voltage outputs (12 V and above) a higher  $\rm V_{OR}$  of approximately 110 and 120 V is recommended.

Values below 80 V are not usually recommended. Low  $V_{\text{OR}}$  may cause excessive triggering of the MOSFET self-protection feature during start-up, especially in higher output (>12 V) designs, resulting in an output voltage rise that is not uniform.

| Issue                                                             | Suggested Action                              | Comment                                                         |

|-------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------------------------|

| D34 (minimum diode conduction time at light load/no-load) <1.4 µs | Decrease K <sub>p</sub><br>until D34 >1.4 μs  | 500 ns margin from<br>1.2 μs is desirable.<br>Hence D34 ≥1.7 μs |

| D33 (minimum diode conduction time at full load) <2.7 μs          | Decrease V <sub>OR</sub><br>until D33 >2.7 μs | 500 ns margin from<br>2.5 μs is desirable.<br>Hence D33 ≥3.0 μs |

Table 10. Suggested Actions for  $K_p$  and  $V_{OR}$  Values.

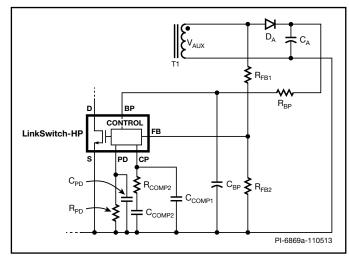

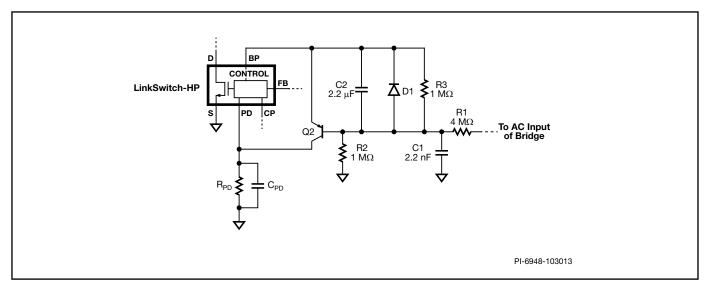

#### Line Sense (VUV<sub>ON</sub>, VUV<sub>OFF</sub>)

$VUV_{ON}$  (undervoltage turn-on) is the desired input line voltage (DC) when the LinkSwitch-HP starts switching during brown-in. This parameter is determined by the turns ratio of bias winding NB to primary winding  $N_p$  and the resistor value  $R_{FB1}$  (Figure 8) which is the top resistor of the feedback resistor divider from bias winding (also feedback sense winding). Typically 100 V is recommended value for universal input range.

By selecting the desired VUV $_{\rm ON}$  threshold the spreadsheet will compute the appropriate value of R $_{\rm FB1}$ . Only VUV $_{\rm ON}$  threshold is selectable. VUV $_{\rm OFF}$  and VOV will be positioned according to VUV $_{\rm ON}$  threshold selection.

| Voltage Sense |  |        |   |                       |

|---------------|--|--------|---|-----------------------|

| VUVON         |  | 102.11 | V | Undervoltage turn on  |

| VUVOFF        |  | 43.19  | V | Undervoltage turn off |

| VOV           |  | 462.09 | V | Overvoltage threshold |

Figure 7. Line Voltage Sense Section of Design Spreadsheet.

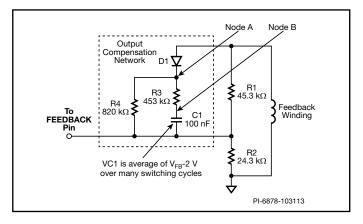

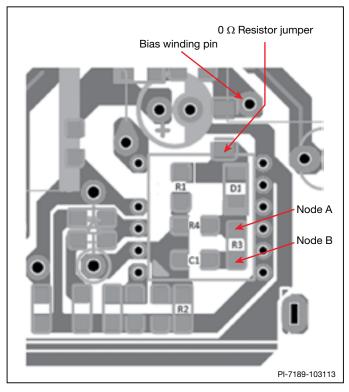

Figure 8. Typical Primary Configuration.

$VUV_{OFF}$  (undervoltage turn-off) is the brown-out voltage threshold below which the LinkSwitch-HP stops switching. This is a fixed ratio to  $VUV_{ON}$ .

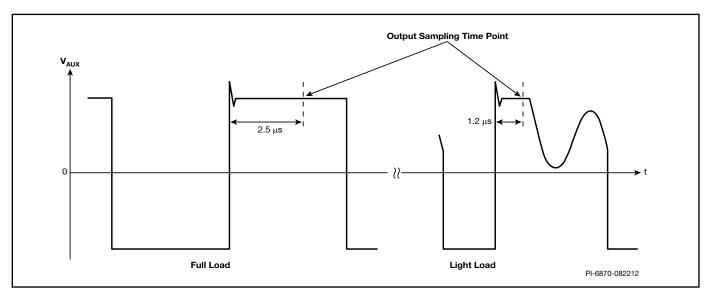

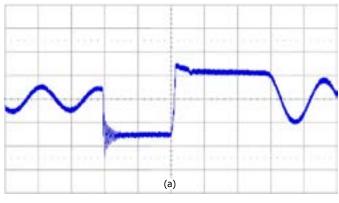

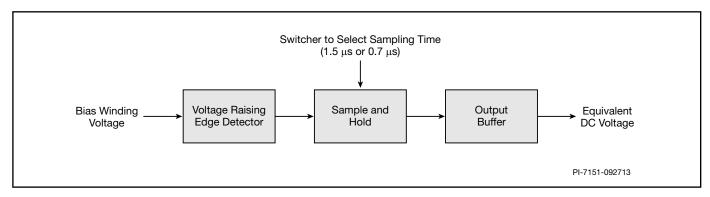

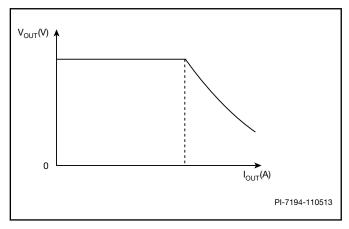

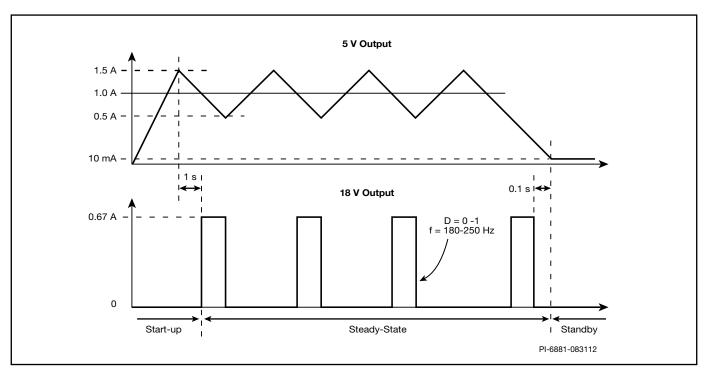

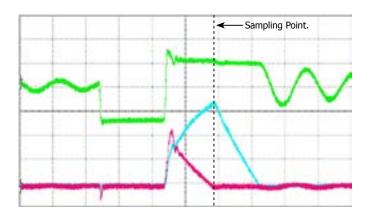

### Minimum Sampling Time Under Light and Heavy Load Conditions

These cells show flyback conduction time (the time period the output diode is conducting) for light and full load conditions. As shown in Figure 10 the sampling time reduces with reducing load. A warning is displayed if the conduction time is too short for either case. The typical sampling time is 1.2  $\mu s$  at no-load or light load, and 2.5  $\mu s$  at full load. TSAMPLE\_LIGHT\_LOAD is adjusted to be 1.4  $\mu s$  and TSAMPLE\_FULL\_LOAD is adjusted to be 2.7  $\mu s$  to cover the possible variable range. Please refer to Table 10 for desirable values of these parameters.

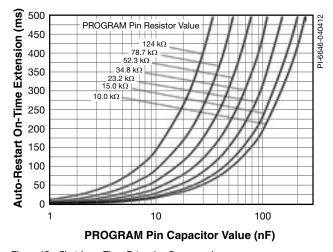

#### Shutdown Delay Capacitor (Cpn)

Desired shutdown delay time (in addition to the standard 35 ms) can be programmed by selecting a delay capacitor ( $C_{PD}$ ) value for a chosen current limit resistor ( $R_{PD}$ ). Resistor  $R_{PD}$  is automatically selected when choosing a KI factor. The total programmed delay is

| FEEDBACK SENSING SECTION |  |       |        |                                  |

|--------------------------|--|-------|--------|----------------------------------|

| RFB1                     |  | 35.70 | k-ohms | Feedback divider upper resistor  |

| RFB2                     |  | 9.09  | k-ohms | Feedback divider lowerr resistor |

Figure 9. Feedback Sense Resistor Values Section of Design Spreadsheet.

Figure 10. Sampling Time.

| <b>ENTER LinkSwitch-HP</b> | VARIABLES |          |       |                                |

|----------------------------|-----------|----------|-------|--------------------------------|

| LinkSwitch-HP              | Auto      | LNK6766E |       | Selected LinkSwitch-HP         |

| ILIMITMIN                  |           | 1.814    | Α     | Minimum Current limit          |

| ILIMITMAX                  |           | 2.087    | Α     | Maximum current limit          |

| ILIMITMIN_EXT              |           | 1.814    | Α     | External Minimum Current limit |

| ILIMITMAX_EXT              |           | 2.087    | Α     | External Maximum current limit |

| KI                         | Auto      | 1.000    | Α     | Current limit reduction factor |

| Rpd                        |           | 124.00   | k-ohm | Program delay Resistor         |

| Cpd                        |           | 33.00    | nF    | Program delay Capacitor        |

| Total programmed delay     |           | 0.86     | sec   | Total program delay            |

Figure 11. Shutdown Delay Section of Design Spreadsheet.

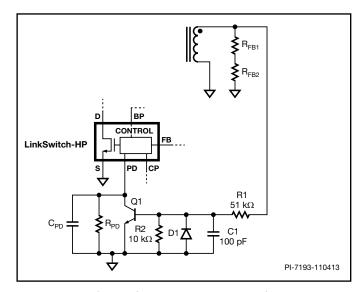

Figure 12. Shutdown Time Extension Programming.

reported in Cell [E37].  $C_{PD}$  also works as a noise filter capacitor for the PROGRAM pin, a recommended capacitor value of 1 nF will be required to pass the surge test for 6 kV.

#### LinkSwitch-HP ON-State Drain to Source Voltage, V<sub>ps</sub> (V)

This parameter is the average ON state voltage developed across the DRAIN and SOURCE pins of LinkSwitch-HP. By default, if the grey override cell is left empty, a value of 4 V is assumed. Use the default value if no better data is available.

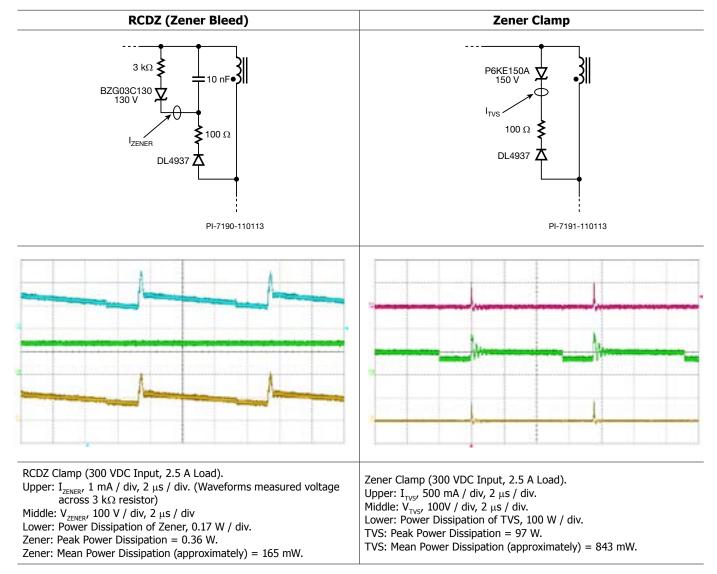

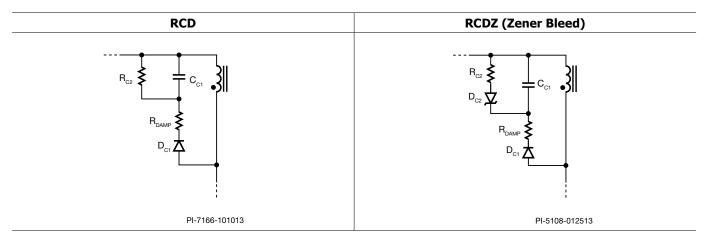

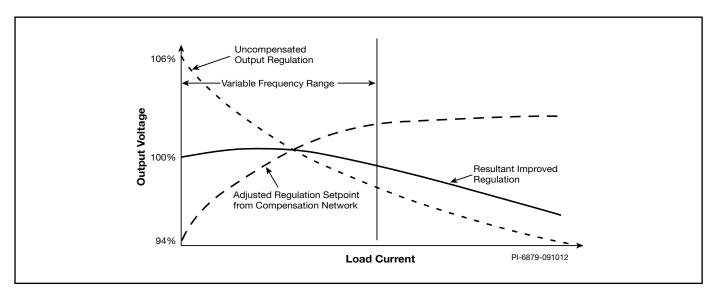

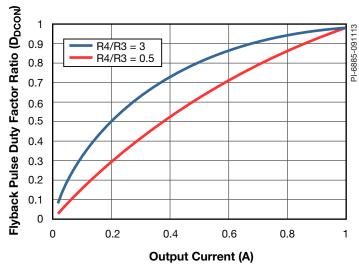

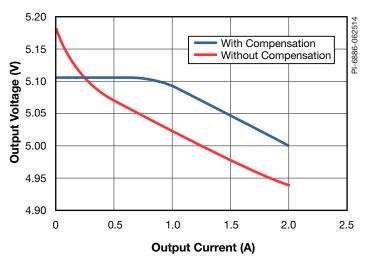

#### Output Diode Forward Voltage Drop, V<sub>D</sub> (V)