# Application Note AN-86 LinkSwitch-XT2 Family

Design Guide

# **Product Highlights**

The LinkSwitch<sup>™</sup>-XT2 IC family combines a high-voltage (725 V or 900 V) power MOSFET switch and an ON/OFF controller into a monolithic IC which is fully fault protected. Auto-restart limits device and circuit dissipation during overload and output short-circuit, over-temperature protection disables switching during thermal faults. Large hysteresis in the thermal protection circuit protects the PCB and surrounding components from experiencing high average temperature during fault conditions. Frequency-jitter reduces EMI by modulating switching frequency. The LinkSwitch-XT2 family is ideal for low-power adapters and chargers as well as auxiliary power for appliances, and to provide power for industrial systems, and metering power. LinkSwitch-XT2based circuits are extremely cost-effective and offer an ideal replacement for linear charger replacement circuits, meeting worldwide standby and efficiency standards such as those described by the California Energy Commission (CEC). LinkSwitch-XT2 ICs can operate without a primary-side clamp circuit (Clampless<sup>™</sup>) for output powers below 2 W (up to 2.5 W with a bias winding) significantly reducing component count. As a replacement for conventional linear and RCC topologies, LinkSwitch-XT2-based designs offer multiple functional benefits.

- Output overvoltage protection (OVP)

- Input overvoltage line protection (OVL)

- Hysteretic over-temperature protection (OTP)

- Extended creepage between DRAIN pin and all other pins to improve field reliability

- 725 V MOSFET rating for excellent surge withstand

- 900 V MOSFET rating series for increased industrial input voltage ranges or extra safety margin

- Extremely low component count

- · Single-sided PCB and full SMD manufacturability

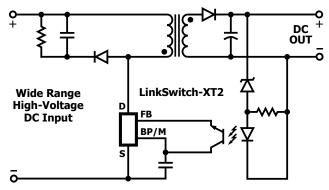

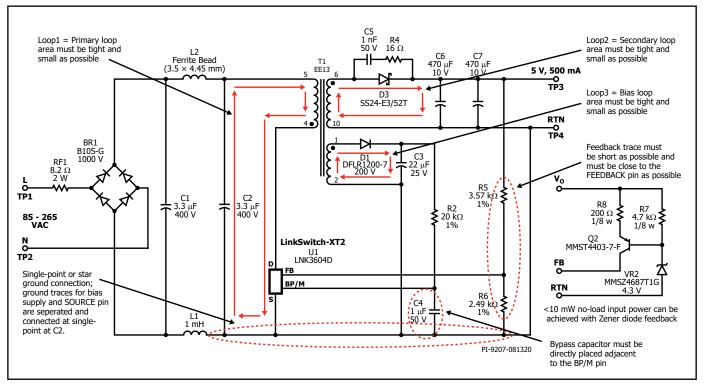

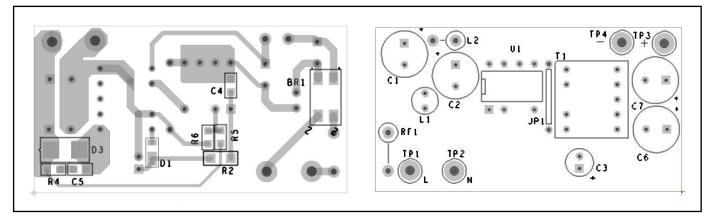

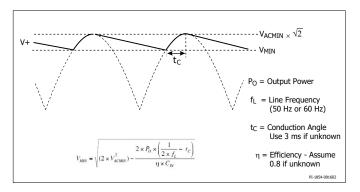

Figure 1. Basic Configuration Using LinkSwitch-XT2 in a Flyback Converter.

# Scope

This application note describes the process of designing an isolated power supply using the LinkSwitch-XT2 family of devices. The objective is to provide power supply engineers with and to enable them to build quickly an efficient, cost-effective flyback converter. Design equations are provided for the selection of key components. To simplify terminology, the application note refers directly to the PIXIs design spreadsheet that is part of the PI Expert<sup>™</sup> design software suite. The basic circuit for LinkSwitch-XT2 power supplies is shown in Figure 1, which also serves as the reference for component identification and is used throughout this application note.

In addition to this application note, the reader may also find the LinkSwitch-XT2 Reference Design Kit (RDK) – containing an engineering prototype board, useful as an example of a complete and fully functional power supply. Further details can be found at www.power.com.

# **Quick Start**

Readers familiar with power supply design and Power Integrations design software may elect to skip the step-by-step design approach described later, and can use the following information to quickly design the transformer and select the components for a first prototype. For this approach, only the information described below needs to be entered into the PIXIs spreadsheet, other parameters will be automatically selected based on a typical design. The spreadsheet below is for LNK3604 XT2 Variant.

- Enter AC input voltage range VACMIN, VACMAX and minimum line frequency fL

- Enter Time\_Bridge\_Conduction estimate

- The conduction time, is usually set at 2.66 ms and can be verified by direct measurement.

- Enter nominal output voltage VOUT

- Enter continuous output current IOUT

- Enter estimated efficiency, η

- 0.8 for universal input voltage (85-265 VAC) or single 100/115 VAC (85-132 VAC) and 0.85 for a single 230 VAC (185-265 VAC) design. Adjust the number accordingly after measuring the efficiency of the first prototype board at peak load and VACMIN.

- Enter loss allocation factor

- 0.5 for typical application. Adjust the number accordingly after the first prototype-board evaluation.

- Enter input capacitance

- 2-3 μF/W for universal (85-265 VAC) or single 100/115 VAC (85-132 VAC) line input.

- $1 \mu$ F/W for single 230 VAC (185-265 VAC) line input

- Select the type of Feedback configuration

- Choose between Opto for isolated converter or Bias winding for non-isolated converter.

- Select Yes if a bias winding is required

- Select configuration for current limit mode

- Two current limit configurations are available, REDUCED, STANDARD.

- Enter the desired reflected output voltage, VOR

- A good starting value for VOR is to set within the range of 90 V – 110 V.

- Enter the on-state Drain to Source Voltage, VDSON

- The default value given is 10 V. If no available value given in MOSFET datasheet, typical setting of VDSON during on-state is 10 V.

- Enter Primary Inductance Tolerance, LPRIMARY\_TOL

- The default value given is 10%. If no available data from the supplier, typical setting is 10% to ensure manufacturability of the transformer.

- Enter the Output Winding Diode Forward Voltage Drop, VF\_SECONDARY

- VF\_SECONDARY is typically set at 0.7 V.

- Enter core type (if desired),.

- Suggested core size will be selected automatically if none is entered

- AE, LE, AL, BW are automatically reflected based on the selected core type.

- For custom core, enter the core parameters

- Enter the desired safety margin, MARGIN

- The default margin in the spreadsheet is 0 mm, assuming that a triple insulated wire will be used for secondary windings.

- If triple insulated wire is not used at the secondary winding, the value that should be entered for safety margin M is 3.1 mm. This is the typical margin for universal input (85 – 265 VAC).

- Enter number of primary layers (if desired), LAYERS\_ PRIMARY

- The default number of primary layers reflected in the spreadsheet is 3.

- Enter the Primary winding wire AWG, AWG\_PRIMARY

- The value recommended is based on the given/calculated primary current. If desired to alter the value other parameters and ensure that no warnings are generated.

- Enter secondary number of turns, NSECONDARY

If the grey override cell is left blank, the spreadsheet will

- If the grey overhoe cell is left blank, the spreadsheet will automatically calculate the secondary number of turns.

Enter the desired Bias Turns NBIAS

- Enter the desired Bias Turns , NBIAS

- Typically, the default value in the spreadsheet will give a 22 V Bias winding voltage as this gives the optimized performance on OVP setting.

- Enter Bias Winding Diode Forward Voltage Drop, VF\_BIAS

Typically set at 0.7 V.

### For multiple outputs design enter the following requirements under Transformer Secondary Design Parameters (Multiple Outputs):

# 1st Output

(If unused, the defaults are from the single output design)

Enter the Main Output Voltage, VOUT1

# 2nd Output

- (If unused, leaved the section blank)

- Enter the 2nd Output Voltage, VOUT2

- Enter the 2nd Output DC Current, IOUT2

- Enter the output diode voltage drop for the 2nd output, VD2

# A 3rd output may be added if desired.

#### If any warnings are generated, make changes to the design by following instructions in spreadsheet.

- Build transformer as suggested in "Transformer Construction" tab

- Select key components

- Build prototype and iterate design as necessary, entering measured values into spreadsheet where estimates were used (e.g. efficiency, VMIN). Note that the initial efficiency estimate is very conservative.

# **Output Power Table**

|                              | Peak or Open Frame <sup>1,2</sup> |            |  |  |  |  |

|------------------------------|-----------------------------------|------------|--|--|--|--|

| Poducts <sup>3</sup>         | 725 V MOSFET                      |            |  |  |  |  |

|                              | 230 VAC ±15% 85-265 VAC           |            |  |  |  |  |

| LNK3604P/G/D                 | 9.2 W 6.1 W                       |            |  |  |  |  |

| Due de sta?                  | 900 V MOSFET                      |            |  |  |  |  |

| <b>Products</b> <sup>3</sup> | 230 VAC ±15%                      | 85-265 VAC |  |  |  |  |

| LNK3694P/G/D                 | 6 W                               | 4 W        |  |  |  |  |

| LNK3696P/G/D                 | 11 W                              | 8 W        |  |  |  |  |

|                              | 1                                 | 1          |  |  |  |  |

Table 1. Output Power Table.

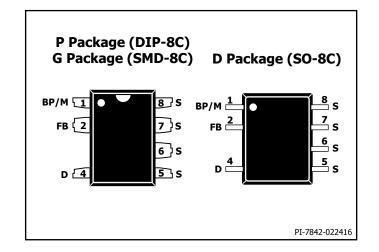

- Notes: 1. Maximum continuous power in a typical non-ventilated enclosed adapter measured at 50 °C ambient.

- Maximum practical continuous power in an open frame design with adequate heat sinking, measured at 50 °C ambient. Packages: P: DIP-8C, G: SMD-8C, D: SO-8C.

- 3.

# Step-by-Step Design Procedure

# Step 1 – Enter Application Variables $VAC_{MIN'} VAC_{MAX'} f_{L'}$

V<sub>o</sub>, I<sub>o</sub>, ղ, C<sub>IN</sub>

| ENTER APPLICATION VARIABLES |        |           |          |                                                                                     |

|-----------------------------|--------|-----------|----------|-------------------------------------------------------------------------------------|

| LINE VOLTAGE RANGE          |        | UNIVERSAL |          | AC line voltage range                                                               |

| VACMIN                      | 85.00  | 85.00     | Volts    | Minimum AC line voltage                                                             |

| VACTYP                      |        | 115.00    | Volts    | Typical AC line voltage                                                             |

| VACMAX                      | 265.00 | 265.00    | Volts    | Maximum AC line voltage                                                             |

| fL                          | 50     | 50        | Hertz    | AC mains frequency                                                                  |

| TIME_BRIDGE_CONDUCTION      | 2.90   | 2.90      | mseconds | Input bridge rectifier diode conduction time                                        |

| LINE RECTIFICATION          | F      | F         |          | Select 'F'ull wave rectification or 'H'alf wave rectification                       |

| VOUT                        | 5      | 5         | Volts    | Output voltage                                                                      |

| IOUT                        | 0.5    | 0.5       | Amperes  | Average output current specification                                                |

| CC THRESHOLD VOLTAGE        | 0.00   | 0.00      | Volts    | Voltage drop across the sense resistor                                              |

| OUTPUT CABLE RESISTANCE     | 0.00   | 0.00      | Ohms     | Enter the resistance of the output cable (if used)                                  |

| EFFICIENCY                  | 0.70   | 0.70      |          | Efficiency Estimate at output terminals. Under 0.8 if no better<br>data available   |

| LOSS ALLOCATION FACTOR      | 0.50   | 0.50      |          | The ratio of power losses during the MOSFET off-state to the<br>total system losses |

| POUT                        |        | 2         | Watts    | Continuous Output Power                                                             |

| CIN                         | 6.60   | 6.60      | uFarads  | Input capacitor                                                                     |

| VMIN                        |        | 91.16     | Volts    | Valley of the rectified VACMIN                                                      |

| VMAX                        |        | 374.77    | Volts    | Peak of the VACMAX                                                                  |

| FEEDBACK                    | OPTO   | OPTO      |          | Select the type of feedback required                                                |

| BIAS WINDING                | YES    | YES       |          | Select whether a bias winding is required                                           |

Table 2. Application Variable Section of LinkSwitch-XT2 Design Spreadsheet.

#### Input Voltage

Determine the input voltage range from Table 3.

| Nominal Input Voltage (VAC) | VAC <sub>MIN</sub> | VAC <sub>MAX</sub> |

|-----------------------------|--------------------|--------------------|

| 100/115                     | 85                 | 132                |

| 230                         | 195                | 265                |

| Universal                   | 85                 | 265                |

Table 3. Standard Worldwide Input Line Voltage Ranges.

# Line Frequency, $f_L$

Select 50 Hz for universal or single line 100 VAC, 60 Hz for single line 115 VAC input. 50 Hz for single 230 VAC input. These values represent typical line frequencies which most applications this gives adequate overall design margin. For absolute worst-case conditions, assume a line frequency tolerance of  $\pm 6\%$ .

# Output Voltage, V<sub>out</sub> (V)

Enter the nominal output voltage of the main output during the continuous load condition. Generally, the main output is the output from which feedback is derived. For CV/CC designs this should be the typical output voltage at the nominal peak power point in the output characteristic. For CV only outputs, this should be the specified output voltage. For designs with an output cable, enter the voltages at the load.

# Output Current, I<sub>out</sub> (A)

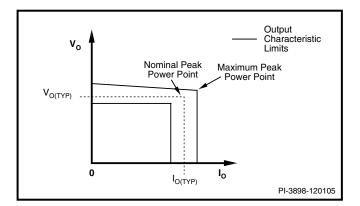

Enter the output current from the power supply. For CV/CC designs this should be the maximum output current at the maximum peak-power point in the output characteristic (see Figure 2). For CV only outputs, this should be the maximum output current. In multiple output designs the output power of the main output (typically the output from which feedback is taken) should be increased such that the maximum continuous output power from the main output

Figure 2. Diagram Showing Correct Values of IO and VO to Enter for CV/CC Designs.

matches the combined output power from all the outputs. The individual output voltages and currents should then be entered at the bottom of the spreadsheet.

#### CC Threshold Voltage (V)

For CV only designs, this is not applicable; enter 0. For CV/CC designs, this is the expected voltage developed across the current sense resistor at the nominal CC point. Typically, this value is in the range of 0.3 V to 1.3 V, depending on the specific circuit used. For designs using the V\_BE of a bipolar transistor ( $\sim 0.65$  V) as the CC reference voltage, to maintain CC control, the optocoupler LED has to stay forward biased. This may require an additional resistor to be added in series with the CC sense resistor to increase the overall voltage drop ( $> \sim 1.1$  V). It is this overall voltage drop that should be entered as the CC threshold. For the exact forward drop of the optocoupler LED, consult the manufacturer's data sheet.

# Output Cable Resistance ( $\Omega$ )

Enter the output cable resistance. If there is no output cable enter 0. This parameter is used as part of the total output power calculation.

# Power Supply Efficiency, $\eta$

This is the complete power supply efficiency measured at the point of load, therefore including any CC sense and cable losses. For a CV/CC design with a nominal peak power point at a voltage of 5.5 V and current of 0.5 A, use a value of 0.57. Use a value of 0.64 for a 5.5 V CV only design if no better data is available, or until measurements can be made on a prototype.

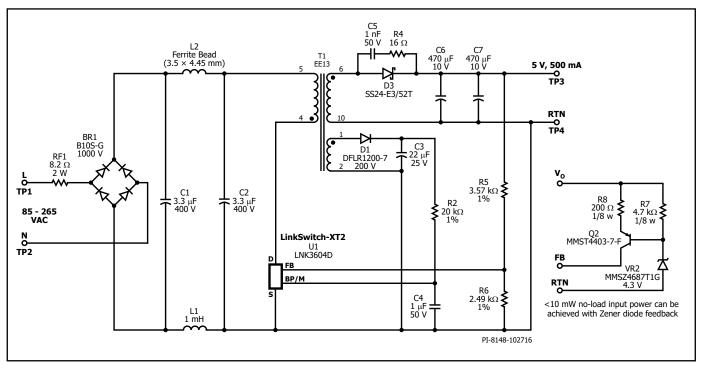

# Bridge Diode Conduction Time, $t_c$ (ms)

Enter the bridge diode conduction time. Use 2.66 ms if no other data is available or until a measurement can be made on a prototype.

#### **Power Supply Loss Allocation Factor**

This factor represents the proportion of losses between the primary and the secondary of the power supply.

If no better data is available then the following values are recommended:

$$Z = \frac{\text{Secondary Losses}}{\text{Total Losses}}$$

• Bias winding feedback designs (CV): 0.5

- Optocoupler CV feedback: 0.5

- Optocoupler CV and CC feedback: 0.75

# Total Input Capacitance, $C_{IN}$ (µF)

Enter total input capacitance using Table 4 for guidance. The capacitance is used to calculate the minimum and maximum DC voltage across the bulk capacitor and should be selected to keep the minimum DC input voltage,  $V_{\text{MIN}} > 50$  V, and ideally  $V_{\text{MIN}} > 70$  V.

|                           | Total Input Capacitance per Watt<br>Output Power μF/W |                            |  |  |  |  |  |

|---------------------------|-------------------------------------------------------|----------------------------|--|--|--|--|--|

| AC Input Voltage<br>(VAC) | Full-Wave<br>Rectification                            | Half-Wave<br>Rectification |  |  |  |  |  |

| 100/115                   | 2                                                     | 4-5                        |  |  |  |  |  |

| 230                       | 1                                                     | 1-2                        |  |  |  |  |  |

| 86-265                    | 2                                                     | 4-5                        |  |  |  |  |  |

Table 4. Suggested Total Input Capacitance for Different Input Voltage Ranges

# Enter Feedback, Bias type and Clamp information

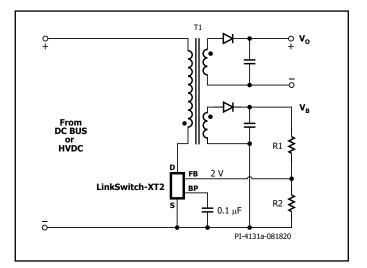

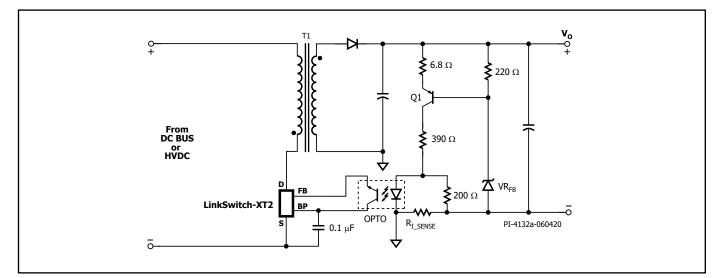

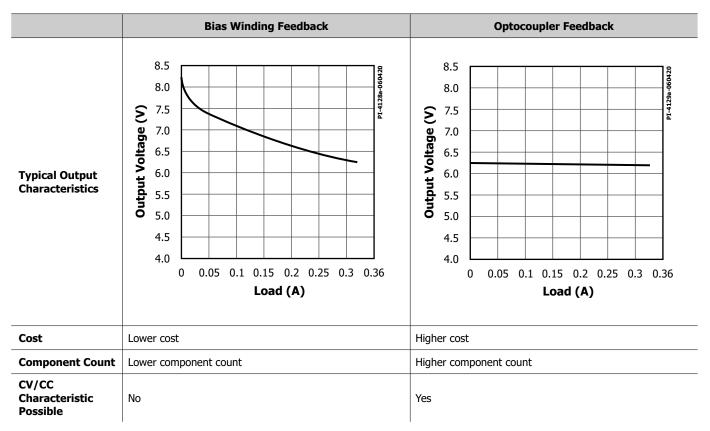

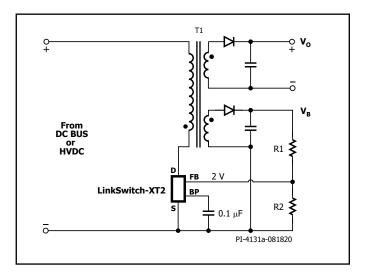

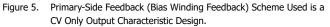

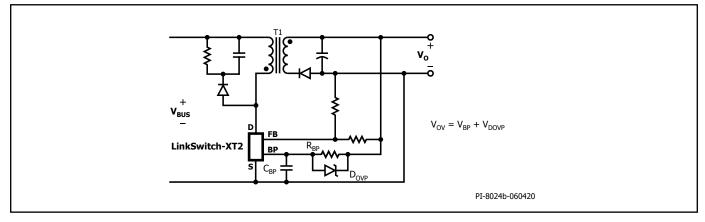

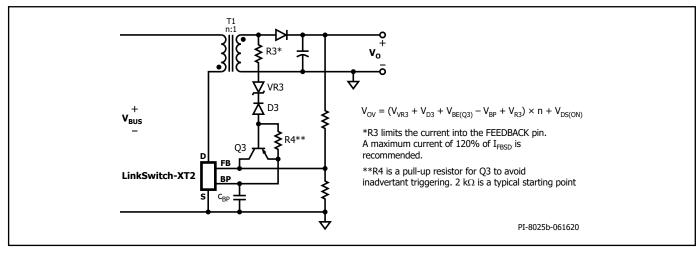

Select between either bias winding feedback (primary-side feedback), Figure 3, or optocoupler feedback (secondary-side feedback), Figure 4. Bias winding makes use of a primary- side auxiliary winding to set the output voltage. Optocoupler feedback directly senses the output voltage and can provide any level of accuracy depending on the voltage reference selected. Secondary-side feedback also allows for a CV/CC output characteristic. See Table 5 for a summary of feedback types.

Figure 3. Primary-Side Feedback (Bias Winding Feedback) Scheme Used in a CV Only Output

Figure 4. Secondary-Side Feedback Scheme used for a CV/CC Output Characteristic Design.

Table 5. Summary of Comparison Between Bias Winding Feedback and Optocoupler Feedback.

Figure 1 shows a CV only optocoupler design, Table 6 provides guidance for component selection for both CV and CV/CC configurations. Figure 3 shows a CV only bias winding configuration.

| Output Type           | CV/CC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CV Only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Suggested<br>Feedback | $\begin{array}{c} & & & & \\ & & & \\ & & & \\ & & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ &$ | U <sub>FB</sub><br>(4.3 V)<br>(100 Ω)<br>(100 Ω)<br>(100 Ω)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D)<br>(PC817D) |

| Notes                 | $\begin{array}{l} R_{\text{SENSE}} \colon V_{\text{F(UFB}}/I_{\text{O}} \\ \text{VR}_{\text{FB}} \colon V_{\text{O-VBE}(\text{QFB})} (\text{Use a Zener with a low } I_{\text{ZT}} \text{ such as} \\ \text{the BZX79 series}) \\ R_{\text{S}} \colon V_{\text{BE}(\text{QFB})}/I_{\text{ZT(VRFB})} \\ R_{\text{A}} \colon \text{Limits base-emitter current of } Q_{\text{FB}}, R_{\text{C}} \text{ and } R_{\text{D}} \\ \text{Limits } U_{\text{FB}} \text{ current} \\ U_{\text{FB}} \colon \text{Use high CTR device (200\% - 600\%)} \\ Q_{\text{FB}} \colon \text{Any samll signal PNP transistor (Values shown for a 5.5 V, 500 mA output)} \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $ \begin{array}{l} VR_{FB}: \ V_{o}\text{-}V_{F(UFB)} \ (\text{Use a Zener with a low } I_{ZT} \ \text{such as the} \\ BZX79 \ series) \\ R_{B}: \ \ V_{F(UFB)}/I_{ZT(VRFB)} \\ R_{A}: \ \ \text{Limits} \ \ U_{FB} \ \text{current during transients and allows} \\ \text{small output voltage adjustments} \\ U_{FB}: \ \ \text{Use high CTR device } (200\% - 600\%) \\ L_{A}: \ \ \text{Optional for lower output switching noise (Use} \\ \text{ferrite bead or low value } (1\text{-}3 \ \mu\text{H}) \ \text{inductor rated} \\ \text{for } I_{O}) \\ C_{A}: \ \ \text{Optional for lower output switching noise (Use} \\ \text{low ESR, 100 } \mu\text{F with voltage rating } >1.25 \times V_{O}) \\ (\text{Values shown are for a 5 V output)} \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Table 6. Example of Feedback Configurations.

If optocoupler feedback is selected, the user still has the option to use a bias winding. It may be used to externally power the Link-Switch-XT2 device for lower no-load consumption. In addition, the bias winding can be configured as a shield for reduced EMI.

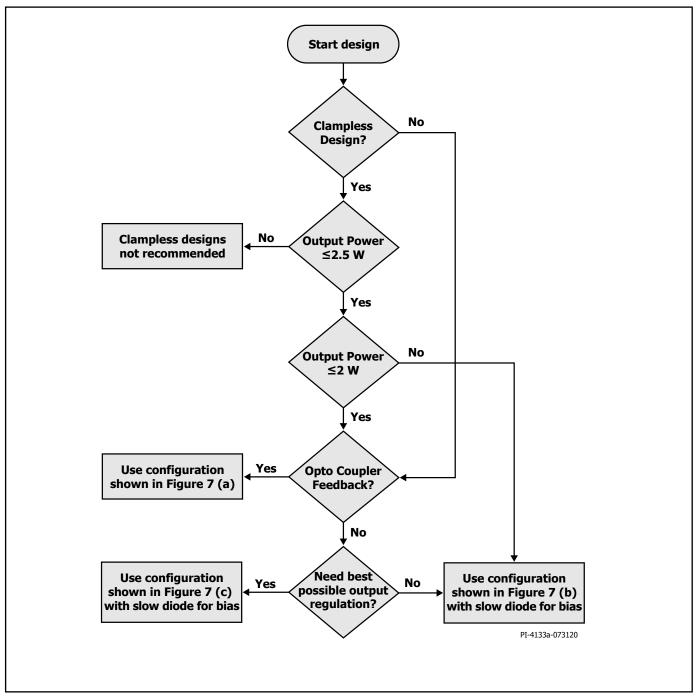

Designs below 2.5 W output power may be able to eliminate the primary-side clamp circuit. Clampless circuits offer the benefit of low cost and component count, but these circuits rely on specific transformer construction techniques. See the section on transformer construction for details.

For designs greater than 2.5 W, a Clampless solution is not recommended. See the section on clamp design for details.

All the variables described above can be entered in the "Enter Application variables" section of the LinkSwitch-XT2 design spreadsheet in PI XIs design software (see Table 2).

# Step 2 – Enter LinkSwitch-XT2 Variables

To select the correct LinkSwitch-XT2 device, refer to the LinkSwitch-XT2 data sheet power table and select based on the input voltage, enclosure type and output power of the design.

| LINKSWITCH-XT2 VARIABLES |         |          |         |                                                                               |

|--------------------------|---------|----------|---------|-------------------------------------------------------------------------------|

| CURRENT LIMIT MODE       | RED     | RED      |         | Pick between RED(Reduced) or STD(Standard) current limit mode of<br>operation |

| PACKAGE                  | SO-8C   | SO-8C    |         | Device package                                                                |

| ENCLOSURE                | Adapter | Adapter  |         | Pick the device enclosure                                                     |

| GENERIC DEVICE           |         | LNK3604  |         | Device series                                                                 |

| DEVICE CODE              |         | LNK3604D |         | Device code                                                                   |

| PMAX                     |         | 3.60     | Watts   | Device maximum power capability                                               |

| VOR                      | 77      | 77       | Volts   | Voltage reflected to the primary winding when the MOSFET is off               |

| VDSON                    |         | 10.0     | Volts   | MOSFET on-time drain to source voltage                                        |

| VDSOFF                   |         | 556.5    | Volts   | Estimated MOSFET off-time drain to source voltage                             |

| ILIMITMIN                |         | 0.180    | Amperes | Minimum current limit                                                         |

| ILIMITTYP                |         | 0.205    | Amperes | Typical current limit                                                         |

| ILIMITMAX                |         | 0.230    | Amperes | Maximum current limit                                                         |

| FSMIN                    |         | 124000   | Hertz   | Minimum switching frequency                                                   |

| FSTYP                    |         | 132000   | Hertz   | Typical switching frequency                                                   |

| FSMAX                    |         | 140000   | Hertz   | Maximum switching frequency                                                   |

| RDSON                    |         | 44.20    | Ohms    | MOSFET drain to source resistance                                             |

Table 7. Linkswitch-XT2 Variables

#### **Current Limit**

The value of the BYPASS/MULTI-FUNCTION pin capacitor determines the device current limit setting. LinkSwitch-XT2 allows the internal current limit to be selected between two levels, Standard Current Limit and Reduced Current Limit. The choice can be selected in the spreadsheet by entering RED or STD.

Selecting the correct current limit level depends on the thermal environment, the amount of board area or use of an external heatsink, and the average output power. Selecting RED gives the lowest current limit and results in lowest device dissipation. This minimizes heatsinking needed even in high ambient conditions. An example where RED would be selected is in a sealed adapter with minimal heat sinking.

Selecting STD gives the highest current limit and therefore maximum power from a given device. This is ideal for open frame designs, adapters where an external heatsink is attached to the SOURCE pins of the device.

Selecting STD is optimum for most applications, balancing heat dissipation and system efficiency.

| PRIMARY WAVEFORM PARAMETERS |   |       |          |                                                       |

|-----------------------------|---|-------|----------|-------------------------------------------------------|

| MODE OF OPERATION           |   | CCM   |          | Mode of operation                                     |

| KRP/KDP                     |   | 0.935 |          | Measure of continuous/discontinuous mode of operation |

| KP_TRANSIENT                |   | 0.536 |          | KP under conditions of a transient                    |

| DMAX                        |   | 0.516 |          | Maximum duty cycle                                    |

| TIME_ON                     |   | 4.161 | useconds | MOSFET conduction time at the minimum line voltage    |

| TIME_ON_MIN                 |   | 0.828 | useconds | MOSFET conduction time at the maximum line voltage    |

| IAVG_PRIMARY                |   | 0.049 | Amperes  | Average input current                                 |

| IRMS_PRIMARY                |   | 0.077 | Amperes  | Root mean squared value of the primary current        |

| LPRIMARY_MIN                |   | 1518  | uH       | Minimum primary inductance                            |

| LPRIMARY_TYP                |   | 1632  | uH       | Typical primary inductance                            |

| LPRIMARY_MAX                |   | 1476  | uH       | Maximum primary inductance                            |

| LPRIMARY_TOL                | 7 | 7     |          | Primary inductance tolerance                          |

#### Table 8. Primary Waveform Parameters

| SECONDARY WAVEFORM PARAMETERS |  |       |         |                                                  |

|-------------------------------|--|-------|---------|--------------------------------------------------|

| IPEAK_SECONDARY               |  | 3.118 | Amperes | Peak secondary current                           |

| IRMS_SECONDARY                |  | 1.295 | Amperes | Root mean squared value of the secondary current |

|                               |  |       |         | Peak inverse voltage on the secondary diode, not |

| PIV_SECONDARY                 |  | 32.65 | Volts   | including the leakage spike                      |

| VF_SECONDARY                  |  | 0.7   | Volts   | Secondary diode forward voltage drop             |

Table 9. Secondary Waveform Parameters

# Reflected Output Voltage, V<sub>or</sub> (V)

This parameter is the secondary winding voltage reflected back to the primary through the turns ratio of the transformer (during the conduction time of the output diode). The default value is 100 V, however this can be increased up to 185 V to achieve the maximum power capability from the selected LinkSwitch-XT2 device. In general, start with the default value of 100 V, increasing the value when necessary to maintain KP above its lower limit of 0.6. For Clampless designs, there is less flexibility in selecting the value of VOR. Increasing VOR directly increases the peak Drain voltage. Therefore, for Clampless designs, a value of  $\leq 90$  V should be used and only increased once the peak Drain voltage has been measured and adequate margin (< = 90%) to BVDSS determined.

LinkSwitch-XT2 On-State DRAIN to SOURCE Voltage,  $V_{\text{DSON}}$  (V)

This parameter is the average on-state voltage developed across the DRAIN and SOURCE pins of LinkSwitch-XT2. By default, if the gray override cell is left empty, a value of 10 V is assumed. Use the default value if no better data is available.

Secondary Diode Forward Voltage Drop,  $V_{F(SECONDARY)}$  (V) Enter the average forward voltage drop of the (main) output diode. Use 0.5 V for a Schottky diode or 1 V for a ultrafast diode if no better data is available. By default, a value of 0.7 V is assumed.

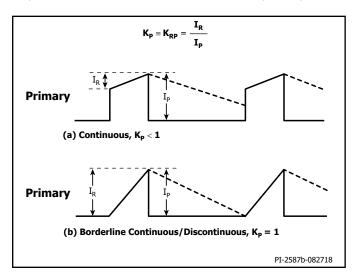

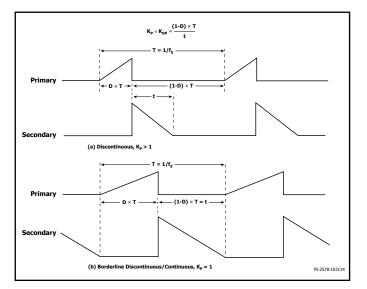

# Calculated Ripple to Peak Current Ratio, $\mathrm{K}_{\mathrm{P}}$

Below a value of 1, indicating continuous conduction mode,  $K_p$  is the ratio of ripple to peak primary current ( $K_{pp}$ ). Above a value of 1, indicating discontinuous conduction mode, KP is the ratio of primary MOSFET off-time to the secondary diode conduction time ( $K_{pp}$ ). The value of  $K_p$  should be in the range of 0.6 <  $K_p$  < 6 and guidance is given in the comments cell if the value is outside this range. A value above 1 will typically result in lower noise, discontinuous conduction mode at 115 VAC, where EMI measurements are made.

Variables referenced in Step 2 are found in the "LinkSwitch-XT2 Variables, Primary Waveform Parameters and Secondary Waveform Parameters" section of the spreadsheet (see Table 7 to Table 9).

# Step 3 – Transformer Construction Parameters

Core Effective Cross-Sectional Area, Ae (mm<sup>2</sup>)

Core Effective Path Length, Le (mm), Core Ungapped

Effective Inductance, AL (nH/turns<sup>2</sup>)

Volume of the Core, Ve (mm<sup>3</sup>)

Window area of the Bobbin, AW (mm)

Width of the Bobbin, BW (mm)

Mean Length per turn of the Bobbin, MLT (mm)

| TRANSFORMER CONSTRUCTION PARAMETERS |      |          |              |                                            |

|-------------------------------------|------|----------|--------------|--------------------------------------------|

| Core selection                      |      |          |              |                                            |

| CORE                                | EE13 | EE13     |              | Select the transformer core                |

| BOBBIN                              |      | B-EE13-H |              | Bobbin name                                |

| AE                                  | 17   | 17       | mm^2         | Cross sectional area of the core           |

| LE                                  |      | 30.2     | mm           | Effective magnetic path length of the core |

| AL                                  |      | 1130.0   | nH/(turns^2) | Ungapped effective inductance of the core  |

| VE                                  |      | 517.0    | mm^3         | Volume of the core                         |

| AW                                  |      | 21.90    | mm^2         | Window area of the bobbin                  |

| BW                                  | 7.9  | 7.9      | mm           | Width of the bobbin                        |

| MLT                                 |      | 0.00     | mm           | Mean length per turn of the bobbin         |

| MARGIN                              | 0.00 | 0.00     | mm           | Safety margin                              |

Table 10. Transformer Construction Parameters

By default, if the Core Type cell is left empty, the spreadsheet will select the EE13 core. The user can change this selection and choose an alternate core from a list of commonly available cores suitable for the output power (see Table 10). Changes to these values will change the power capability of a given core size, therefore Table 11 should be used for guidance only.

The gray override cells can be used to enter the core and bobbin parameters directly. This is useful if a core is selected that is not on the list or the specific core or bobbin information differs from that recalled by the spreadsheet.

# Safety Margin, MARGIN (mm)

For designs that require isolation but are not using triple insulated wire for the secondary winding, the width of the safety margin to be used on each side of the bobbin should be entered here. Typically, for universal input designs, a total margin of 6.2 mm would be required; therefore a value of 3.1 mm would be entered into the spreadsheet. For vertical bobbins, the margin may not be symmetrical however, the total margin divided by 2 should still be entered.

As the margin reduces the available area for the windings, margin construction may not be suitable for small core sizes. If after entering the margin, more than 4 primary layers (L) are required, it is suggested that either a larger core be selected or switch to a zero margin design using triple insulated wire for the secondary winding.

| Core Size | Suggested Power Range |              |  |  |  |

|-----------|-----------------------|--------------|--|--|--|

|           | 100/115 or 85-265 VAC | 230 VAC Only |  |  |  |

| EE8       | <1W                   | <1W          |  |  |  |

| EE10      | <2W                   | <2W          |  |  |  |

| EE13      | <4W                   | <4W          |  |  |  |

| EE16      | <5W                   | <6W          |  |  |  |

| EE19      | <5.6W                 | <7.1W        |  |  |  |

| EE22      | <6W                   | <8W          |  |  |  |

| EE25      | <6W                   | <9W          |  |  |  |

Table 11. Commonly Available Cores and Power Levels at Which Cores Can be used for Typical Designs.

| PRIMARY WINDING      |   |       |               |                                                        |

|----------------------|---|-------|---------------|--------------------------------------------------------|

| NPRIMARY             |   | 122   |               | PrImary number of turns                                |

| BMAX_TARGET          |   | 1500  | Gauss         | Target value of the magnetic flux density              |

| BMAX_ACTUAL          |   | 1810  | Gauss         | Actual value of the magnetic flux density              |

| BAC                  |   | 846   | Gauss         | AC flux density                                        |

| ALG                  |   | 110   | nH/T^2        | Gapped core effective inductance                       |

| LG                   |   | 0.176 | mm            | Core gap length                                        |

| LAYERS_PRIMARY       | 2 | 2     |               | Number of primary layers                               |

| AWG_PRIMARY          |   | 38    |               | Primary winding wire AWG                               |

| OD_PRIMARY_INSULATED |   | 0.125 | mm            | Primary winding wire outer diameter with insulation    |

| OD_PRIMARY_BARE      |   | 0.101 | mm            | Primary winding wire outer diameter without insulation |

| CMA_PRIMARY          |   | 204   | mil^2/Amperes | Primary winding wire CMA                               |

Table 12. Primary Winding Parameters.

# Actual Maximum Operating Flux Density, BMAX\_ACTUAL (Gauss)

The cycle skipping mode of operation used in LinkSwitch-XT2 can generate audio frequency components in the transformer. To limit this audible noise generation the transformer should be designed such that the peak core flux density is below 1500 Gauss (150 mT). Following this guideline, and using the standard transformer production technique of dip varnishing, practically eliminates audible noise. Vacuum impregnation of the transformer should not be used due to the high primary capacitance and increased losses that result

Higher flux densities are possible, however careful evaluation of the audible noise performance should be made using production transformer samples before approving the design. Audible noise may also be created by ceramic capacitors that use dielectrics such as

Z5U, when used in clamp circuits may also generate audio noise. If this is the case, try replacing them with a capacitor having a different dielectric, for example a film type. Flux densities above 3000 Gauss (300 mT) are not recommended

#### Primary Layers, Layers\_Primary

By default, if the override cell is empty, a value of 3 is assumed. Primary layers should be in the range of 1 < L < 4, and in general it should be the lowest number that meets the primary current density limit (CMA) of 200 Cmils/Amp. Values above 4 layers are possible, but the increased leakage inductance and physical fit of the windings should be considered.

For Clampless designs without a bias winding, 2 primary layers must be used. This is to ensure sufficient primary capacitance to limit the peak Drain voltage below the BVDSS rating of the internal MOSFET.

| SECONDARY WINDING      |   |       |               |                                                          |

|------------------------|---|-------|---------------|----------------------------------------------------------|

| NSECONDARY             | 9 | 9     |               | Secondary turns                                          |

| AWG_SECONDARY          |   | 26    |               | Secondary winding wire AWG                               |

| OD_SECONDARY_INSULATED |   | 0.76  | mm            | Secondary winding wire outer diameter with insulation    |

| OD_SECONDARY_BARE      |   | 0.455 | mm            | Secondary winding wire outer diameter without insulation |

| CMA_SECONDARY          |   | 247   | mil^2/Amperes | Secondary winding CMA                                    |

Table 13. Secondary Winding Parameters.

# Secondary Turns, N<sub>SECONDARY</sub>

By default, if the grey override cell is left blank, the minimum number of secondary turns is calculated such that the maximum operating flux density, BM, is kept below the recommended maximum. In general, it is not necessary to enter a number in the override cell except in designs where a higher operating flux density is acceptable (see Minimizing Audible Nose section for an explanation of BM limits).

| BIAS WINDING |      |       |       |                                        |

|--------------|------|-------|-------|----------------------------------------|

| NBIAS        | 20   | 20    |       | Bias turns                             |

| VF_BIAS      | 0.50 | 0.50  | Volts | Bias diode forward voltage drop        |

| VBIAS        |      | 12.67 | Volts | Bias winding voltage                   |

| PIVB         |      | 74.10 | Volts | Peak inverse voltage on the bias diode |

| CBP          |      | 1.0   | uF    | BP pin capacitor                       |

Table 14. Bias Winding Parameters.

the gray override cell.

**Calculated Bias Winding Turns and Voltage**  $N_{BIAS}$ ,  $V_{F,BIAS}$ Where a bias winding is used, the number of turns and voltage developed are displayed. The relatively large default number of turns allows the bias to be used as a shield winding for reduced EMI. If desired, the number of turns can be adjusted by entering a value into

The variables described in Step 3 are found in the "Transformer Construction Parameters, Primary Winding, Secondary Winding, and Bias Winding" section of the spreadsheet (see Table 10, Table 12, Table 13, and Table 14).

Other transformer parameters calculated in the spreadsheet are:

# **NPRIMARY** - Primary Winding Number of Turns

ALG (nH/T^2) - Gapped Core Effective Inductance

**BAC (Gauss)** - AC Flux Density for Core Loss Curves (0.5 xPeak to Peak) **AWG** - Primary Wire Gauge (Rounded to next smaller standard AWG value)

**OD PRIMARY INSULATED (mm)** - Primary winding wire outer diameter with insulation

**OD PRIMARY BARE (mm)** - Primary winding wire outer diameter without insulation

CMA PRIMARY (mils^2/Amp) - Primary Winding Current Capacity

# Step 4 – Iterate Transformer Design and Generate Transformer Design Output

Iterate the design making sure that no warnings are displayed. Any parameters outside the recommended range of values can be corrected by following the guidance given in the right hand column.

Once all warnings have been cleared, the output transformer design parameters can be used to either wind a prototype transformer or send to a vendor for samples. The key transformer electrical parameters are:

# Primary Inductance, $L_{PRIMARY_TYP}$ (µH)

This is the target nominal primary inductance of the transformer.

# Primary Inductance Tolerance, L<sub>PRIMARY\_TOL</sub> (%)

This is the assumed primary inductance tolerance. A value of  $\pm 10\%$  is used by default, however if specific information is known from the transformer vendor, then this may be overridden by entering a new value in the gray override cell.

# Step 5 – Selection of Input Stage

The input stage comprises fusible resistor(s), input rectification diodes and line filter network. Flameproof fusible resistors are recommended to be chosen and depending on the differential line input surge requirements, a wire-wound type may be required. The fusible resistor(s) provides fuse safety, inrush current limiting and differential mode noise attenuation. The EMI performance of half-wave rectified designs is improved by adding a second diode in the lower return rail.

The EMI performance of half-wave rectified designs is improved by adding a second diode in the lower return rail. This provides EMI gating (EMI currents only flow when the diode is conducting) and also doubles the differential surge-withstand as the surge voltage is shared across two diodes. In designs using a single input capacitor at least one of the input diodes should be a fast type (trr < 200 ns), This reduces ringing and associated increase in EMI. Table 15 shows the recommended input stage based on output power for a universal input design while Table 4 shows how to adjust the input capacitance for other input voltage ranges.

| Pout                                  | ≤1 W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ≤3                                                                                                                                                                                                                                                                                                                                                                           | ; w                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Suggested 85 – 265 VAC<br>Input Stage | $\begin{array}{c c} & & & & & \\ & & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & & \\ & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & &$ | $\begin{array}{c} \bullet & \bullet & \bullet \\ R_{F1} & D_{1N1} & \bullet & \bullet \\ \bullet & \bullet & C_{1N1} & C_{1N2} \\ \bullet & \bullet & C_{1N1} & C_{1N2} \\ \bullet & \bullet & \bullet & \bullet \\ \bullet & \bullet & \bullet & \bullet \\ \bullet & \bullet &$                                                                                            | $\begin{array}{c} \begin{array}{c} \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\$                                                                                                                                                                                                                                                                                                                                  |

| Component<br>Selection Guide          | $ \begin{array}{c} {\sf R}_{\sf F1} : 8.2 \ \Omega, \ 1 \ W \\ \qquad {\sf Fusible} \\ {\sf R}_{\sf F2} : \ 100 \ \Omega, \ 0.5 \ W, \\ \qquad {\sf Flameproof} \\ {\sf C}_{\sf IN1}, \ {\sf C}_{\sf IN2} : \ge 3.3 \ \mu{\sf F}, \\ \qquad 400 \ V \ each \\ {\sf D}_{\sf IN1}, \ {\sf D}_{\sf IN2} : \ 1N4007, \\ \qquad 1 \ A, \ 1000 \ V \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $ \begin{array}{l} R_{\text{F1}} : 8.2 \text{ W}, 1 \text{ W} \\  \text{Fusible} \\ L_{\text{IN}} : 470 \text{ mH} - 22 \text{ mH}, \\ (0.05 \text{ A} - 0.3\text{A}) \\ C_{\text{IN1}}, C_{\text{IN2}} : \geq 4 \ \mu\text{F/W}_{\text{OUT'}} \\ 400 \text{ V} \text{ each} \\ D_{\text{IN1}}, D_{\text{IN2}} : 1\text{N4007}, 1 \text{ A}, \\ 1000 \text{ V} \end{array} $ | $ \begin{array}{l} R_{\text{F1}} : 8.2 \text{ W}, 1 \text{ W} \\  \text{Fusible} \\ L_{\text{IN}} : 470 \mu\text{H} - 2.2 \text{m}\text{H}, \\ (0.05 \text{ A} - 0.3 \text{ A}) \\ C_{\text{IN1}}, C_{\text{IN2}} : \geq 2 \mu\text{F}/\text{W}_{\text{OUT}}, \\  400 \text{ V} \text{ each} \\ D_{\text{IN1}}, D_{\text{IN2}}, D_{\text{IN3}}, D_{\text{IN4}} : 1\text{N4007}, 1 \text{ A}, \\  1000 \text{ V} \end{array} $ |

| Comments                              | **Increase value to meet required<br>differential line surge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | **Increase value to meet required differential line surge                                                                                                                                                                                                                                                                                                                    | **Increase value to meet required<br>differential line surge                                                                                                                                                                                                                                                                                                                                                                  |

Table 15. Input Filter Recommended Based on Total Output Power.

# Step 6 – Selection of LinkSwitch-XT2 External Components

LinkSwitch-XT2 current limit can be selected using the 0805 size BYPASS pin capacitor for more stability (0.1  $\mu\text{F}$  for normal current limit / 1  $\mu\text{F}$  for reduce current limit). LinkSwitch-XT2 ICs select between normal and reduced current limit at power-up prior

# Step 7 – Selection of Primary Clamp Circuit

For output powers of 2.5 W or below and using the LNK3604, it is possible to eliminate external clamp components by careful design of the transformer and bias winding. For Clampless designs, a 2-layer primary should be used. The resultant increase in the intra-winding capacitance limits the peak drain voltage at turn off. For output powers greater than 2 W, the winding capacitance is not sufficient to limit peak drain voltage. Therefore a bias winding should be added to the transformer and rectified with a standard recovery (rectifier) diode. Suitable diodes for the bias winding include 1N4003-1N4007. The addition of a bias winding acts as a clamp and also reduces the leakage inductance ringing and improves EMI. Table 16 summarizes the requirements between Clampless designs and designs using an external clamp.