# Application Note AN-106Q for Automotive Applications InnoSwitch3-AQ Family

Design Guide

#### 1 Introduction

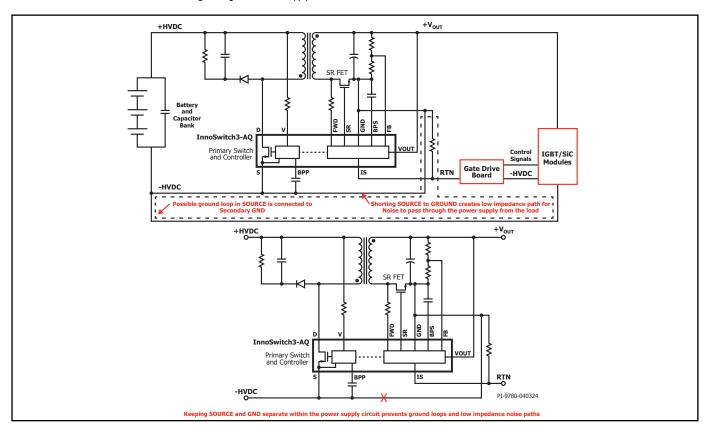

Power supplies used in automotive applications are usually subject to much harsher conditions than those used in commercial or industrial stationary applications. Automotive power supplies are often exposed to wide temperature ranges, shock and vibration, foreign particles and contaminants, and high levels of EMI. Bus voltages can go as high as 1000 VDC for electric vehicles, so the effects of high-voltage DC and transients must also be considered. Depending on the load, input voltage, and location of a power supply in a vehicle, the conditions stated earlier must be considered to ensure a safe, stable, and reliable power supply operation.

In many automotive applications, the power supply is part of the functional safety concept according to ISO26262. Reliability through proper design is mandatory. This application note considers a design supporting ISO26262.

The InnoSwitch™3-AQ family of ICs dramatically simplifies the design and manufacture of isolated flyback power converters in automotive applications. The InnoSwitch3-AQ family combines primary and secondary controllers and safety-rated feedback into a single IC allowing accurate output voltage regulation even with a wide input voltage range of 30 VDC to >1000 VDC.

InnoSwitch3-AQ devices incorporate multiple protection features, including input line over- and undervoltage protection¹, output overvoltage and over-current limiting, and over-temperature protection. The devices' ability to start up from 30 V input makes them ideal for functional safety critical emergency power supplies.

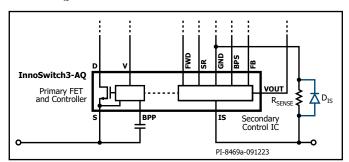

The InnoSwitch3-AQ IC combines a high-voltage power switch (MOSFET, SiC MOSFET or PowiGaN $^{\text{TM}}$ ) along with both primary-side (high-voltage side) and secondary-side (low-voltage side) controllers in one device. The architecture incorporates a novel inductive coupling feedback scheme (FluxLink $^{\text{TM}}$ ) with reinforced isolation to provide a safe, reliable way to transmit accurate output voltage and current information from the secondary to the primary controller.

The primary controller on the InnoSwitch3-AQ IC is a quasi-resonant (QR) flyback controller that can operate in and seamlessly switch between continuous conduction mode (CCM), boundary mode (CrM), and discontinuous conduction mode (DCM). The controller uses both variable frequency and variable current control schemes. The primary controller consists of a frequency jitter oscillator, a receiver circuit magnetically coupled to the secondary controller, a current limit controller, a 5 V regulator on the PRIMARY BYPASS pin, an audible noise reduction engine for light load operation, bypass overvoltage detection circuit, current limit selection circuitry, over-temperature protection, leading edge blanking, and a high-voltage switch (either 750 V, 900 V or 1700 V).

$^{\scriptsize 1}$  V Pin OV trigger is disabled by default in INN3947CQ and INN3949CQ

The InnoSwitch3-AQ secondary controller consists of a transmitter circuit that is magnetically coupled to the primary receiver, constant voltage (CV) and constant current (CC) controller, a 4.4 V regulator on the SECONDARY BYPASS pin, QR mode circuitry, oscillator and timing circuits and numerous integrated protection features.

#### 2 Scope

This application note is intended to guide engineers in designing an isolated DC-DC flyback power supply using the InnoSwitch3-AQ family of devices for automotive applications. This application note uses the Power Integrations PIXIs designer tool for InnoSwitch3-AQ devices. The PIXIs designer is part of the PI Expert Suite™ of software tools developed to simplify the process of designing with Power Integrations′ products. PIXIs is a spreadsheet-based tool that takes a user's specifications and calculates critical design parameters needed to complete a power supply design. (PIXIs is available at <a href="https://piexpertonline.power.com">https://piexpertonline.power.com</a>)

#### This Application Note Contains the Following Sections/ Topics:

- Step-by-step design checklist for PIXIs, component selection, and layout for automotive applications.

- Electrical design guide for high input voltage power supplies according to IEC 60644-1.

- Transformer design and component selection for high-voltage and wide ambient temperature operating range (-40 °C to 105 °C).

- 4. Layout recommendations for high EMI immunity.

- 5. Circuit design, layout, and transformer guidelines.

- 6. Circuit suggestions for additional protection.

#### 3 Related Documents and Standards

/1/ InnoSwitch3-AQ Family Data Sheet

/2/ AN-72 InnoSwitch3 Family Design Guide

/3/ IEC 60664-1:2020

Insulation coordination for equipment within low-voltage supply systems

Part 1: Principles, requirements and tests

/4/ IEC 60664-4:2005

Insulation coordination for equipment within low-voltage supply systems

Part 4: Consideration of high-frequency voltage stress.

www.power.com June 2024

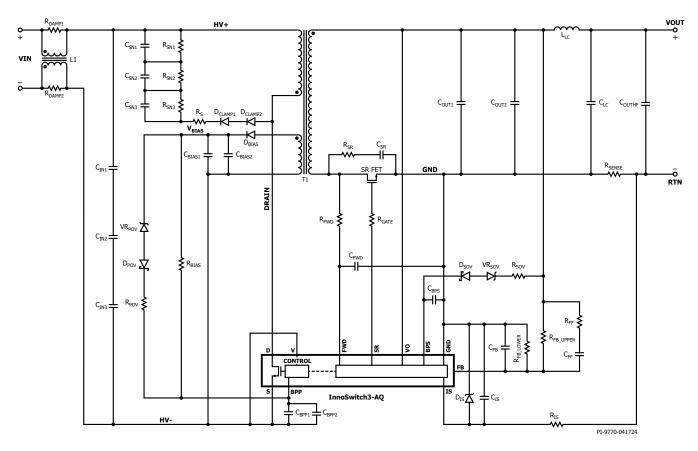

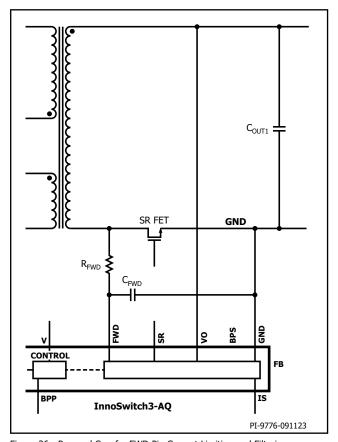

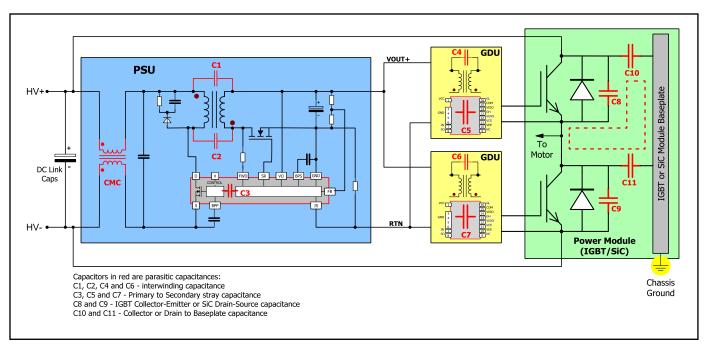

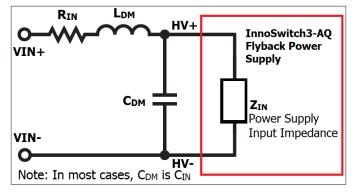

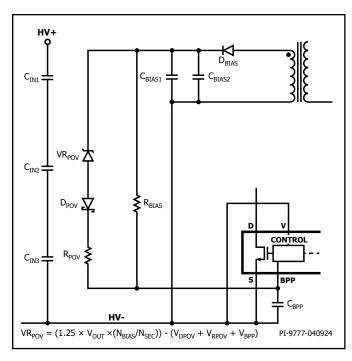

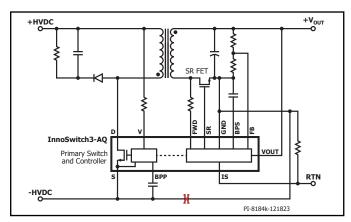

#### 4 Typical Application Schematic

Figure 1 shows the typical application schematic for an isolated flyback converter using the InnoSwitch3-AQ controller. Unless otherwise specified, references to components in this document shall refer to the designators shown in Figure 1. The schematic shown will apply to most applications. Changes in the component count for some circuit sections shall depend on the target application's specifications.

1. Input capacitors  $(C_{_{INX}})$  – series/parallel combination will depend on input voltage range and filtering requirements.

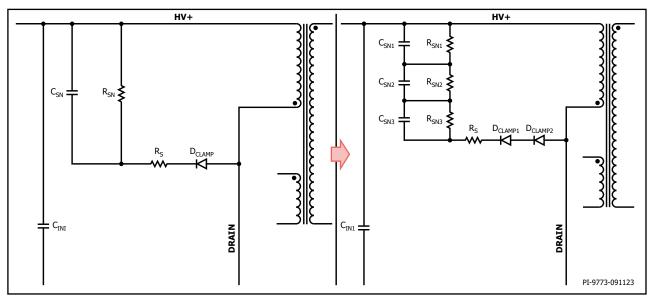

- 2. Snubber network ( $C_{SNx'}$ ,  $R_{SNx'}$ ,  $R_{Sx'}$  and  $D_{CLAMPx}$ ) series/parallel combinations of the snubber network will vary according to input voltage range and output power requirements.

- Output capacitors (C<sub>OUTx</sub>) the number of parallel capacitors will depend on output voltage ripple and operating life.

- 4. SR FETs the number of units in parallel depends on temperature rise and efficiency targets.

Component values and ratings will vary according to specific application specifications.

Figure 1. InnoSwitch3-AQ Typical Application Schematic.

#### 5 Design Checklists

This section contains checklists that designers can follow to ensure all relevant points when designing using the InnoSwitch3-AQ are addressed before a prototype is built. The checklist is split into multiple parts:

- 1. PIXIs

- 2. Component Selection

- 3. Layout

It is recommended that designers review each item in the checklist to reduce development time by increasing the likelihood of a specifications -compliant prototype (may require minor tuning during testing).

#### Part 1: PIXIs Design Checklist

Go to <a href="https://piexpertonline.power.com">https://piexpertonline.power.com</a> to access the PIXIs design spreadsheet

#### **IMPORTANT!**

When using PIXIs, no WARNINGS must be shown on the INFO column of the spreadsheet. If warnings are present, the reason for the warning and tips on resolving it will be given in the right most column of the spreadsheet.

#### DESIGNS WITH WARNINGS ARE NOT CONSIDERED VIABLE.

| ✓ | #                                                                                                   | Parameter                                                                                                                                                         | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page      |

|---|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|   | 1                                                                                                   | Set Desired Output Voltage (VOUT): Output voltage should be from 5 V to 24 V.                                                                                     | For VOUT >24 V, contact Power Integrations for more details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <u>11</u> |

|   | 2                                                                                                   | Input all Desired Operating Conditions: Set at least two operating conditions - the maximum and minimum input voltage with its respective maximum output current. | a) Up to 9 operating conditions can be specified. PIXIs will try to find the best solution to meet all conditions. b) Use default values for EFFICIENCY (0.85) and Z_FACTOR (0.5).                                                                                                                                                                                                                                                                                                                                                           | 11        |

|   | 3                                                                                                   | Select Primary Controller: Use the power table in the InnoSwitch3-AQ data sheet as a guide to select the appropriate device.                                      | See Section 6.2 of this document for more details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <u>12</u> |

|   | 4                                                                                                   | Select Controller Current Limit Mode:<br>Choose between STANDARD and INCREASED.                                                                                   | In general: STANDARD - if the power output is well within the device's capability or cooling is a challenge. INCREASED - if a higher power is required, especially at minimum input or if thermal management is not an issue. See Section 6.2 for more design options and considerations.                                                                                                                                                                                                                                                    | 12        |

|   | 5 400 VDC systems: 65 KHZ for 60 W and above, 85 KHZ is                                             |                                                                                                                                                                   | This value can be iterated until an acceptable design is achieved. See Section Worst-Case Electrical Parameters for more details.                                                                                                                                                                                                                                                                                                                                                                                                            | <u>13</u> |

|   | 6                                                                                                   | $V_{\rm OR}$ : In general, set $V_{\rm OR}$ to 10x to 12.5x of VOUT                                                                                               | See Table 3 in Section Worst-Case Electrical Parameters for a list of suggested V <sub>OR</sub> values.                                                                                                                                                                                                                                                                                                                                                                                                                                      | <u>14</u> |

|   | 7                                                                                                   | Primary Inductance Tolerance (LPRIMARY_TOL)                                                                                                                       | Use 5% to 7% tolerance for higher transformer production yield.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <u>14</u> |

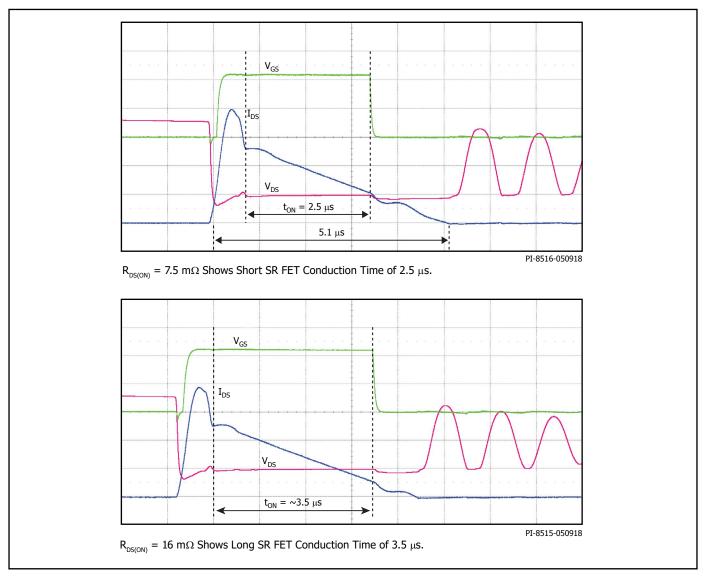

|   | 8                                                                                                   | SR FET: Use the SR FET automatically chosen by PIXIs.                                                                                                             | If another SR FET is used, it should meet the following requirements: a) 1.265 V $\leq$ V $_{\text{TH(MIN)}} \leq$ 2.5 V. b) $R_{\text{DS(ON)}} > (0.01 \times \text{V}_{\text{OUT}})/(I_{\text{p}} \times \text{V}_{\text{OR}})$ where $I_{\text{p}}$ is the primary peak current limit (PIXIs Row 78). c) Use SR FET with lowest body diode $T_{\text{RR}}$ available. d) It is not recommended to use FETs with breakdown voltage $>$ 150 V (limited by FWD pin voltage rating). e) See Section 7.5 for more details on SR FET selection. | 31        |

|   | Transformer Core Selection: Select core from the database. Ensure $B_{PEAK} \le 3800$ If the Gauss. |                                                                                                                                                                   | If the desired core is not on the PIXIs database, check the core size for power handling capability by following the steps in Section 8.1.                                                                                                                                                                                                                                                                                                                                                                                                   | <u>35</u> |

| ✓                                                                                                                                                                                                                                                 | #                                                                                         | Parameter                                                                                                                                                                                                                                                                                                                                                                                          | Comments                                                                                                                                                                                                                                              | Page      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

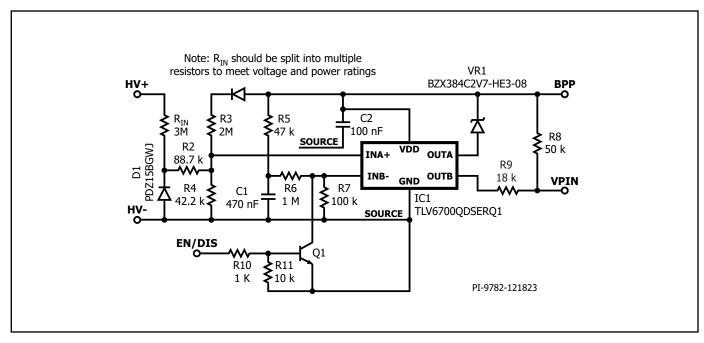

|                                                                                                                                                                                                                                                   | 10                                                                                        | Primary Components Selection Section Select OV/UV mode. Input desired OV/UV thresholds and use calculated components.                                                                                                                                                                                                                                                                              | Check the data sheet to see if the device has UV-only protection or both OV and UV.                                                                                                                                                                   | <u>17</u> |

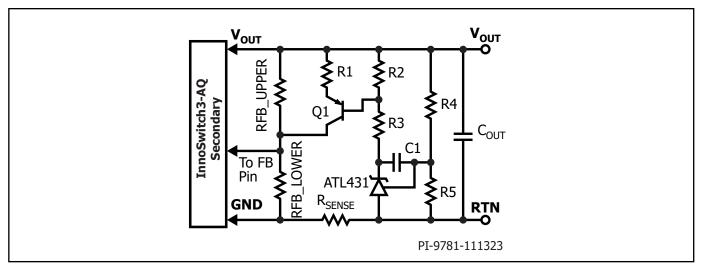

|                                                                                                                                                                                                                                                   | 11 Use PIXIs computed values for the feedback network resistors and capacitor. (<19 Volta |                                                                                                                                                                                                                                                                                                                                                                                                    | For high-precision voltage regulation requirements (<1% tolerance across temperature), see the Precision Voltage Regulation Circuit in Section 9.6                                                                                                    | <u>45</u> |

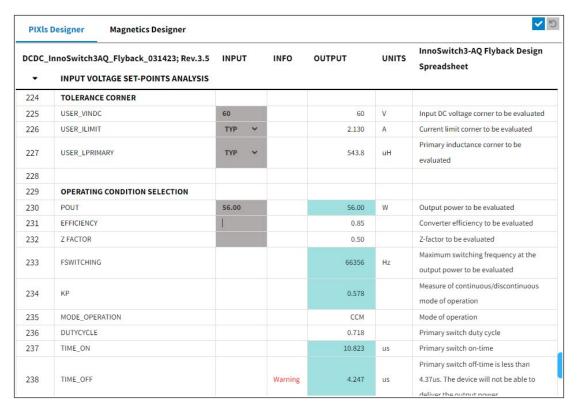

| Set-Point Analysis  12 Use set-point analysis to check operating points and loading conditions.  show the point analysis to check operating points and loading conditions.                                                                        |                                                                                           | Use set-point analysis to check operating points and                                                                                                                                                                                                                                                                                                                                               | Check the following tolerance combinations. There should be no warnings issued by PIXIs (PIXIs rows 225-227). a. VINMIN, ILIMIT_MAX, LPRIMARY_MAX b. VINMAX, ILIMIT_MIN, LPRIMARY_MIN                                                                 | <u>21</u> |

|                                                                                                                                                                                                                                                   | 13                                                                                        | Check InnoSwitch3-AQ IC Power Loss and Temperature Rise Calculate the expected operating temp of the InnoSwitch3-AQ IC using the parameters from PIXIs.                                                                                                                                                                                                                                            | See Section 6.7.1 on how to calculate temperature rise. If the calculated operating temperature is ≥130 °C at maximum ambient temperature, iterate the design to reduce temperature (e.g., adjust switching frequency, change InnoSwitch3-AQ device). | <u>22</u> |

|                                                                                                                                                                                                                                                   |                                                                                           | a) Check if windings fit inside the selected core/bobbin. Fill must be 80% or less to ensure manufacturability.     b) Use estimated power loss to calculate the                                                                                                                                                                                                                                   | Adjust wire gauge and turns ratio in PIXIs if fill or loss is too high. See Section 6.6 for details.                                                                                                                                                  |           |

|                                                                                                                                                                                                                                                   | '                                                                                         | Part 2: Component (Component designators refer to                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                       |           |

| ✓                                                                                                                                                                                                                                                 | #                                                                                         | Parameter                                                                                                                                                                                                                                                                                                                                                                                          | Comments                                                                                                                                                                                                                                              | Page      |

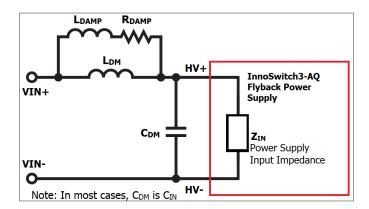

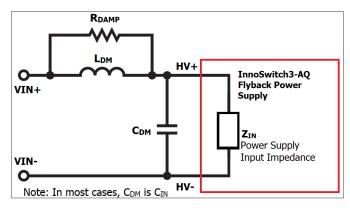

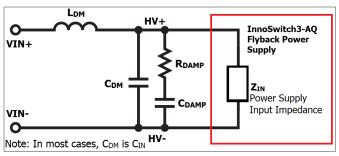

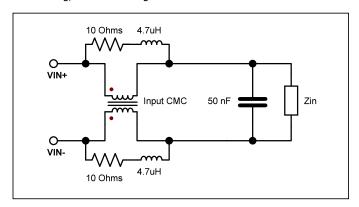

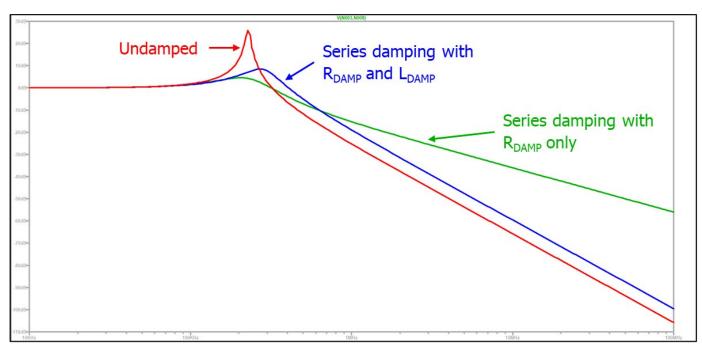

|                                                                                                                                                                                                                                                   | 1                                                                                         | Input CMC (L1) and Damping Resistors (R <sub>DAMPx</sub> ) a) Use CMC with the highest inductance available that can meet the required maximum input voltage and current. b) Damping resistors should be at least thick film, 1206 SMD resistors. The use of surge-capable resistors is recommended.                                                                                               | See Section 9.1 for the calculation of damping resistors.                                                                                                                                                                                             | <u>36</u> |

|                                                                                                                                                                                                                                                   | 2                                                                                         | Input Capacitors (C <sub>INx</sub> ) a) Use 68 nF to 150 nF, 1206, MLCC, X7R, rated ≥500 V. b) Minimum of 3 in series.                                                                                                                                                                                                                                                                             | Larger capacitors can be used if the capacitor has soft termination. Place $C_{\text{IN}}$ in the layout in such a way as to reduce the primary loop.                                                                                                 | -         |

|                                                                                                                                                                                                                                                   | 3                                                                                         | Primary Snubber Circuit (R <sub>SNX</sub> , C <sub>SNX</sub> , D <sub>CLAMPX</sub> , R <sub>s</sub> ) a) If the transformer prototype is ready, calculate snubber based on actual measured primary leakage inductance. b) If no transformer is available yet, assume leakage (L <sub>LK</sub> ) to be 1% of L <sub>PRIMARY</sub> for designs 35 W and higher. Otherwise, use 1.5% assumed leakage. | See Section 7.2 for snubber topology, design calculations, and component selection.                                                                                                                                                                   | <u>29</u> |

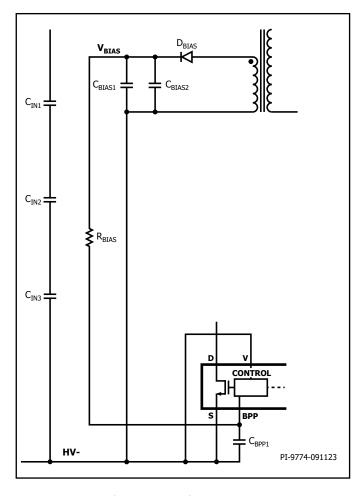

| Primary Bias Voltage (D <sub>BIASX</sub> , C <sub>BIAS</sub> , R <sub>BIAS</sub> ) a) D <sub>BIAS</sub> - use 200 V, 200 mA, fast-recovery diode (BAS21GWX or equivalent). b) C <sub>BIAS</sub> - use two 10 μF, 50 V, 1206, X7R MLCC capacitors. |                                                                                           | a) D <sub>BIAS</sub> - use 200 V, 200 mA, fast-recovery diode                                                                                                                                                                                                                                                                                                                                      | Place the bias voltage components close to the transformer pins to minimize the bias loop. Place $R_{\text{BIAS}}$ close to $C_{\text{BPP}}$ . See Section 7.3 for the calculation of optimum $R_{\text{BIAS}}$ .                                     |           |

| $ $ b) $C_{RIAS}$ - use two 10 $\mu$ F, 50 V, 1206, X7R MLCC $ $ cl                                                                                                                                                                               |                                                                                           | b) $C_{\text{BIAS}}$ - use two 10 $\mu\text{F}$ , 50 V, 1206, X7R MLCC capacitors.                                                                                                                                                                                                                                                                                                                 | close to $C_{\mbox{\tiny BPP}}$ . See Section 7.3 for the calculation of optimum $R_{\mbox{\tiny BIAS}}$ .                                                                                                                                            |           |

| ✓                                                                                                                                                                                       | #                                                                                                                                                                                                               | Parameter                                                                                               | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Page      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

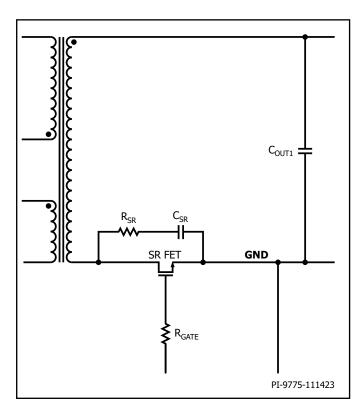

|                                                                                                                                                                                         | 6 Recommended starting values are: FE                                                                                                                                                                           |                                                                                                         | The values given here are starting values. Adjust SR FET Snubber values during prototype testing. See Section 7.6 for more details.                                                                                                                                                                                                                                                                                                                                                                                                                    | <u>33</u> |

|                                                                                                                                                                                         | 7                                                                                                                                                                                                               | Secondary Synchronous Rectifier (SR FET)                                                                | Estimate power loss using PIXIs values for the SR FET, then specify copper cooling area size before starting the layout.                                                                                                                                                                                                                                                                                                                                                                                                                               | -         |

| Recommended values: a) For R <sub>FWD</sub> , use 47 Ω, 0805 or 1206, thick film SMD resistor. b) For C use 100 pF 250 V 1206 X7R MICC                                                  |                                                                                                                                                                                                                 | Recommended values: a) For R $_{\text{FWD}}$ , use 47 $\Omega$ , 0805 or 1206, thick film SMD resistor. | During prototype testing, if the FWD pin voltage spike is near 150 V (> 85%), $R_{\text{FWD}}$ can be increased to 100 $\Omega$ and $C_{\text{FWD}}$ to 330 pF. Place $C_{\text{FWD}}$ and $R_{\text{FWD}}$ very close to the FWD pin and on the same layer as the InnoSwitch3-AQ. See Section 7.7 for more information.                                                                                                                                                                                                                               | <u>34</u> |

| 9 Use 2.2 μF, 0805 or 1206 SMD package, X7R or C0G, Initiated >25 V, MLCC capacitors                                                                                                    |                                                                                                                                                                                                                 | Use 2.2 μF, 0805 or 1206 SMD package, X7R or C0G,                                                       | The BPS capacitor must be placed close to the BPS and GND pins and on the same layer as the InnoSwitch3-AQ IC. See Section 7.4 for more information.                                                                                                                                                                                                                                                                                                                                                                                                   |           |

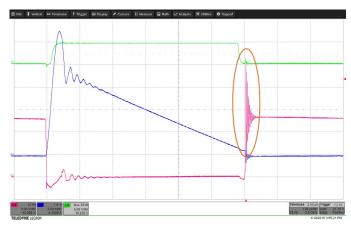

|                                                                                                                                                                                         | SR FET Gate Resistor ( $R_{GATE}$ ) a) Default value is 0 $\Omega$ . b) Use 0603, thick film SMD resistor.                                                                                                      |                                                                                                         | Place $R_{GATE}$ next to the GATE pin of the SR FET. If oscillations are observed in the SR GS pin or SR VDS has large spikes, $R_{GATE}$ can be increased up to 5.6 $\Omega$ . If parallel SR FETs are necessary to meet thermal requirements, each SR FET must have its own gate resistor with a value < 4.7 $\Omega$ .                                                                                                                                                                                                                              |           |

|                                                                                                                                                                                         |                                                                                                                                                                                                                 |                                                                                                         | Place feedback network components close to the InnoSwitch3-AQ IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <u>17</u> |

| Current Sense Resistor (R <sub>SENSE</sub> )  a) R <sub>SENSE</sub> = 35 mV/ I <sub>OUT(MAX)</sub> b) Use 1206 or larger package, 1% tolerance or better, current sense chip resistors. |                                                                                                                                                                                                                 | a) $R_{SENSE} = 35$ mV/ $I_{OUT(MAX)}$<br>b) Use 1206 or larger package, 1% tolerance or                | a) Use multiple resistors in parallel for consistent current limit across temperature for high current applications (>3 A). b) $R_{\text{SENSE}}$ must be placed close to the InnoSwitch3. If this is not possible, use a Kelvin connection and properly route the signal to the IS pin. c) $I_{\text{OUT(MAX)}}$ should be higher than the highest-rated output current. A value $10\%$ - $20\%$ higher than $I_{\text{OUT(MAX)}}$ may be used to ensure that there is adequate margin between the protection threshold and the rated output current. | -         |

|                                                                                                                                                                                         | Current Sense Filter ( $R_{1s}$ , $C_{1s}$ )  a) For $C_{1s}$ , use 1 $\mu$ F to 4.7 $\mu$ F, 0805, X7R or C0G,  b) For $R_{1s}$ , use 10 $\Omega$ , 0402 or 0603, 1% tolerance or better, thick film resistors |                                                                                                         | Component placement should be beside the IS pin and on the same layer. For $C_{\rm Is'}$ a 1 $\mu$ F capacitor is suitable for most applications. In some designs, the value may be increased to 4.7 $\mu$ F depending on the circuit board layout and noise filtering needed for the IS pin signal.                                                                                                                                                                                                                                                   | -         |

| ✓ | #                                                                                                                                                          | Parameter                                                                                                                                                     | Comments                                                                                                                                                                                                                                                                                                                                                                                 | Page      |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|   | 14                                                                                                                                                         | Output Capacitors ( $C_{out}$ ) a) Use 220 $\mu$ F to 330 $\mu$ F per ampere of load current. b) Use only polymer and hybrid polymer electrolytic capacitors. | a) Multiple capacitors in parallel can be used to reduce output ripple voltage. b) Ensure the total current ripple rating of the output capacitors is greater than the maximum secondary ripple current. c) Calculate capacitor life according to manufacturer recommendations. d) Place output capacitors in the layout to reduce the secondary loop. See Section 7.8 for more details. | <u>34</u> |

|   | 15                                                                                                                                                         | High-Frequency Output Filter Capacitor ( $\mathbf{C}_{\text{OUTHF}}$ ) Use 0.1 μF to 10 μF, 1206, X7R or C0G, 50 V, MLCC.                                     | Place this capacitor where the load connects to the power supply. The load of the power supply must never bypass this capacitor. The selection of the most appropriate value depends on the measured ripple and EMI.                                                                                                                                                                     | ı         |

|   | 16 SMD diode.                                                                                                                                              |                                                                                                                                                               | Place primary-sensed overvoltage components near the InnoSwitch3-AQ IC. See Section 9.2 for the schematic and details.                                                                                                                                                                                                                                                                   | 43        |

|   | 17   SMD diode.                                                                                                                                            |                                                                                                                                                               | Place secondary-sensed overvoltage components near the InnoSwitch3-AQ IC. See Section 9.3 for details.                                                                                                                                                                                                                                                                                   | <u>43</u> |

|   | IS Pin Protection Diode (D <sub>1s</sub> ) Use a Schottky diode with at least 30 A non-repetitive peak current if no RC filter is used for the IS pin. The |                                                                                                                                                               | Needed during events such as an output short-circuit with very low impedance where IS pin voltage may exceed the absolute maximum rating of the pin. See Section 9.4.                                                                                                                                                                                                                    | <u>43</u> |

AN-106Q

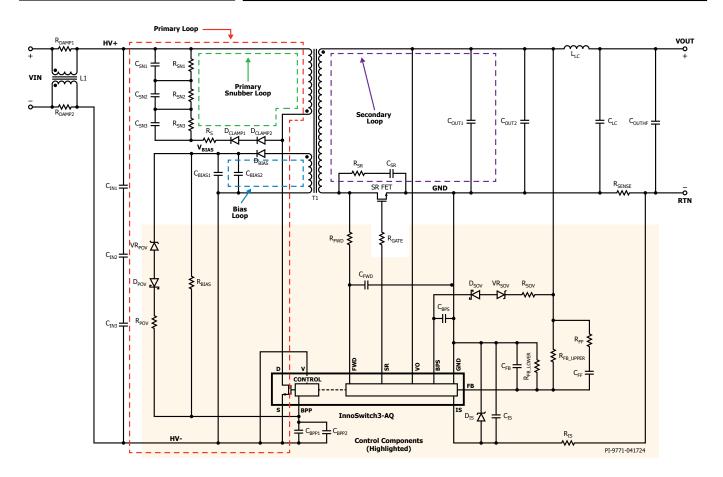

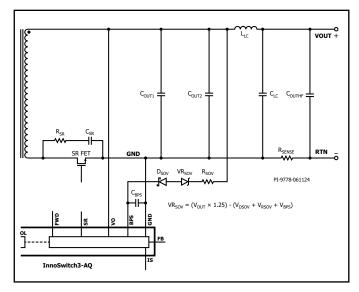

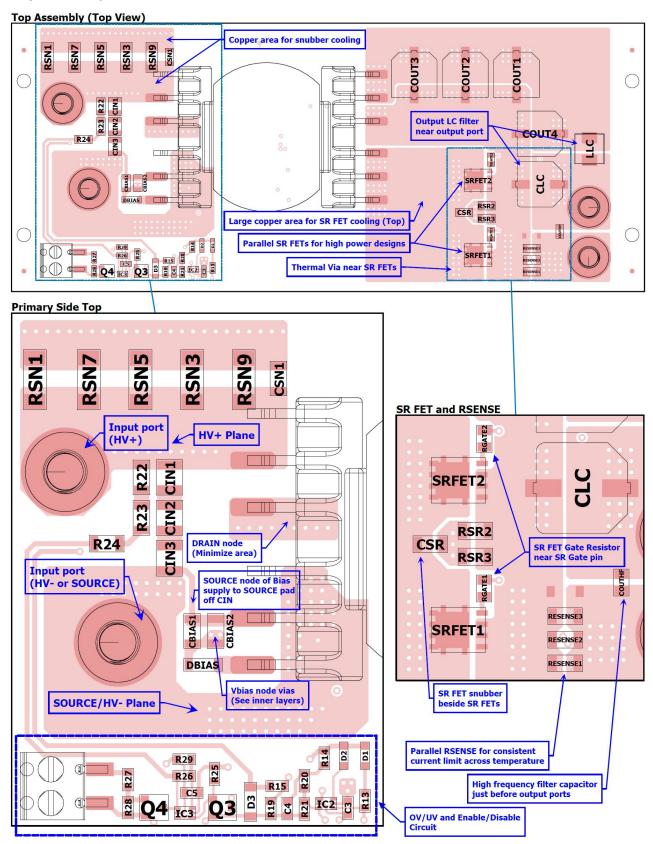

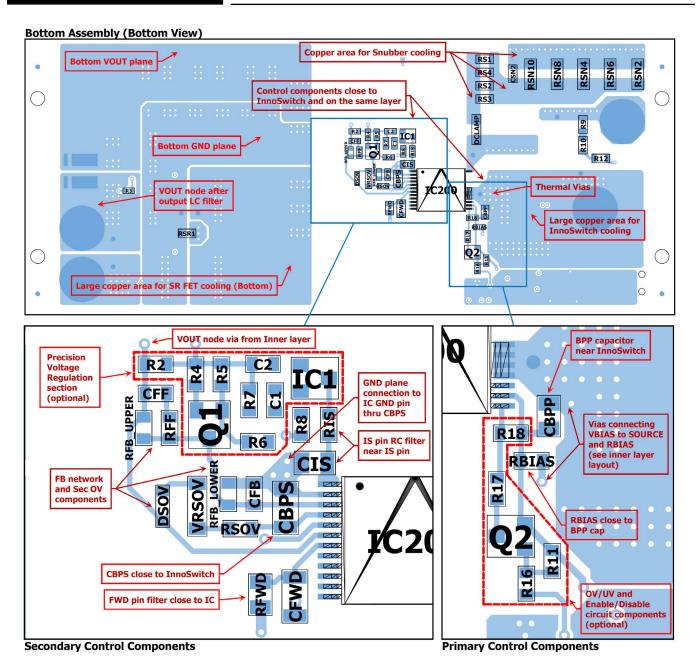

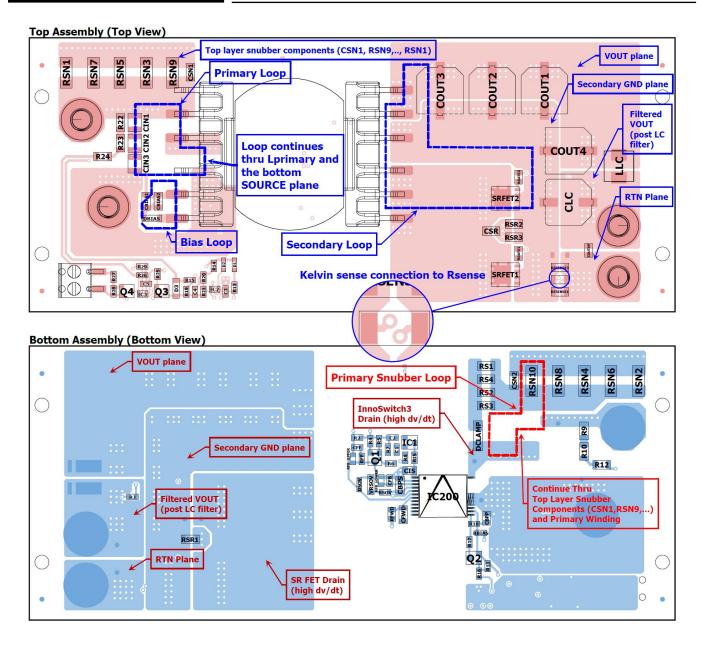

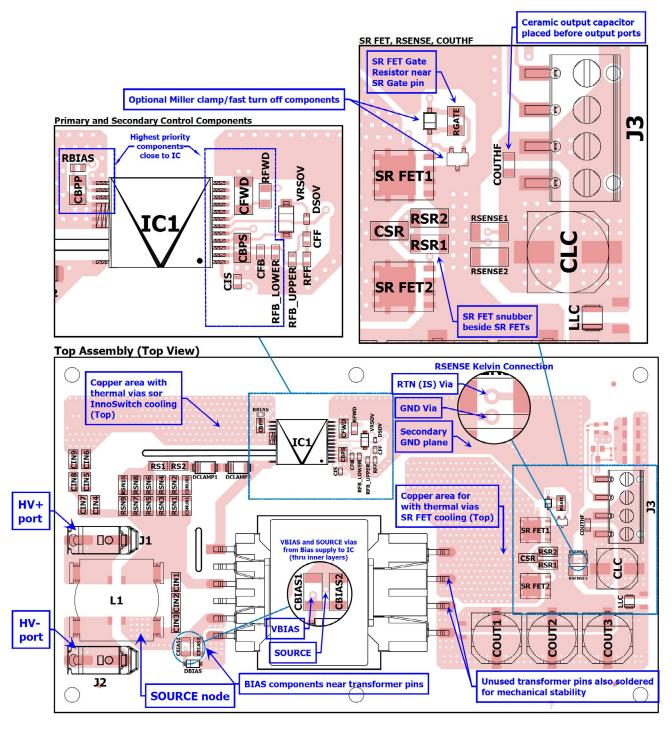

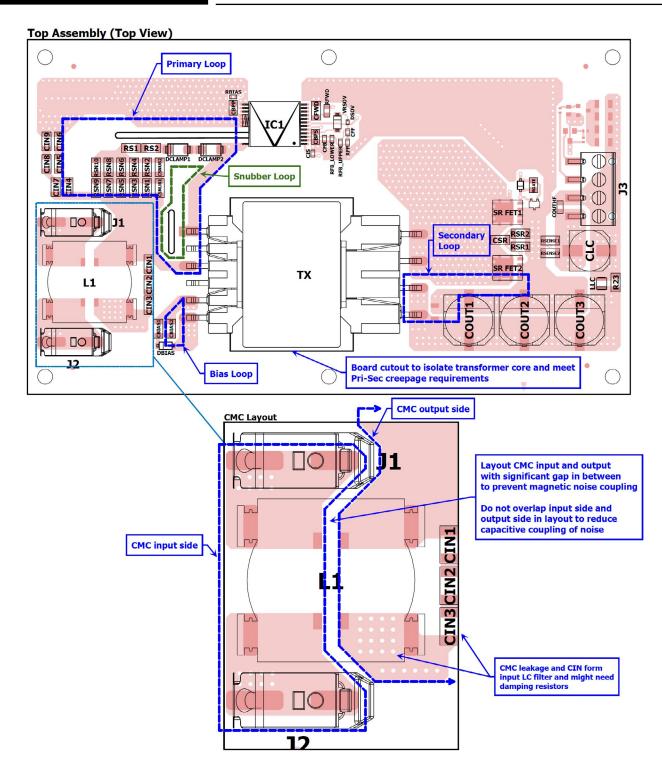

Figure 2. Schematic Showing Critical Loops and Control Components.

| (Refer to Figure 2 for identification of critical loops and control components)  ✓ # Components/Nets Comments |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                              |             |  |  |

|---------------------------------------------------------------------------------------------------------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| ✓                                                                                                             | # | Components/Nets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Comments                                                                                                                                                                                                                                                                                                                                                                                                     | Page        |  |  |

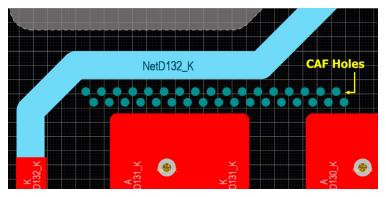

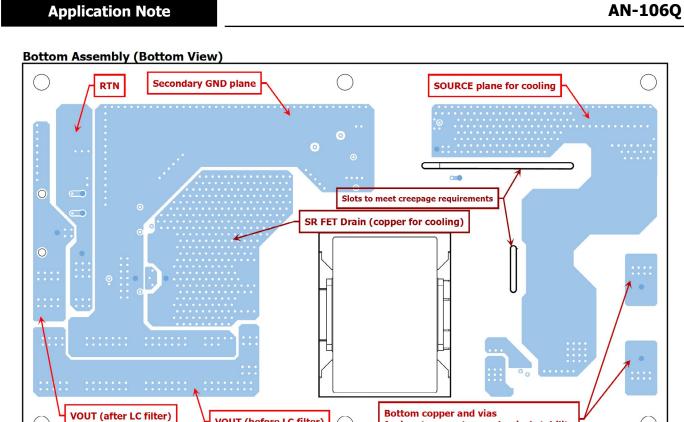

|                                                                                                               | 1 | Creepage and Clearance Calculate creepage and clearance requirements according to IEC 60664-1/4.                                                                                                                                                                                                                                                                                                                                                                                                                                                          | a) Functional/basic isolation for primary-to-primary. b) Reinforced isolation for secondary-to-primary. c) Creepage and clearance calculations should be done for all nodes with high voltage between them. See Section 10 for recommended minimum creepage and clearance values. d) Ensure pollution degree, altitude of operation, and humidity is considered based on the target application environment. | <u>47</u>   |  |  |

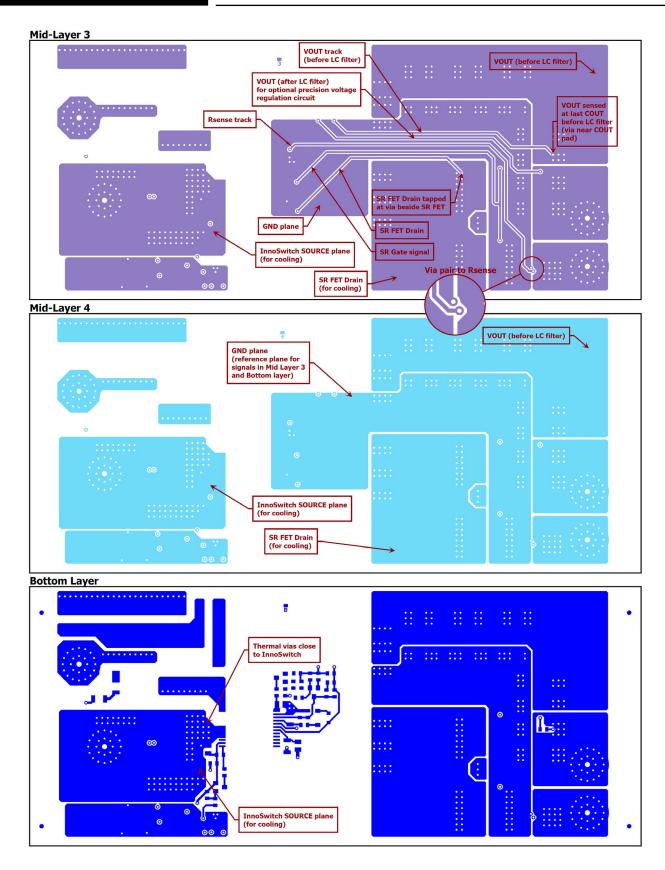

|                                                                                                               | 2 | Control Components (highlighted in Figure 2) Should be placed as close to the InnoSwitch3-AQ IC as possible. Placement should follow the following placement priority: 1) $C_{\text{BPP}}$ , $C_{\text{FWD}}$ , $C_{\text{FB}}$ and $C_{\text{IS}}$ 2) $R_{\text{BIAS}}$ (beside $C_{\text{BPP}}$ ), $R_{\text{FWD}}$ (beside $C_{\text{FWD}}$ ) 3) $R_{\text{FB\_LOWER}}$ (beside $C_{\text{FB}}$ ) and $R_{\text{IS}}$ (beside $C_{\text{IS}}$ ) 4) $R_{\text{FB\_UPPER}}$ , $R_{\text{FF}}$ and $C_{\text{FF}}$ 5) Primary and secondary OV components | a) Ideally, all control components should be on the same layer as the InnoSwitch IC. If this is not possible, ensure priority 1 and 2 components are placed in the same layer as the InnoSwitch3-AQ IC. b) All secondary control components connected to GND must connect to the IC GND pin through the C <sub>BPS</sub> pad.                                                                                |             |  |  |

|                                                                                                               | 3 | Control Components Routing Keep routes between control components short. Avoid vias if possible.                                                                                                                                                                                                                                                                                                                                                                                                                                                          | See Section 12 for layout examples.                                                                                                                                                                                                                                                                                                                                                                          |             |  |  |

|                                                                                                               | 4 | Input CMC Keep the input and output nodes of the CMC as far away as possible to prevent noise from coupling through the power lines.                                                                                                                                                                                                                                                                                                                                                                                                                      | See Section 12 for layout examples.                                                                                                                                                                                                                                                                                                                                                                          |             |  |  |

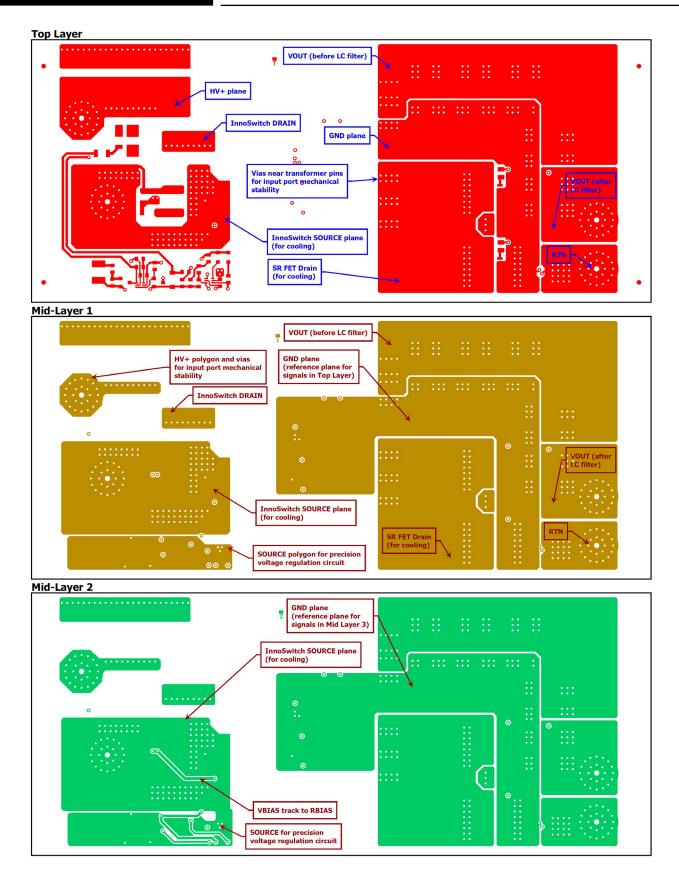

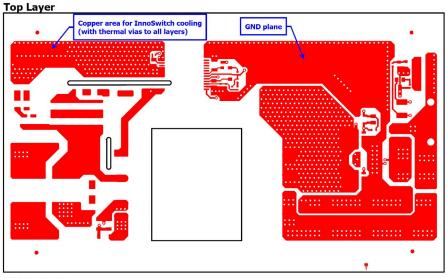

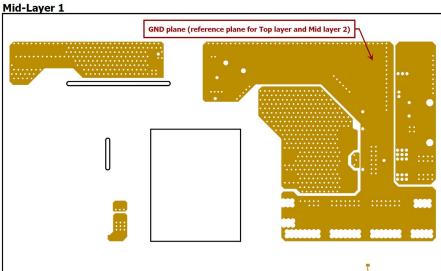

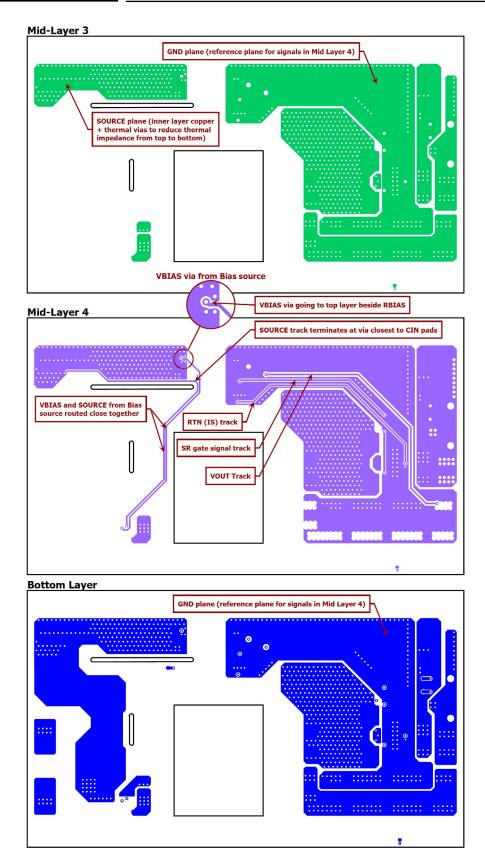

|                                                                                                               | 5 | Input Capacitors Place input capacitors close to the transformer and InnoSwitch3-AQ IC to minimize the primary loop.                                                                                                                                                                                                                                                                                                                                                                                                                                      | If the InnoSwitch3-AQ IC and input capacitors are not on the same layer, increase the number of vias connecting the SOURCE pin of the InnoSwitch3-AQ IC to the capacitors. Do the same for the capacitor to transformer pin connection.                                                                                                                                                                      | 48 to       |  |  |

|                                                                                                               | 6 | Snubber Network Position snubber components close together to minimize the primary snubber loop.                                                                                                                                                                                                                                                                                                                                                                                                                                                          | a) The anode of $D_{CLAMP}$ should connect directly to the DRAIN of the InnoSwitch3-AQ IC.<br>b) $R_{SN}$ and $C_{SN}$ should connect directly to the input capacitors, not the transformer HV+ pin. See Section 12.                                                                                                                                                                                         | · <u>59</u> |  |  |

|                                                                                                               | 7 | <b>Bias Voltage Components</b> Place bias components (C <sub>BIASx'</sub> D <sub>BIAS</sub> ) close to the transformer bias winding pins to minimize the bias loop.                                                                                                                                                                                                                                                                                                                                                                                       | a) Connect the SOURCE/HV- pad of $C_{BIAS}$ directly to the SOURCE/HV- pad of $C_{IN}$ . b) Isolate this track from the SOURCE polygon, which carries the primary switching current. c) Route $V_{BIAS}$ directly beside or overlapping the $C_{BIAS}$ to $C_{BPP}$ SOURCE/HV- track. d) If routed overlapping, these tracks should be on adjacent copper layers. See Section 12.                            |             |  |  |

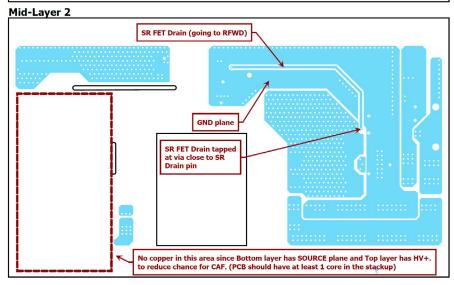

|                                                                                                               | 8 | SR FET and Output Capacitors Place near the secondary transformer pins to minimize the secondary loop area.                                                                                                                                                                                                                                                                                                                                                                                                                                               | a) When parallel FETs are used, place SR FETs close together. b) Ensure SR FETs have adequate copper cooling area to keep SR FET junction temperature within limits. c) If possible, have the cooling area present on all layers. d) Do not overlap the SR FET drain cooling area with other nodes, such as the GND plane, because this node has high dv/dt signals. See Section 12.                         |             |  |  |

| ✓ | #  | Components/Nets                                                                                                                                                                                                                    | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Page                |

|---|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

|   | 9  | SR FET RC Snubber Place beside the SR FET, preferably on the same layer.                                                                                                                                                           | If two SR FETs in parallel are used, place the SR FET RC snubber between the two MOSFETs. See Section 12.                                                                                                                                                                                                                                                                                                                                                                                   |                     |

|   | 10 | ${f R_{SENSE}}$ and ${f D_{IS}}$<br>Position ${f R_{SENSE}}$ to allow the shortest and most direct path to the ${f R_{IS}}$ and ${f C_{IS}}$ pin. ${f D_{IS}}$ , ${f C_{IS}}$ and ${f R_{IS}}$ as close to the IS pin as possible. | a) Protect $R_{\text{SENSE}}$ from noisy nodes such as the SR FET drain.<br>b) Route the signal from $R_{\text{SENSE}}$ to $R_{\text{IS}}$ in such a way as to avoid noisy tracks, such as the track from the SR FET drain to $R_{\text{FWD}}$ .<br>c) Avoid crossing other tracks containing high frequency signals such as the SR gate signal and $V_{\text{OUT}}$ .                                                                                                                      |                     |

|   | 11 | High dv/dt Nodes Minimize the copper area and track length for the following high dv/dt nodes: a) InnoSwitch3-AQ DRAIN. b) Track from SR FET to R <sub>FWD</sub> (use lower track width).                                          | Do not overlap high dv/dt nodes with any other node.                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     |

|   | 12 | High di/dt Loops Aside from tight component placement, routing of high di/dt loops should be done to reduce the area enclosed by the loop. See Figure 2.                                                                           | a) Large loops can generate large magnetic fields that can couple to nearby conductors. A larger loop will also be susceptible to noise from nearby magnetic fields. b) Minimize the length and loop area of the following: Primary loop, Secondary loop, Bias loop, and Primary snubber loop. See Section 12.                                                                                                                                                                              | Page<br>48 to<br>59 |

|   | 13 | Reference Planes and Return Paths                                                                                                                                                                                                  | Control signals must always be routed with a well-defined return path. The return path is usually an unbroken GND plane located on the adjacent layer where the signal is routed. Ensure the control signals are routed so the GND plane copper is always directly below the track. If this is not possible, tracks not overlapping a GND plane must be paired with a GND track routed together with the signal track and located on the same layer. See Section 12.                        |                     |

|   | 14 | Vias                                                                                                                                                                                                                               | Signals that go through vias and continue on a layer not adjacent to the signal's original GND plane must be accompanied by a GND via. This via allows the return current to easily transfer to a different GND plane or return path track. See Section 12. Multiple vias are recommended for critical control signals or power lines for reliability. Multiple vias are also recommended for tracks with high current or high di/dt to reduce via resistance and inductance, respectively. |                     |

| ✓ | #  | Components/Nets           | Comments                                                                                                                                                                                                                                                                                                                                                                                              | Page                        |

|---|----|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

|   | 15 | Intersecting Signals      | If unavoidable, signals that intersect and are located on different layers must always have a GND plane between their layers. Ideally, each signal layer must have its own GND plane on an adjacent layer.                                                                                                                                                                                            |                             |

|   | 16 | Secondary GND Plane       | The GND plane should connect to the GND pin of the InnoSwitch3-AQ IC only through the BPS pin capacitor GND pad. Multiple vias should be used to reduce the inductance from the GND plane to the GND pin. GND nodes from anywhere else in the circuit can connect directly to the GND plane through a via as long as return paths are well defined and do not intersect. See Section 12 for examples. | Page <u>48</u> to <u>59</u> |

|   | 17 | Signal Measurement Points | Connect control signals to appropriate measurement points.<br>a) The output voltage $(V_{\text{OUT}})$ signal must be tapped from the pad of the output capacitor.<br>b) Tap the SR Drain-Source voltage with a dedicated track from $R_{\text{FWD}}$ directly to the drain pad of the SR MOSFET.                                                                                                     |                             |

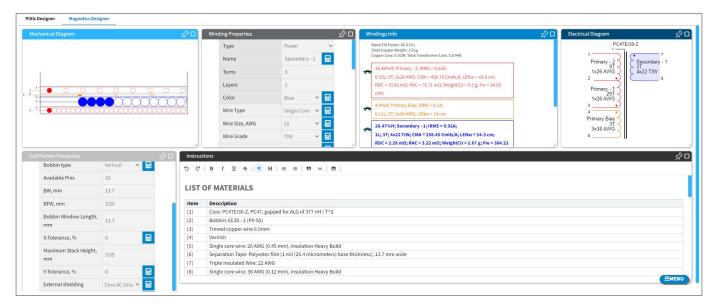

#### 6 PIXIs Design Details

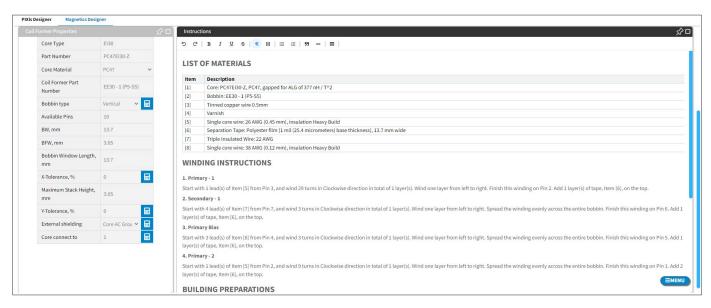

When using the PIXIs tool, it is important to iterate the design until no more warnings are present. Warnings can be addressed by following the guidance given in the right most column of the spreadsheet. Once all warnings are cleared, use the magnetics designer tool to optimize the transformer and then generate the design documents that can be used to create a prototype transformer.

#### 6.1 Application Variables and Operating Conditions

Enter the desired output voltage and the target output power for each input voltage set point. Up to 9 operating conditions can be specified and PIXIs will attempt to solve for a design that will satisfy all operating points. Figure 3 shows the Application Variables section of the PIXIs for InnoSwitch3-AO devices.

For power supplies with a specified operating input range but has output power requirements below the minimum, it is recommended to enter only the nominal range in the Operating Conditions fields and then use Set-Point Analysis to evaluate the design at lower input voltages. See the Set-Point Analysis section for an example.

| PIXIs<br>Desig                             | 9                     |          |      |         |       |                                              |

|--------------------------------------------|-----------------------|----------|------|---------|-------|----------------------------------------------|

| DCDC_InnoSwitch3AQ_Flyback_031423; Rev.3.5 |                       | .5 INPUT | INFO | ОИТРИТ  | UNITS | InnoSwitch3-AQ Flyback Design<br>Spreadsheet |

| •                                          | APPLICATION VARIABLES |          |      |         |       | Design Title                                 |

| 3                                          | VOUT                  | 12.00    |      | 12.00   | V     | Output Voltage                               |

| 4                                          | OPERATING CONDITION 1 |          |      |         |       |                                              |

| 5                                          | VINDC1                | 1000.00  |      | 1000.00 | V     | Input DC voltage 1                           |

| 6                                          | IOUT1                 | 5.000    |      | 5.000   | A     | Output current 1                             |

| 7                                          | POUT1                 |          |      | 60.00   | W     | Output power 1                               |

| 8                                          | EFFICIENCY1           |          |      | 0.85    |       | Converter efficiency for output 1            |

| 9                                          | Z_FACTOR1             |          |      | 0.50    |       | Z-factor for output 1                        |

| 10                                         |                       |          |      |         |       |                                              |

| 11                                         | OPERATING CONDITION 2 |          |      |         |       |                                              |

| 12                                         | VINDC2                | 300.00   |      | 300.00  | V     | Input DC voltage 2                           |

| 13                                         | IOUT2                 | 5.000    |      | 5.000   | Α     | Output current 2                             |

| 14                                         | POUT2                 |          |      | 60.00   | W     | Output power 2                               |

| 15                                         | EFFICIENCY2           |          |      | 0.85    |       | Converter efficiency for output 2            |

| 16                                         | Z_FACTOR2             |          |      | 0.50    |       | Z-factor for output 2                        |

| 17                                         |                       |          |      |         |       |                                              |

| 18                                         | OPERATING CONDITION 3 |          |      |         |       |                                              |

| 19                                         | VINDC3                | 60.00    |      | 60.00   | ٧     | Input DC voltage 3                           |

| 20                                         | IOUT3                 | 0.500    |      | 0.500   | Α     | Output current 3                             |

| 21                                         | POUT3                 |          |      | 6.00    | W     | Output power 3                               |

| 22                                         | EFFICIENCY3           |          |      | 0.85    |       | Converter efficiency for output 3            |

| 23                                         | Z_FACTOR3             |          |      | 0.50    |       | Z-factor for output 3                        |

Figure 3. Enter the Desired VOUT and Output Power for Each Corresponding Input Voltage.

#### Notes:

- **1. VOUT** Recommended  $V_{OUT}$  range is from 5 VDC to 24 VDC

- The InnoSwitch3-AQ VOUT pin has an absolute maximum voltage of 27 V. For designs requiring outputs >24 VDC, please contact Power Integrations customer support.

- VINDC Maximum input voltage is 1100 VDC while the minimum is 30 VDC.

- 3 EFFICIENCY Use the default values for the first iteration of the design. This can be adjusted to match bench measurements once a prototype is available.

- 4. Z-FACTOR Power Supply Loss Allocation Factor Equal to the ratio of the losses in the secondary-side over the total converter losses. Use the default value for I<sub>OUT</sub> of 3 A and below. A value of 0.65 can be used for higher output currents. If there is a need to optimize calculations, a power loss budget measured from the prototype can be used to determine the actual secondary losses, and the Z-factor can be iterated in the spreadsheet.

- If line undervoltage protection is disabled (V pin shorted to SOURCE pin), the power supply will start to operate at 30 VDC input. Use the INPUT VOLTAGE SET-POINT ANALYSIS section of the PIXIs to determine the expected maximum output power at this operating point.

- For wide-range input designs (e.g., 30 VDC to 1000 VDC), higher power requirements at the minimum input voltage will limit the maximum output power at higher input voltages due to increased switching losses (deep DCM operation at high input voltage, no valley switching, higher switching frequency).

- It is not necessary to fill up all operating conditions fields.

Required power at the minimum and maximum input voltages will suffice.

#### **6.2 Primary Controller Selection**

Use the Table 1 InnoSwitch3-AQ Output Power Table to select the appropriate InnoSwitch3-AQ IC for the design.

Adjust the DEVICE\_CODE field to the chosen InnoSwitch3-AQ device. For the ILIMIT\_MODE, select between STANDARD or INCREASED.

In general, INCREASED current limit is selected when designing near the maximum power capability of the device or when higher power is needed in the lower input ranges of the design.

The primary controller selection section is shown in Figure 4. Upon selecting the current limit and device code, the device's characteristics are listed in the succeeding cells based on data sheet values.

#### **Design Notes:**

- It is possible to design for higher power versus the values stated in the power table if thermal management measures are implemented to keep the package temperature below 125 °C.

- Always estimate the total power loss in the device (switching + conduction losses) to appropriately size the cooling copper area of the SOURCE node.

- Refer to the InnoSwitch3-AQ data sheet for information on the devices' thermal impedance and Drain-Source capacitance.

#### **Output Power Table**

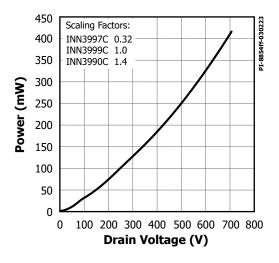

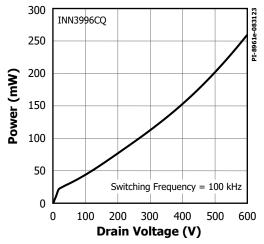

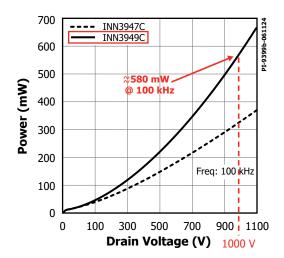

| Product <sup>2</sup>   | Output Power (W)<br>At Working Voltage <sup>1</sup> |        |        |         |         |  |

|------------------------|-----------------------------------------------------|--------|--------|---------|---------|--|

| 750 V MOSFET           |                                                     | 30 VDC | 60 VDC | 400 VDC | 800 VDC |  |

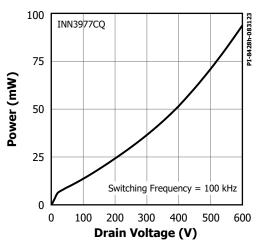

| INN3977CQ              | 520 V                                               | 10     | 20     | 30      | _       |  |

| 900 V MOSFET           | •                                                   | 30 VDC | 60 VDC | 400 VDC | 800 VDC |  |

| INN3996CQ              | 650 V                                               | 7      | 14     | 20      | _       |  |

| 900 V PowiGal          | l Switch                                            | 30 VDC | 60 VDC | 400 VDC | 800 VDC |  |

| INN3997CQ3             | 650 V                                               | 10     | 20     | 55      | _       |  |

| INN3999CQ <sup>3</sup> | 650 V                                               | 10     | 30     | 85      | _       |  |

| INN3990CQ <sup>3</sup> | 650 V                                               | 10     | 40     | 100     | _       |  |

| 1700 V SiC Sw          | itch                                                | 30 VDC | 60 VDC | 400 VDC | 800 VDC |  |

| INN3947CQ              | 1200 V                                              | 10     | 23     | 50      | 50      |  |

| INN3949CQ              | 1200 V                                              | 10     | 40     | 70      | 70      |  |

Table 1. Output Power Table. Notes:

- Maximum output power is dependent on the design. Power delivery is calculated assuming that package temperature must be < 125 °C and that the design uses suitable thermal strategies (e.g. PCB copper area and/or a thermal interface to enclosure).

- Packages: InSOP-24D.

- 4. Transients may exceed this value.

| PIXIs<br>Desig |                                       |                    |      |           |       | <b>✓</b>                                                     |

|----------------|---------------------------------------|--------------------|------|-----------|-------|--------------------------------------------------------------|

| DCDC_I         | InnoSwitch3AQ_Flyback_031423; Rev.3.5 | INPUT              | INFO | OUTPUT    | UNITS | InnoSwitch3-AQ Flyback Design Spreadsheet                    |

| •              | APPLICATION VARIABLES                 |                    |      |           |       | Design Title                                                 |

| 68             |                                       |                    |      |           |       |                                                              |

| •              | PRIMARY CONTROLLER SELECTION          |                    |      |           |       |                                                              |

| 70             | ILIMIT_MODE                           | INCREASED >        |      | INCREASED |       | Device current limit mode                                    |

| 71             | VDRAIN_BREAKDOWN                      | 1700 🗸             |      | 1700      | V     | Device breakdown voltage                                     |

| 72             | DEVICE_GENERIC                        |                    |      | INN39X9   |       | Device selection                                             |

| 73             | DEVICE_CODE                           | INN3949CQ <b>▽</b> |      | INN3949CQ |       | Device code                                                  |

| 74             | PDEVICE_MAX                           |                    |      | 70        | W     | Device maximum power capability                              |

| 75             | RDSON_25DEG                           |                    |      | 0.62      | Ω     | Primary switch on-time resistance at 25°C                    |

| 76             | RDSON_125DEG                          |                    |      | 1.10      | Ω     | Primary switch on-time resistance at 125°C                   |

| 77             | ILIMIT_MIN                            |                    |      | 1.981     | A     | Primary switch minimum current limit                         |

| 78             | ILIMIT_TYP                            |                    |      | 2.130     | A     | Primary switch typical current limit                         |

| 79             | ILIMIT_MAX                            |                    |      | 2.279     | A     | Primary switch maximum current limit                         |

| 80             | VDRAIN_ON_PRSW                        |                    |      | 0.24      | V     | Primary switch on-time voltage drop                          |

| 81             | VDRAIN_OFF_PRSW                       |                    |      | 1180      | V     | Peak drain voltage on the primary switch during turn-<br>off |

Figure 4. InnoSwitch3-AQ Device and Current Limit Setting in the Primary Controller Selection Section of PIXIs.

#### 6.3 Worst-Case Electrical Parameters

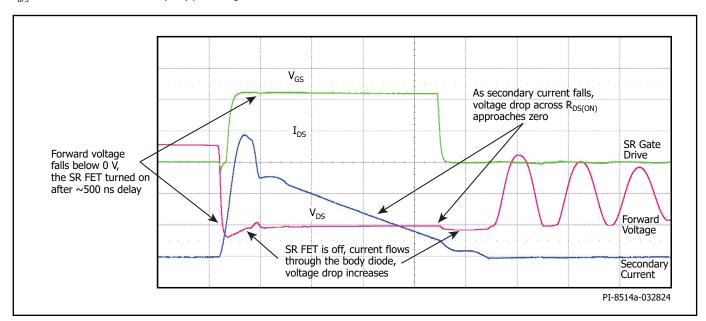

Most iterations will be done in this spreadsheet section until a suitable transformer design is achieved. For the first iteration of the design, the default values of FSWITCHING\_MAX, VOR, and LPRIMARY\_TOL can be used. Once a transformer core is selected, the user can adjust the value of these variables until PIXIs clears all warnings.