# 1SP0635V2A0D SCALE-2 Family

Gate Driver for IGBT Modules up to 3300 V Versatile Fiber-Optic Interface

# **PRELIMINARY**

# **Product Highlights**

# **Highly Integrated, Compact Footprint**

- Ready-to-use gate driver solution for power modules up to 3300 V blocking voltage

- Single-channel gate driver

- 35 A peak output gate current

- 3 W output power at maximum operating temperature

- Supports parallel connection of up to four power modules

- -40 °C to +85 °C operating ambient temperature range

- · Optical status indicator

## **Protection / Safety Features**

- Short-circuit protection

- Dynamic Advanced Active Clamping (DA<sup>2</sup>C)

- Undervoltage lock-out (UVLO) protection

- NTC temperature sensing

- DC-link voltage measurement at 75 kHz

- Gate monitoring

- Double-sided conformally coated (ELPEGUARD SL 1307 FLZ/4 from Lackwerke Peters)

- RoHS compliant

# **Applications**

- Railway inverter

- Industrial drives

- Other industrial applications

# **Description**

The Plug-and-Play 1SP0635V2A0D gate driver is a compact singlechannel intelligent gate driver designed to support a range of IGBT modules. It features a versatile fiber-optic interface.

The 1SP0635V2A0D is designed to work with an isolated DC-DC converter ISO6125R-33, which needs to be purchased separately as it is not integrated into the driver.

Power Integrations' Dynamic Advanced Active Clamping allows an extended DC-link voltage range to support the IGBT off-state for up to 60 seconds. This is ideal for railway and regenerating applications.

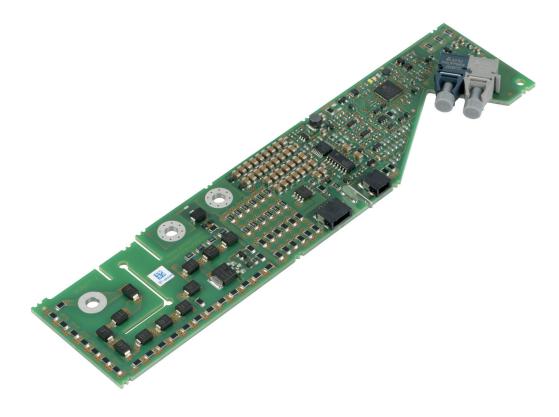

Figure 1. Product Photo of 1SP0635V2A0D.

# **Pin Functional Description**

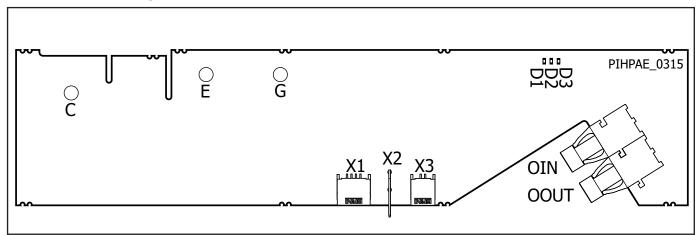

Figure 2. 1SP0635V2A0D Interfaces.

#### **Connector X1**

ERNI interface to connect main driver external DC-DC converter. <u>Part number:</u> ERNI 504255-E, 4 pin, right angle.

#### COM (Pins 1, 4)

This pins are the connection to secondary-side ground potential.

#### **VISO (Pins 2, 3)**

This pins are the connection to secondary-side supply voltage.

#### **Connector X2**

Quick FIT terminal to DC-link measuring input Part number: Ettinger 019.25.131.

#### **Connector X3**

ERNI interface for NTC measurement. <u>Part number:</u> ERNI 504235-E, 2 pin, right angle.

## NTC (Pin 1)

This pin is the first NTC terminal.

# COM (Pin 2)

This pin is the second NTC terminal.

#### **Connection to Semiconductor**

# **Terminal G**

Gate contact of IGBT.

#### **Terminal E**

Auxiliary emitter contact of IGBT.

## **Terminal C**

Auxiliary collector contact of IGBT.

# **Fiber-Optic Interface**

Main driver to external controller (fiber optic receiver and transmitter).

#### **OIN (Receiver)**

This fiber optic receiver is the command input. <u>Part number:</u> Broadcom HFBR-2522ETZ

#### **OOUT (Transmitter)**

This fiber optic transmitter is the status output. <u>Part number:</u> Broadcom AFBR-1529Z

# **Optical Indicators**

For easy verification of the operation of the gate driver.

#### D1

White LED for monitoring the power supply. The indicator is turned on when the driver is supplied with voltage.

#### D2

Green LED for monitoring the status of optic input. The indicator is turned on when the driver receives a turn-on command.

#### **D3**

Red LED for monitoring the fault status.

The LED is turned ON and keeps to light ON upon a Fault detected by the driver (i.e. VCE-short-circuit detection (SC\_VCE), undervoltage monitoring high (UVLO\_POS) or low (UVLO\_NEG).

The LED is turned OFF at the next turn-on command under the condition that all Fault conditions are cleared.

# **Functional Description**

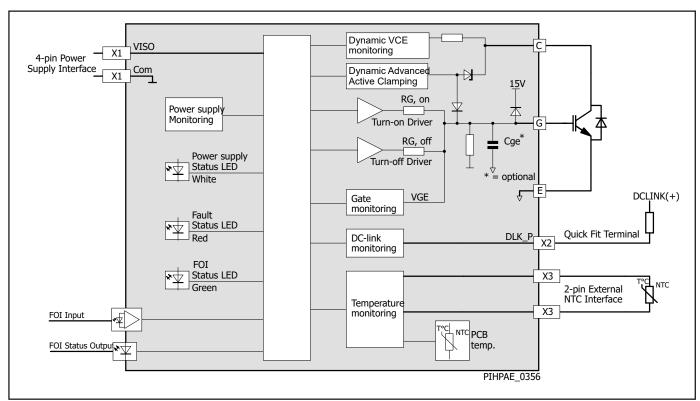

The basic topology of the 1SP0635V2A0D driver is shown in Figure 3. This driver is a single-channel intelligent gate driver. The driver is equipped with the following features:

- Dynamic V<sub>CF</sub> monitoring (short-circuit protection)

- Dynamic Advanced Active Clamping DA<sup>2</sup>C (overvoltage protection at turn-off)

- Gate monitoring

- NTC temperature sensing

- · DC-link voltage measurement at 75 kHz

- · Gate clamping to the positive rail

- Power supply monitoring

The driver 1SP0635V2A0D is not equipped with a DC-DC converter. The signals are isolated with versatile fiber optics links. The power supply (isolated DC-DC converter ISO6125R-33) has not been integrated in the driver. It is a separate unit. The signals are isolated with versatile fiber optics links.

Plug-and-play capability means that the drivers are ready to operate immediately after mounting. The user does not need to invest any effort in designing or adjusting the driver to match a specific application.

#### Description of X1, X2 and X3

The main driver is equipped with a 4-pin interface connector X1. It is recommended to connect both COM and VISO pins.

The X2 connector is the input for measuring the DC-link voltage through an external resistor connected to the DC-link. It is referred to the emitter voltage. This feature is only available for low-side drivers (in two-level applications). For the HS driver, the signal must be left unconnected. The X3 connector provides an interface from the External NTC thermistor to the driver measuring input.

#### **Screw Terminals**

The main driver is mounted on top of the power module and fixed by screws.

#### **Connection Cables for X1**

For recommended cables, please refer to data sheets RLC-PSI-641-050-0.

#### **Power Supplies and Electrical Isolation**

The power supply shall be an isolated DC/DC converter such as Power Integration ISO6125R-33.

#### **Fiber Optic Receiver OIN**

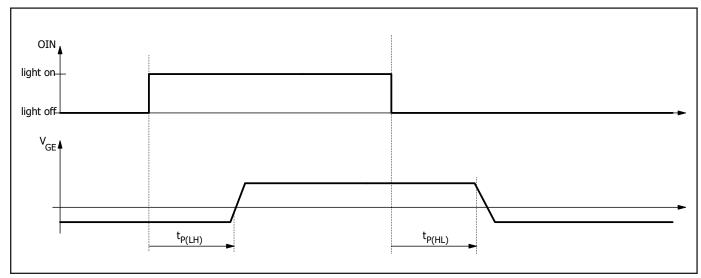

The input signal OIN is received by a fiber optic receiver. OIN has a positive logic (light on implies turn-on) and is edge-triggered. The gate driver signal is transferred from the OIN receiver to the gate with a propagation delay of  $t_{\text{P(LH)}}$  for the turn-on and  $t_{\text{P(HL)}}$  for turn-off commands as illustrated in Figure 5. Filtering is implemented to ensure that any positive or negative command pulses below  $t_{\text{FILTER(ON\_PULSE)}}$  and respectively  $t_{\text{FILTER(ON\_PULSE)}}$  are not transmitted to the Gate.

#### **Fiber Optic Transmitter OOUT**

The status output signal OOUT is transmitted by a fiber optic transmitter to external control. OOUT provides a data stream according to a UART protocol described in the section "Data Protocol".

#### **Short-Circuit Detection**

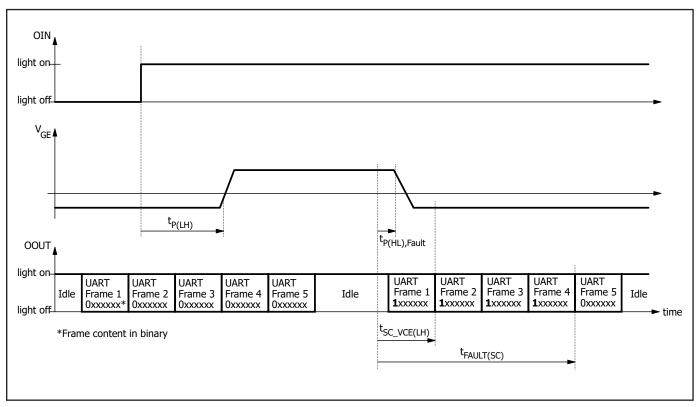

Figure 6 shows the response of the driver in the event of a short-circuit fault. Upon the short circuit detection, a delay of  $t_{\text{P(HL),FAULT}}$  is applied before the IGBT is turned off. The status bit SC\_VCE of the status register is set to binary '1' and it is transferred to the status output OOUT feedback terminal with a delay of response time  $t_{\text{SC,VCE(LH)}}.$

The IGBT can be turned on again by applying a positive edge to the fiber-optic input after the fault status has disappeared and a successive period of  $t_{\scriptscriptstyle BLK}$  has elapsed. The fault status LED is also enabled upon fault detection.

Figure 3. Functional Block Diagram.

#### **Undervoltage Detection**

In the event of an undervoltage fault being detected on either the VISO-VEE or VEE-COM supply voltages, the fault status remains active and the driver is locked for as long as the undervoltage remains. In case the VISO-VEE or the VEE-COM goes in undervoltage, the status bit UVLO\_POS respectively UVLO\_NEG of the status register is set to binary '1' after a delay time response of  $t_{\mbox{\tiny UVLO(LH)}}$ .

The status bits are cleared after the fault status has disappeared and the IGBT can be turned on again by applying a positive edge to the fiber-optic input after a successive blocking time  $t_{\scriptscriptstyle BLK}$  is elapsed. The fault status LED is also enabled upon fault detection.

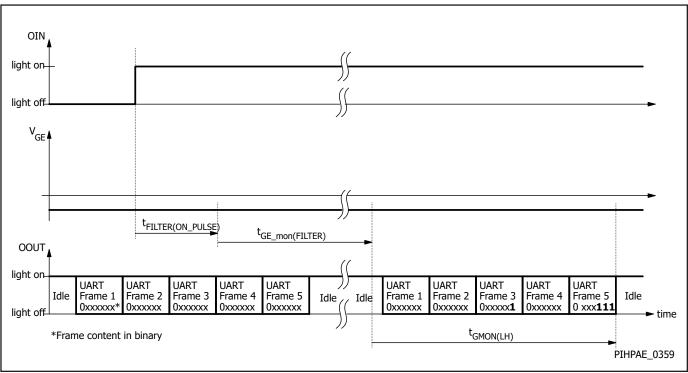

#### **Gate Monitoring Warning Detection**

When the Gate-Emitter voltage goes below the threshold  $V_{\text{GE\_mon(ON)}}$  or  $V_{\text{GE\_mon(OFF)'}}$  after a delay time  $t_{\text{GE\_mon(FILTER)}}$  following the VGE switching, the warning status bit VGE\_STAT\_HI respectively VGE\_STAT\_HI of the status register is set to binary '1' and transferred to the fiber optic transmitter with a delay of the response time  $t_{\text{GMON(LH)}}$ . Figure 7 illustrates the Gate monitoring timing.

#### **DC-Link Voltage Monitoring**

The driver comprises an input to measure the DC-link voltage referred to the Emitter voltage. This feature is only available for the low-side driver of a 2 Level System Converter. The X2 connector has to be connected to a high voltage-rated external resistance to the DC-Link source.

The DC-link measured value is transferred to the optical transmitter OOUT through the DLK[11.0] data bit fields at a rate of  $S_{\tiny DLK}$ . The response time to reach 95% of the measured value is given by  $t_{\tiny DLK}$ . Both measuring range  $V_{\tiny DLK,\,RANGE}$  and measuring output resolution  $V_{\tiny DLK,\,RES}$  are specified according to a specific value of external resistance (refer to characteristics section).

#### Please note the following:

- Precautions shall be considered when connecting the external resistance to the X2 input to minimize the connecting loop and any undesired coupling that may affect the measurement accuracy.

- For the high-side driver, the X2 input must be either left unconnected or connected to the driver emitter, and the data bit fields DLK[11.0] returned by the optical transmitted ignored.

# **PCB NTC Temperature Monitoring**

The driver is assembled with a thermistor measuring the driver's PCB temperature. The measured temperature value is transferred to the optical transmitter OOUT through the DAT[11.0] data bit fields at a rate of  $\rm S_{NTC1}$  (for the data format, refer to the sub-section "NTC Temperature" of the "Protocol section)". The response time to reach 95% of the measured value is  $\rm t_{NTC1}$ . The measuring range is defined by the parameter  $\rm V_{NTC1\_RANGE}$  and measuring output resolution is defined by the parameter  $\rm V_{NTC1\_RES}$ .

#### **External NTC Temperature Monitoring**

The driver comprises a connector (X3) available for connecting an external NTC thermistor for measuring for instance heatsink temperature. The measured external temperature value is transferred to the optical transmitter OOUT through the DAT[11.0] data bit field at a rate of  $S_{\mbox{\scriptsize NTC2}}$  (for the data format, refer to sub-section "NTC Temperature" of the "Protocol section)". The response time to reach 95% of the measured value is given by  $t_{\mbox{\scriptsize NTC2}}$ . The measuring range is defined by the parameter  $V_{\mbox{\scriptsize NTC2}}$  and measuring output resolution is defined by the parameter  $V_{\mbox{\scriptsize NTC2}}$  res.

The NTC shall be electrically isolated according to the system isolation requirements. Both external NTC terminals shall not be connected to any external potential such as the emitter or the collector.

In case the external NTC is unused, the connector X3 shall be left unconnected. A Missing or unconnected NTC thermistor will generate a constant negative full-scale value in the DAT[11..0] data bit field.

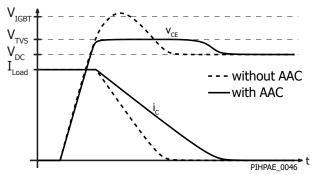

#### Dynamic Advanced Active Clamping (DA<sup>2</sup>C)

Active clamping acts to partially turn on the IGBT if the collectoremitter voltage exceeds a predefined threshold. The IGBT is then kept in linear operation. Basic active clamping topologies implement a single feedback path from the IGBT's collector through transient voltage suppressor (TVS) diodes to the IGBT gate. The gate driver in 1SP0635V2A0D contains Power Integrations' Dynamic Advanced Active Clamping (DA²C) that operates as follows:

When active clamping is activated, the turn-off MOSFET for the gate driver is switched off in order to improve the effectiveness of the active clamping and to reduce the losses in the TVS diodes. This feature is called as Advanced Active Clamping (AAC). The principle of AAC is illustrated in Figure 4.

Figure 4. Advanced Active Clamping.

Additional TVS diodes are added in series with the TVS diodes required to withstand the maximum DC-link voltage during switching. These TVS diodes are short-circuited during the IGBT on-state for about 15 to 20  $\mu s$  after the turn-off command is received to ensure efficient active clamping. After this delay, these additional TVS diodes are activated and allow the DC-link voltage to be increased to a higher value during the IGBT off-state. This feature together with Advanced Active Clamping – is called Dynamic Advanced Active Clamping (DA^2C). Note that the time that the voltage can be applied above the value for switching operation should be limited to short periods (< 60s).

#### **Blocking Time**

After a short circuit detection or an undervoltage detection, the gate signal is turned off for a period of  $t_{\text{BLK}}$  and the status bit G\_BLOCKING of the status register is maintained to binary '1' during the whole period and goes to binary '0' afterward.

#### **Self-Test**

A driver internal self-test is implemented to check driver functionalities. The warning status bit "ST" of the status register is set to binary '1' in case the self-test detects parameters outside the expected range. Otherwise, the "ST" status bit is set to binary '0'.

#### **Dynamic Behavior of IGBT**

Due to the different behavior of the included IGBT and diode chips, the dynamic behavior of the IGBT module depends on their type and manufacturer. Module construction and the distribution of the internal gate resistances and inductances also play a role in determining dynamic response. Note that different module types from the same manufacturer may also require a specific gate-driver adaptation.

Power Integrations, therefore, supplies specific versions of SCALETM-2 plug-and-play drivers adapted to each type of IGBT module. These drivers must not be used with IGBT modules other than those for which they were specified.

Figure 5. Driver Gate Signal in Normal Operation Mode.

$\label{eq:Figure 6.} \textbf{Fiber Optic Feedback from the Driver in Short-Circuit Fault Mode.}$

# Turn-On of the IGBT / Commutation of Diode Current

When a driver input goes high (light on), the gate driver turns on the corresponding IGBT. The driver includes the gate resistors, matched to the appropriate IGBT module.

The driver is optimized to achieve minimum switching losses when paired with relatively low inductances within the power stack. It is therefore recommended to check the commutation behavior of the system assembly.

#### **Turn-Off of the IGBT**

The IGBT is turned off when the corresponding input turns low (light off). The gate resistance is already optimized and should not be altered.

Fast turn-off of the IGBT may cause overvoltage, which increases with DC-link voltage or load current. The turn-off overvoltage is approximately:

$$V_{TR} = L_S x di_C/dt$$

where  $\rm V_{TR}$  is the turn-off overvoltage,  $\rm i_{\rm C}$  is the collector current and  $\rm L_{\rm S}$  is the stray inductance.

Limiting overvoltage at turn-off is essential for high-power or high-voltage IGBTs. To ensure this, SCALE-2 plug-and-play drivers provide a Dynamic Advanced Active Clamping function DA<sup>2</sup>C.

# PRELIMINARY

Figure 7. Fiber Optic Feedback of the Driver in Normal Operation Mode.

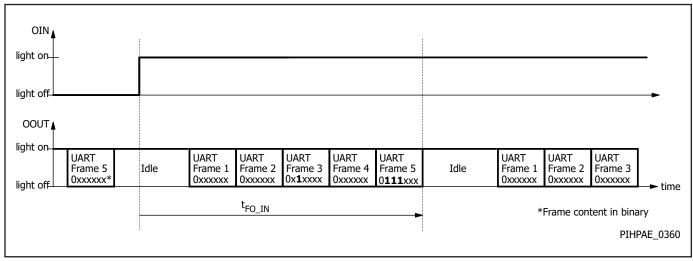

Figure 8. Fiber Optic Status Register Bit in Normal Operation Mode.

#### **Data Protocol**

The fiber optical output provides a signal according to Power Integrations' proprietary protocol. It is based on the UART protocol.

#### **UART Frame**

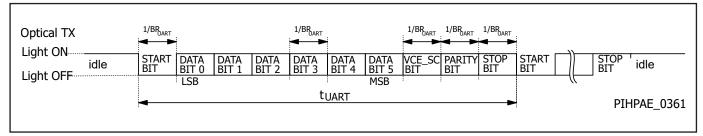

Figure 9 shows the timing of the UART frame and the polarity of the optical transmitter. Each UART frame of the protocol comprises 1 start bit, 6 data bits (DATA BIT 0 ... 5), 1 VCE\_SC (short-circuit) data bit, 1 parity bit (even), and 1 stop bit. The length of an UART frame is defined by  $t_{\mbox{\tiny UART}}$  and the bit rate by  $BR_{\mbox{\tiny UART}}$ . Both start bit and stop bit have a length of 1 bit. The least significant bit (LSB) of the data is sent first. This means that after sending the start bit, the DATA BIT 0 is sent and before sending the STOP BIT, the parity bit is sent.

The parity bit is defined as the even parity calculation of the following bit fields: DATA BIT 0 to DATA BIT 5 and the SC\_VCE bit. The status bit SC\_VCE bit indicates a short-circuit detection. The polarity of the bit related to the optical transmitter is defined as follows:

- the start bit is a transition from light ON to light OFF

- the stop bit is a transition from light OFF to light ON

- a logical low data (including VCE\_SC) is defined as a light ON

- a logical high data (including VCE\_SC) is defined as a light OFF

- the idle state is defined as a light ON

#### **Data Packet**

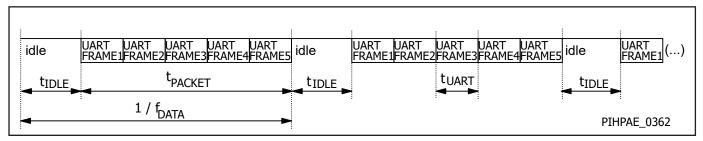

The protocol is defined in such a way a data packet of five consecutive UART frames (as in Figure 9) is sent periodically at a rate of  $f_{DATA}$  (refer to Figure 10). The data packet length is defined as  $t_{PACKET}$  and between two packets there is an idle time of  $t_{IDLE}$  where no data are transmitted.

#### **Short Circuit Detection and Idle Time**

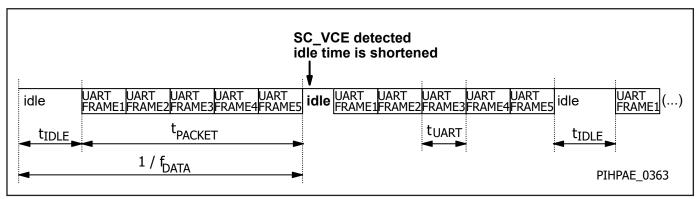

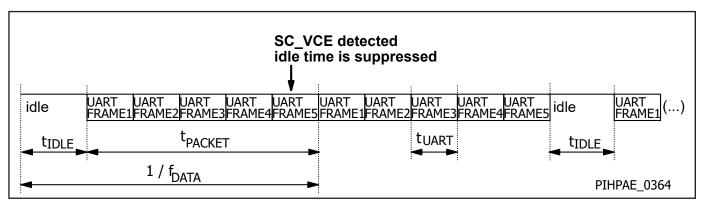

As the protocol is asynchronous to any VCE short-circuit detection, depending on the time of the VCE short circuit detection, the idle time might be reduced to inform the host controller about the event. Both Figure 11 and Figure 12 show examples where the idle time  $t_{\tiny IDLE}$  and data frequency  $f_{\tiny DATA}$  are impacted.

#### **Data Packet Format**

Each data packet meets the format illustrated below:

| SC_VCE                | MSB<br>Data<br>bit5 | Data<br>bit4 | Data<br>bit3 | Data<br>bit2 | Data<br>bit1 | LSB<br>Data<br>bit0 |

|-----------------------|---------------------|--------------|--------------|--------------|--------------|---------------------|

| UART<br>FRAME1 SC_VCE |                     | DLK[4]       | DLK[3]       | DLK[2]       | DLK[1]       | DLK[0]              |

| UART<br>FRAME2 SC_VCE | DLK[11]             | DLK[10]      | DLK[9]       | DLK[8]       | DLK[7]       | DLK[6]              |

| UART<br>FRAME3 SC_VCE | DAT[5]              | DAT[4]       | DAT[3]       | DAT[2]       | DAT[1]       | DAT[0]              |

| UART<br>FRAME4 SC_VCE |                     | DAT[10]      | DAT[9]       | DAT[8]       | DAT[7]       | DAT[6]              |

| UART<br>FRAME5 SC_VCE |                     | ADR[1]       | ADR[0]       | CRC[2]       | CRC[1]       | CRC[0]              |

PIHPAE\_0365

#### **Data Bit Fields Description**

#### SC-VCE

This is a status bit that indicates when a VCE short-circuit is detected. It is set to binary '1' when a VCE short-circuit is detected or else to binary '0'. When a VCE short-circuit is detected, the SC-VCE bit is updated at the host side with a delay of  $\mathbf{t}_{\text{SC-VCE(LH)}}$ .

## DLK[11]..DLK[0]

These 12 bits are used for the DC-link measurement value. The format is an unsigned integer, and the resolution is 1V. The DC-link data is refreshed with a  $S_{\text{DI}\,\text{K}}$  rate.

Example of data DLK[11..0] value and its corresponding DC-link value: 1001 1100 0100 = 2500V

#### ADR[2]..ADR[0]

These three bits are address bits. They are used to define the content of the data value returned in *DAT[11..0]*.

| ADR[2] | ADR[1]         | ADR[0]                 | DAT[110]                 |

|--------|----------------|------------------------|--------------------------|

| 1      | 1              | 1                      | Status register          |

| 1      | 0              | 1                      | External NTC temperature |

| 1      | 1 1 0          |                        | PCB NTC temperature      |

| Oth    | er combination | Reserved for other use |                          |

#### DAT[11]..DAT[0]

The data of 12 data bits is defined by the address ADR[2..0]. It is refreshed with a rate defined by  $f_{\text{DATA}}$ . In normal operation (no VCE short-circuit detected), the Data Register is updated as the following sequence:

- The Status Register is copied and transferred to DAT[11..0] at the rate f<sub>DATA</sub> during 31 consecutive cycles.

- One value of the PCB NTC temperature is transferred to DAT[11..0] during one cycle.

- The Status Register is copied and transferred to DAT[11..0] at the rate  $f_{\text{DATA}}$  during 31 consecutive cycles.

- One value of the External NTC temperature is transferred to DAT[11..0] during one cycle.

Both PCB NTC temperature and External NTC temperature are refreshed with  $S_{\mbox{\tiny NTC1}}$  and  $S_{\mbox{\tiny NTC2}}$  rates respectively. In the case of a VCE short-circuit detection, the above sequence is restarted.

Figure 9. UART Frame Timing and Optical Transmitter Polarity.

Figure 10. Data Packet Timing in Normal Operating Condition.

Figure 11. Data Packet Timing for a Short Circuit Condition Detected During Idle.

Figure 12. Data Packet Timing for a Short Circuit Condition Detected at the End of Data Packet.

#### **Status Register**

The status register contains 12 bits, to indicate the driver status.

| Status<br>Register | Bit Name    | Description                                                                                                                                                                                                                                                                   |

|--------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SR[11] (MSB)       |             | Unused                                                                                                                                                                                                                                                                        |

| SR[10]             |             | Unused                                                                                                                                                                                                                                                                        |

| SR[9]              |             | Unused                                                                                                                                                                                                                                                                        |

| SR[8]              |             | Unused                                                                                                                                                                                                                                                                        |

| SR[7]              | G_BLOCKING  | Gate blocking status bit. Set to binary 1 when the gate output is blocked or else to binary '0'                                                                                                                                                                               |

| SR[6]              | SUM_FAILURE | Sum failure status bit. Set to binary<br>'1' when at least one Failure bit is<br>set and set to binary '0' when all<br>failure bits are cleared. The sum<br>includes the status of VCE_SC fault<br>and both unvervoltage monitoring<br>faults VGE_STAT_HI and VGE_<br>STAT_LO |

| SR[5]              | ST          | Driver self-test warning status bit.<br>Set to binary '1' when an internal<br>Failure is detected or else to binary<br>'0'                                                                                                                                                    |

| SR[4]              | IN_STAT     | Optical fiber receiver status bit.<br>Set to binary '1' when a turn-on<br>command is sent or else set to<br>binary '0'                                                                                                                                                        |

| SR[3]              | UVLO_POS    | Undervoltage fault status bit of VISO-VEE. Set to binary '1' when a failure is detected or else to binary '0'                                                                                                                                                                 |

| SR[2]              | UVLO_NEG    | Undervoltage fault status bit of VEE-COM. Set to binary '1' when a failure is detected or else to binary '0'                                                                                                                                                                  |

| SR[1]              | VGE_STAT_HI | Gate monitoring of Gate-Emitter<br>during ON-state, warning status<br>bit. Set to binary '1' when a warning<br>is detected or else to binary '0'                                                                                                                              |

| SR[0] (LSB)        | VGE_STAT_LO | Gate monitoring of Gate-Emitter<br>during OFF-state, warning status<br>bit. Set to binary '1' when a warn-<br>ing is detected or else to binary '0'                                                                                                                           |

## **NTC Temperature**

Both external NTC temperature and PCB NTC temperature are provided to the host through the data DAT[11..0] when the address ADR[2..0] is selected accordingly. The NTC measurement is provided through 12 bits unsigned, the resolution is 0.5K and the data is offset by 40K. The driver PCB NTC temperature data is refreshed with a rate defined by  $\rm S_{NTC1}$ . The external NTC temperature data is refreshed with a rate defined by  $\rm S_{NTC2}$ .

| Examle of data values DAT[110] | Temperature (°C) |

|--------------------------------|------------------|

| 0000 0000 0000                 | -40 °C (minimum) |

| 0000 0000 0001                 | -39.5 °C         |

| 0000 0100 1111                 | -0.5 °C          |

| 0000 0101 0000                 | 0 °C             |

| 0000 0101 0001                 | 0.5 °C           |

| 0001 0001 1000                 | 100 °C           |

| 0001 0101 0100                 | 130 °C (maximum) |

Note that unconnected NTC will generate a -40°C temperature value.

#### CRC[2..0]

These are a 3 bit Cyclic Redundancy Checks (CRC) covering the following bit fields respectively: DLK[5..0], DLK[11..6], DAT[5..0], DAT[11..6], ADR[2..0]. The CRC parameters calculation is as follows:

| ABIT[2110]1 THE CITE PARAMETERS C | alealacion is as follows: |

|-----------------------------------|---------------------------|

| CRC polynomial coefficient        | x^3 + x + 1               |

| CRC width                         | 3 bits                    |

| CRC shift direction               | right (little-endian)     |

| CRC initial value                 | 0                         |

# **Absolute Maximum Ratings**

| Parameter                                  | Symbol                | Conditions $T_A = -40 \text{ °C to } 85 \text{ °C}$ | Min | Max  | Units             |

|--------------------------------------------|-----------------------|-----------------------------------------------------|-----|------|-------------------|

| Absolute Maximum Ratings <sup>1</sup>      |                       |                                                     |     |      |                   |

| Supply Voltage                             | V <sub>VISO-COM</sub> | VISO to COM                                         |     | 28   | V                 |

| Average Supply Current                     | I <sub>DC</sub>       | Average supply current                              |     | TBD  | mA                |

| Gate Output Power <sup>2</sup>             | $P_{G}$               |                                                     |     | 3    | W                 |

| Switching Frequency                        | f <sub>sw</sub>       | Continuous                                          |     | 3    | kHz               |

|                                            |                       | Switching operation (continuous)                    |     | 2200 |                   |

| DC-Link Voltage                            | V <sub>DC-LINK</sub>  | Switching operation <sup>3</sup> (short-term)       |     | 2500 | V                 |

|                                            |                       | Off State⁴                                          |     | 3000 |                   |

| Operating Voltage                          | V <sub>CE</sub>       | Collector-emitter voltage                           |     | 3300 | V <sub>PEAK</sub> |

| Storage Temperature⁵                       | T <sub>ST</sub>       |                                                     | -40 | 50   | °C                |

| Operating Ambient Temperature              | T <sub>A</sub>        |                                                     | -40 | 85   | °C                |

| Component Surface Temperature <sup>6</sup> | T <sub>SURF</sub>     |                                                     |     | 125  | °C                |

| Relative Humidity                          | H <sub>R</sub>        | No condensation                                     |     | 95   | %                 |

| Altitude of Operation <sup>7</sup>         | A <sub>OP</sub>       |                                                     |     | 4000 | m                 |

| Voltage on X2 (DLK_P)                      |                       | Referenced to emitter voltage                       | -10 | 50   | V                 |

# **Recommended Operating Condition**

| Parameter      | Symbol                | Conditions<br>T <sub>A</sub> = -40 °C to 85 °C | Min  | Тур | Max  | Units |

|----------------|-----------------------|------------------------------------------------|------|-----|------|-------|

| Power Supply   |                       |                                                |      |     |      |       |

| Supply Voltage | V <sub>VISO-COM</sub> | VISO to COM                                    | 23.5 | 25  | 26.5 | V     |

### NOTES:

- 1. Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device.

- 2. Actually achievable maximum power depends on several parameters and may be lower than the given value. It has to be validated in the final system. It is mainly limited by the maximum allowed surface temperature.

- 3. This limit is only valid in on-state condition (switching) and must be limited to short periods of time (≤ 60 s). Note that this parameters may be limited to lower values for specific IGBT modules.

- 4. This limit is only valid in off-state condition (not switching) and must be limited to short periods of time (≤ 60 s).

- 5. The storage temperature inside the original package or in case the coating material of coated products may touch external parts must be limited to the given value. Otherwise, it is limited to 85 °C.

- 6. The component surface temperature, which may strongly vary depending on the operating condition, must be limited to the given value to ensure long-term reliability of the product.

- 7. Operation above this level requires a voltage derating to ensure proper isolation coordination.

# 1SP0635V2A0D

# **Characteristics**

| Parameter                                                                                             | Symbol                         | Conditions $V_{VISO-COM} = 25 \text{ V, } T_A = 25 \text{ °C}$                        |                                                                                                                                   | Min | Тур        | Max      | Units |

|-------------------------------------------------------------------------------------------------------|--------------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----|------------|----------|-------|

| Power Supply                                                                                          |                                | , , , , , ,                                                                           | Α                                                                                                                                 |     |            |          |       |

| Supply Current                                                                                        | T                              |                                                                                       | Without load                                                                                                                      |     | 44         |          | mA    |

| Зарріу Саптенс                                                                                        | I <sub>VISO-COM</sub>          | $P_{G} = 2.5 \text{ V}$                                                               | $V$ , $f_{SW} = 3$ kHz, 50% duty cycle                                                                                            |     | 149        |          | ША    |

|                                                                                                       |                                |                                                                                       | Clear fault (resume operation)                                                                                                    |     | 13.0       |          |       |

|                                                                                                       | UVLO <sub>VISO</sub>           |                                                                                       | Set fault (suspend operation)                                                                                                     |     | 13.5       |          | V     |

| Power Supply                                                                                          |                                | Referenced                                                                            | Hysteresis                                                                                                                        |     | 0.5        |          |       |

| Monitoring Threshold                                                                                  |                                | to E                                                                                  | Clear fault (resume operation)                                                                                                    |     | -5.2       |          |       |

|                                                                                                       | UVLO <sub>COM</sub>            |                                                                                       | Set fault (suspend operation)                                                                                                     |     | -5.4       |          | V     |

|                                                                                                       |                                |                                                                                       | Hysteresis                                                                                                                        |     | 0.2        |          |       |

| Power Supply<br>Monitoring Filter Time                                                                | t <sub>uvLo</sub>              |                                                                                       |                                                                                                                                   |     | 4.0        |          | μs    |

| Timing Characteristics                                                                                |                                |                                                                                       |                                                                                                                                   |     |            |          |       |

| Gate Turn-On Delay                                                                                    | t <sub>P(LH)</sub>             |                                                                                       | t ON to 10% of $V_{\text{GE(ON)}}$ , no load<br>Lm FO cable to external control,<br>pression time $t_{\text{PULSE(ON)}}$ included |     | 3.5        |          | μs    |

| Gate Turn-Off Delay                                                                                   | t <sub>P(HL)</sub>             |                                                                                       | OFF to 90% of $V_{\text{GE(OFF)}}$ , no load Lm FO cable to external control, pression time $t_{\text{FILTER(ON)}}$ included      |     | 3.6        |          | μs    |

| Minimal Gate Turn-On<br>Pulse Suppression Time                                                        | t <sub>FILTER(ON_PULSE)</sub>  |                                                                                       |                                                                                                                                   |     | 3.2        |          | μs    |

| Minimal Gate Turn-Off<br>Pulse Suppression Time                                                       | t <sub>FILTER(OFF_PULSE)</sub> |                                                                                       |                                                                                                                                   |     | 3.2        |          | μs    |

| Propagation Delay of<br>Fault Short Circuit to<br>UART at the Optical<br>Transmitter <sup>13</sup>    | t <sub>sc_vce(lh)</sub>        | Complete U                                                                            | JART frame. Parity and stop bits included.                                                                                        |     | 1.9 to 4.2 |          | μs    |

| Propagation Delay of<br>Fault Undevoltage to<br>UART at the Optical<br>Transmitter <sup>13</sup>      | t <sub>uvlo(LH)</sub>          |                                                                                       |                                                                                                                                   |     | TBD        |          | μs    |

| Propagation Delay<br>of Warning Gate<br>Monitoring to UART at<br>the Optical Transmitter <sup>s</sup> | t <sub>gmon(LH)</sub>          | Complete data packet, inclusing status register, CRC and UART stop bits are included. |                                                                                                                                   |     | TBD        |          | μs    |

| Propagation Delay of<br>OIN Status to UART at<br>the Optical Transmitter <sup>8</sup>                 | t <sub>oin</sub>               |                                                                                       |                                                                                                                                   |     | TBD        |          | μs    |

| Duration of Fault State<br>Short-Circuit Condition <sup>8</sup>                                       | t <sub>FAULT(SC)</sub>         |                                                                                       |                                                                                                                                   |     | 3 to 5 UAI | RT frame |       |

| Blocking Time                                                                                         | t <sub>BLK</sub>               |                                                                                       | After fault detection                                                                                                             |     | 20         |          | ms    |

# **Characteristics (Cont.)**

| Parameter                                         | Symbol                    | V <sub>VISO-</sub>      | <b>Conditions</b><br><sub>COM</sub> = 25 V, T <sub>A</sub> = 25 °C | Min | Тур  | Max  | Units |

|---------------------------------------------------|---------------------------|-------------------------|--------------------------------------------------------------------|-----|------|------|-------|

| <b>Short-Circuit Protection</b>                   |                           |                         |                                                                    |     | _    | _    |       |

| Static V <sub>CE</sub> -Monitoring<br>Threshold   | V <sub>CE(SAT)</sub>      |                         |                                                                    |     | 143  |      | V     |

|                                                   |                           | 10% to                  | DC-link voltage = 2400 V                                           |     | 7.5  |      |       |

| Response Time                                     | t <sub>res</sub>          | 90% of V <sub>GE</sub>  | DC-link voltage = 1800 V                                           |     | 7.7  |      | μs    |

|                                                   |                           |                         | DC-link voltage = 1200 V                                           |     | 8.0  |      | -     |

| Turn-Off Delay after<br>Short-circuit Detection   | t <sub>P(HL)FAULT</sub>   | '                       |                                                                    |     | 0.2  |      | μs    |

| Gate monitoring <sup>9</sup>                      |                           |                         |                                                                    |     |      |      |       |

| Turn-On Threshold                                 | V <sub>GE(ON)MAX</sub>    |                         | G to E, set fault                                                  |     | 12.9 |      | V     |

| Turn-Off Threshold                                | V <sub>GE(OFF)MIN</sub>   |                         | G to E, set fault                                                  |     | -7.8 |      | V     |

| Filter Delay                                      | +                         |                         | Turn-on                                                            |     | 30   |      | 116   |

| Filter Delay                                      | t <sub>D(FILTER)</sub>    |                         | Turn-off                                                           |     | 30   |      | μs    |

| DC-Link Voltage Measure                           | ment                      | ,                       |                                                                    |     | _    | _    |       |

| DC-Link measuring range <sup>10</sup>             | V <sub>DLK_RANGE</sub>    |                         |                                                                    | 0   |      | 3200 | V     |

| DC-Link measuring output resolution <sup>10</sup> | V <sub>DLK_RES</sub>      |                         |                                                                    |     | 1    |      | V     |

| DC-Link measuring<br>tolerances <sup>11</sup>     | tol <sub>DLK</sub>        | DC-Link vol             | tage between 500V and 3200V                                        |     | ±2   |      | %     |

| DC-Link filter frequency                          | f <sub>DLK</sub>          | Cut                     | t-off frequency at -3dB                                            |     | 10   |      | kHz   |

| DC-Link response time <sup>11</sup>               | t <sub>DLK</sub>          | Time to re              | each 95% of measured value                                         |     | 100  |      | μs    |

| DC-Link data refresh rate                         | S <sub>DLK</sub>          |                         |                                                                    |     | 75   |      | kHz   |

| Driver PCB Temperature (                          | (NTC <sub>1</sub> ) Measu | rement 12               |                                                                    | 1   |      |      |       |

| NTC <sub>1</sub> measuring range                  | V <sub>NTC1_RANGE</sub>   |                         |                                                                    | -40 |      | 130  | °C    |

| NTC <sub>1</sub> measuring output resolution      | V <sub>NTC1_RES</sub>     |                         |                                                                    |     | 0.5  |      | К     |

| NTC <sub>1</sub> measuring tolerances             | tol <sub>NTC1</sub>       | At temperature of 85 °C |                                                                    |     | ±3   |      | К     |

| NTC <sub>1</sub> filter frequency                 | f <sub>NTC1</sub>         | Cut                     | -off frequency at -3 dB                                            |     | 50   |      | Hz    |

| NTC <sub>1</sub> response time                    | t <sub>NTC1</sub>         | Time to r               | each 95% of measured value                                         |     | TBD  |      | ms    |

| NTC <sub>1</sub> data refresh rate                | S <sub>NTC1</sub>         |                         |                                                                    |     | 1.2  |      | kHz   |

# **Characteristics (Cont.)**

| Parameter                                    | Symbol                  | Conditions $V_{VISO-COM} = 25 \text{ V, } T_A = 25 \text{ °C}$         | Min | Тур | Max  | Units |

|----------------------------------------------|-------------------------|------------------------------------------------------------------------|-----|-----|------|-------|

| External Temperature (NTC <sub>2</sub> )     | Measurem                |                                                                        |     |     |      |       |

| NTC <sub>2</sub> measuring range             | V <sub>NTC2_RANGE</sub> |                                                                        | -40 |     | 130  | °C    |

| NTC <sub>2</sub> measuring output resolution | V <sub>NTC2_RES</sub>   |                                                                        |     | 0.5 |      | К     |

| NTC <sub>2</sub> measuring tolerances        | tol <sub>NTC2</sub>     | Temperature from -20 °C to 130 °C,<br>excluding external NTC tolerance |     | ±2  |      | К     |

| NTC <sub>2</sub> filter frequency            | f <sub>NTC2</sub>       | Cut-off frequency at -3 dB                                             |     | 50  |      | Hz    |

| NTC <sub>2</sub> response time               | t <sub>NTC2</sub>       | Time to reach 95% of measured value                                    |     | TBD |      | ms    |

| NTC <sub>2</sub> data refresh rate           | S <sub>NTC2</sub>       |                                                                        |     | 1.2 |      | kHz   |

| <b>UART Protocol Characteristics</b>         | •                       |                                                                        |     |     |      | '     |

| UART Baud Rate                               | BR <sub>UART</sub>      |                                                                        |     | 5   |      | MBd   |

| UART Baud Rate tolerance                     | BR <sub>UART_TOL</sub>  |                                                                        |     | 1   |      | %     |

| UART frame duration                          | t <sub>uart</sub>       | Start bit, data bits, parity bit and and Stop<br>bits included         |     | 2   |      | μs    |

| Data packet duration                         | t <sub>PACKET</sub>     | No short circuit detected                                              |     | 10  |      | μs    |

| Inter-data-packet delay                      | t <sub>IDLE</sub>       | No short circuit detected                                              |     | 3.3 |      | μs    |

| Data packet rate                             | f <sub>DATA</sub>       | No short circuit detected                                              |     | 75  |      | kHz   |

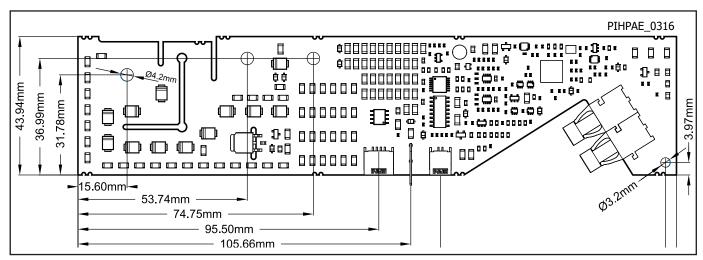

| Mounting <sup>14</sup>                       | '                       |                                                                        |     |     | '    | '     |

| Mounting Holes                               | D <sub>HOLE</sub>       | Diameter of screw hole S1                                              |     | 4   |      | mm    |

| Mounting Torque                              | М                       | Screw M4, as per IGBT data sheet                                       |     |     |      | Nm    |

| Bending                                      | I <sub>BEND</sub>       | According to IPC                                                       |     |     | 0.75 | %     |

| Gate Output                                  |                         |                                                                        |     |     |      |       |

| Turn-On Gate Output Voltage                  | V <sub>GE(ON)</sub>     | Steady-state                                                           |     | 15  |      | V     |

| Turn-Off Gate<br>Output Voltage              | $V_{\text{GE(OFF)}}$    | Steady-state                                                           |     | -10 |      | V     |

#### NOTES:

- 8. The specified delay shows a variation that depends on the asynchronous nature of the protocol.

- 9. The Gate-Emitter voltage value is filtered and compared to the given values at turn-on and turn-off. If the specified values are exceeded ( $V_{GE} < V_{GE\_mon(ON)}$  at turn-on respectively  $V_{GE} > V_{GE\_mon(OFF)}$  at turn-off) after the given filter delay  $t_{GE\_mon(FILTER)}$ , the driver sets a warning status bit in the status register.

- 10. With an external resistance value of  $4.32M\Omega$ .

- 11. Assessed with an exernal chain resistors of 16 series resistors of  $270k\Omega$ , 0.1% tolerances (i.e.  $4.32M\Omega$ ). Valid from DC-link measuring point to optical transmitter.

- 12. This is the tempeature measured on the driver PCB, which is typically higher than the ambient temperature by an amount of 10K to 20K.

- 13. The external temperature measurement is specified with a NTC with the following characteristics:  $R_{25} = 10 \text{ k}\Omega$ ,  $B_{25/85} = 3435 \text{ K}$ .

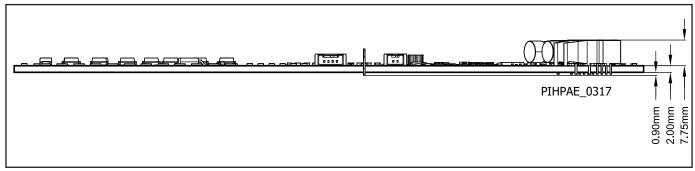

#### **Product Dimensions**

Figure 13. Top View.

Figure 14. Side View.

#### **Conformal Coating**

The electronic components in the gate driver are protected by a layer of acrylic conformal coating on both sides of the PCB with a typical thickness of  $50 \mu m$  using ELPEGUARD SL 1307 FLZ/4 from Lackwerke Peters. This coating layer increases product reliability when exposed to contaminated environments.

Note: Standing water (e.g. condensate water) on top of the coating layer must be prevented. This water will diffuse through the layer over time. If allowed to remain, it will eventually form a thin film between the PCB surface and coating layer, which will cause leakage currents to increase. Such currents will interfere with the performance of the gate driver.

# **Transportation and Storage Conditions**

For transportation and storage conditions refer to Power Integrations' Application Note AN-1501.

## **RoHS Statement**

We hereby confirm that the product supplied does not contain any of the restricted substances according to Article 4 of the RoHS Directive 2011/65/EU in excess of the maximum concentration values tolerated by weight in any of their homogeneous materials.

Additionally, the product complies with RoHS Directive 2015/863/EU (known as RoHS 3) from 31 March 2015, which amends Annex II of Directive 2011/65/EU.

# 1SP0635V2A0D

# **Product Details**

| Part Number                   | Power Module | Voltage Class | Current Class | Package | IGBT<br>Supplier | $R_{g(ON)}$ | R <sub>G(OFF)</sub> | C <sub>GE</sub>  |

|-------------------------------|--------------|---------------|---------------|---------|------------------|-------------|---------------------|------------------|

| 1SP0635V2A0D-<br>FZ2400R33HE4 | FZ2400R33HE4 | 3300 V        | 2400 A        | IHV     | Infineon         | 0.52 Ω      | 3.58 Ω              | Not<br>Assembled |

| Revision | Notes                  | Date  |

|----------|------------------------|-------|

| Α        | Preliminary Datasheet. | 04/23 |

#### For the latest updates, visit our website: www.power.com

Power Integrations reserves the right to make changes to its products at any time to improve reliability or manufacturability. Power Integrations does not assume any liability arising from the use of any device or circuit described herein. POWER INTEGRATIONS MAKES NO WARRANTY HEREIN AND SPECIFICALLY DISCLAIMS ALL WARRANTIES INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF THIRD PARTY RIGHTS.

#### **Patent Information**

The products and applications illustrated herein (including transformer construction and circuits external to the products) may be covered by one or more U.S. and foreign patents, or potentially by pending U.S. and foreign patent applications assigned to Power Integrations. A complete list of Power Integrations patents may be found at www.power.com. Power Integrations grants its customers a license under certain patent rights as set forth at www.power.com/ip.htm.

#### **Life Support Policy**

POWER INTEGRATIONS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF POWER INTEGRATIONS. As used herein:

- 1. A Life support device or system is one which, (i) is intended for surgical implant into the body, or (ii) supports or sustains life, and (iii) whose failure to perform, when properly used in accordance with instructions for use, can be reasonably expected to result in significant injury or death to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Power Integrations, the Power Integrations logo, CAPZero, ChiPhy, CHY, DPA-Switch, EcoSmart, E-Shield, eSIP, eSOP, HiperLCS, HiperPLC, HiperPFS, HiperTFS, InnoSwitch, Innovation in Power Conversion, InSOP, LinkSwitch, LinkZero, LYTSwitch, SENZero, TinySwitch, TOPSwitch, PI, PI Expert, PowiGaN, SCALE, SCALE-1, SCALE-2, SCALE-3 and SCALE-iDriver, are trademarks of Power Integrations, Inc. Other trademarks are property of their respective companies. ©2022, Power Integrations, Inc.

### **Power Integrations Worldwide Sales Support Locations**

# **World Headquarters**

5245 Hellyer Avenue San Jose, CA 95138, USA Main: +1-408-414-9200 Customer Service:

Worldwide: +1-65-635-64480 Americas: +1-408-414-9621 e-mail: usasales@power.com

#### China (Shanghai)

Rm 2410, Charity Plaza, No. 88 North Caoxi Road Shanghai, PRC 200030 Phone: +86-21-6354-6323 e-mail: chinasales@power.com

#### China (Shenzhen)

17/F, Hivac Building, No. 2, Keji Nan Vasanthanagar 8th Road, Nanshan District, Shenzhen, China, 518057 Phone: +86-755-8672-8689 e-mail: chinasales@power.com

#### Germany

(AC-DC/LED/Motor Control Sales) Einsteinring 24 85609 Dornach/Aschheim Germany

Tel: +49-89-5527-39100 e-mail: eurosales@power.com

**Germany** (Gate Driver Sales)

HellwegForum 3 59469 Ense Germany

Tel: +49-2938-64-39990

e-mail: igbt-driver.sales@power.com

## **India**

#1, 14th Main Road Bangalore-560052 India Phone: +91-80-4113-8020 e-mail: indiasales@power.com

# Italy

Via Milanese 20, 3rd. Fl. 20099 Sesto San Giovanni (MI) Italy Phone: +39-024-550-8701 e-mail: eurosales@power.com

Yusen Shin-Yokohama 1-chome Bldg. Taiwan 1-7-9, Shin-Yokohama, Kohoku-ku Yokohama-shi.

Kanagawa 222-0033 Japan Phone: +81-45-471-1021 e-mail: japansales@power.com

# Korea

RM 602, 6FL Korea City Air Terminal B/D, 159-6 Samsung-Dong, Kangnam-Gu, Seoul, 135-728, Korea Phone: +82-2-2016-6610

e-mail: koreasales@power.com

# **Singapore**

51 Newton Road #19-01/05 Goldhill Plaza Singapore, 308900 Phone: +65-6358-2160

e-mail: singaporesales@power.com

5F, No. 318, Nei Hu Rd., Sec. 1 Nei Hu Dist.

Taipei 11493, Taiwan R.O.C. Phone: +886-2-2659-4570 e-mail: taiwansales@power.com

Building 5, Suite 21 The Westbrook Centre Milton Road Cambridge CB4 1YG

Phone: +44 (0) 7823-557484 e-mail: eurosales@power.com