# 800VDC AI 데이터 센터 아키텍처를 위한 1250V/1700V Gan HEMT

Kamal Varadarajan, Jimmy Liu, Chris Lee - 파워 인테그레이션스(Power Integrations)

# 소개

GaN 기반 전력 반도체 디바이스는 우수한 소재 특성으로 고효율 전력 컨버터에 이상적입니다. GaN HEMT는 빠른 스위칭 성능과 낮은 손실이라는 이 기술의 이점을 활용하여 다양한 애플리케이션을 포괄하는 많은 상업용 파워 서플라이 설계에 적용되고 있습니다.

현재 시중에 나와 있는 다양한 제조업체의 디바이스들은 보통 200V 미만 또는 600V~650V 범위의 정격 전압을 제공합니다. 650V 이상에서는 극히 일부 제조업체만이 900V 정격의 GaN HEMT를 출시했습니다. 실리콘 기판을 사용한 상용 GaN HEMT 기술은 매우 두꺼운 버퍼층이 필요하기 때문에 900V가 넘는 전압으로 확장하기가 매우 어렵고, 이로 인해 상당한 공정 문제가 발생합니다.

이 때문에 1200V 정격 이상의 와이드 밴드갭 파워 디바이스가 필요한 애플리케이션은 SiC 스위치를 사용할 수밖에 없었습니다. 그러나 GaN은 SiC보다 훨씬 높은 스위칭 주파수를 지원하며 AI 데이터 센터와 같은 애플리케이션에서 요구되는 높은 전력 밀도를 충족하는 동시에 높은 효율을 유지할 수 있는 방안을 제시합니다. 파워 인테그레이션스 (Power Integrations)의 독점 기술인 PowiGaN™ 기술을 기반으로 개발한 GaN HEMT는 매우 높은 정격 전압(최대 1700V)을 실제 디바이스에서 달성할 수 있다는 고유한 이점이 있어 1200V 이상의 SiC를 대체할 수 있는 경쟁력 있고 즉시 사용 가능한 대안이 됩니다.

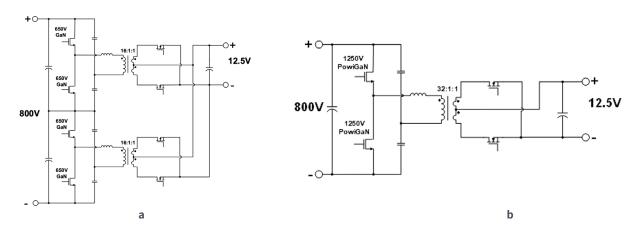

800VDC 버스 애플리케이션에서 GaN의 이점을 활용하기 위해 650V GaN 디바이스를 2개 직렬로 연결한 적층 하프 브리지 구성(650V GaN 디바이스 총 4개)이 사용되어 왔습니다. 이러한 적층 토폴로지는 GaN이 지원하는 고주파수에서 동작이 가능하지만, 제어 복잡성 증가, 입력 전압 불균형으로 인한 신뢰성 위험, 설치 공간 증가, 전도 손실 증가 등 효율 저하와 비용 증가를 초래하는 여러 문제를 야기합니다. 반면, 이 애플리케이션에서 1250V 정격 PowiGaN 스위치를 사용하면 GaN의 특성을 최대한 활용하여 이상적인 고주파 전력 스위치를 구현하는 동시에 전력 컨버터 토폴로지를 크게 단순화할 수 있습니다.

1250V PowiGaN 캐스코드 스위치를 사용하면 파워 서플라이 설계자는 업계 표준 80% 디레이팅을 허용하면서 안정적으로 1000V의 동작 피크  $V_{DS}$ 를 지정할 수 있습니다. 동작 피크  $V_{DS}$  1000V를 초과(최대 1360V)하는 애플리케이션의 경우, 1700V PowiGaN 캐스코드 스위치를 사용하면 사용자는 유사한 고효율 파워 서플라이를, 이제는 더 높은 전압에서도 설계할 수 있습니다. 본 백서에서는 정격 전압이 1200V를 초과하는 업계 최초의 GaN 파워 스위치의 신뢰성과 견고성을 설명하고, NVIDIA 800VDC AI 데이터 센터 아키텍처에서 요구하는 전력 밀도와 98% 이상의 효율 요건을 충족하는 적합성을 살펴봅니다.

# 파워 인테그레이션스(Power Integrations)의 1250V/1700V GaN HEMT 캐스코드 스위치

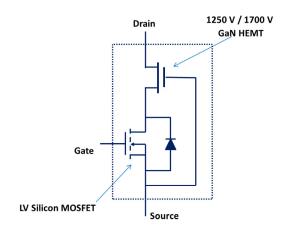

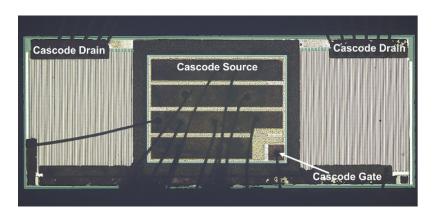

1250V/1700V GaN HEMT는 파워 인테그레이션스(Power Integrations)의 독점 PowiGaN 기술을 사용하여 제작된 상시 ON, 고갈형(depletion) 디바이스입니다. 이 디바이스는 캐스코드 구성으로 저전압 실리콘 MOSFET과 직렬로 연결되어 전력 전자 시스템의 안전한 동작에 필수적인 효과적인 상시 OFF 동작을 구현합니다. 감소 모드 GaN 디바이스는 p-type GaN 게이트 층이 필요하지 않아 안정성이 매우 높은 것으로 간주됩니다. 따라서 기준 전압(Threshold) 드리프트 및 관련 불안정성 문제를 방지하여 장기적인 안정성을 보장합니다. 고전압 GaN HEMT와 저전압 실리콘 MOSFET을 사용한 캐스코드 스위치의 회로도는 그림 1에 나와 있습니다. GaN HEMT 위에 저전압 실리콘 MOSFET이 적층된 60mOhm(최대@ 25°C) 1250V GaN 캐스코드 스위치의 현미경 사진이 그림 2에 나와 있습니다. .

그림 1. 고전압 PowiGaN 캐스코드 스위치 회로도

그림 2. 60mOhm, 1250V PowiGaN 캐스코드 스위치의 현미경 사진

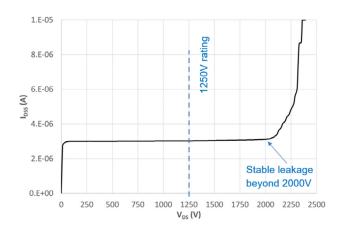

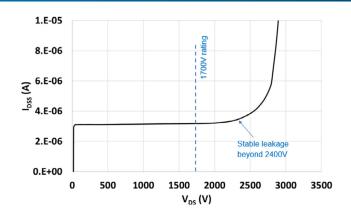

일반적인 1250V 및 1700V PowiGaN 캐스코드 스위치의 OFF 상태 특성이 그림 3과 4에 나와 있습니다. 정격 전압을 크게 넘어서는 조건에서도 안정적인 누설 동작을 보여주며 뛰어난 과도 과전압 기능을 보장합니다. 이는 유사한 정격의 실리콘 또는 SiC 디바이스에 비해 상당한 안전 마진을 제공함을 보여줍니다.

그림 3. 1250 V PowiGaN 캐스코드 스위치의 일반적인 OFF 상태 특성

그림 4. 1700V PowiGaN 캐스코드 스위치의 일반적인 OFF 상태 특성

# 필드 신뢰성 보장

우수한 전기적 특성을 갖추는 것도 중요하지만, 파워 디바이스는 현장에서 안정적인 동작을 보장하기 위해 산업 표준 신뢰성 검증 요건을 충족하거나 초과 달성해야 합니다. 본 섹션에서는 1250V GaN HEMT가 전력 변환 애플리케이션용으로 적합한지 확인하기 위해 정적 및 동적 조건에서 수행된 핵심적인 고전압 신뢰성 스트레스 평가 결과를 공유합니다.

## A. 고온 역바이어스(HTRB)

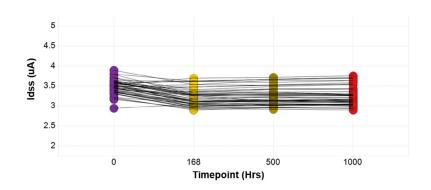

고온 역바이어스(HTRB)는 높은 드레인-소스 바이어스 하에서 파워 디바이스의 장기 안정성을 평가하는 OFF 상태 신뢰성 스트레스 테스트로, 장시간 높은 전기장 하에서 열적으로 활성화된 고장 메커니즘을 가속화하기 위한 것입니다. 1250V GaN 캐스코드 스위치의 HTRB 스트레스 테스트는 150°C의 주변 환경에서 OFF 상태  $V_{DS}$ 를 1000V(1250V 정격의 80%)로 1000시간 동안 가하여 수행되었으며, JEDEC HTRB 가이드라인 JEP198에 명시된 사양에 따라 합격 판정을 받았습니다. 그림 5에서 볼 수 있듯이 디바이스의 누설 안정성이 우수하여 고전압에서 고신뢰성 애플리케이션에 적합함을 입증했습니다.

그림 5. 1000V/150°C, 1000시간의 HTRB 스트레스 조건에서도 안정적인 OFF 상태 드레인 누설

| Voltage/Temperature | 80 °C    | 100 °C   | 120 °C   |

|---------------------|----------|----------|----------|

| 2100 V              |          | <b>✓</b> |          |

| 2150 V              | <b>✓</b> | <b>✓</b> | <b>✓</b> |

| 2200 V              |          | <b>✓</b> |          |

표 1. OFF 상태 가속 평가 조건

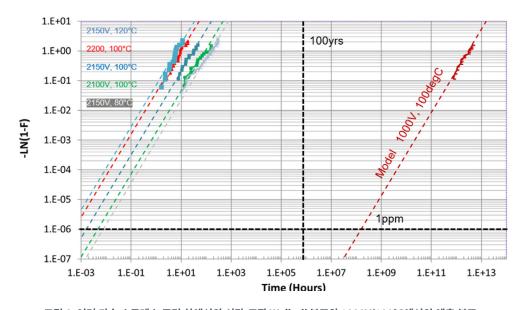

상기 HTRB 검증 테스트 외에도, 내재적인 OFF 상태 고장률을 도출하기 위해 다수의 디바이스에 대해 표 1과 같이 가속  $V_{\rm DS}$  조건( $2100V\sim2200V$ )과 다양한 온도( $80^{\circ}C\sim120^{\circ}C$ )에서 테스트를 실행하였습니다.

이러한 실험에서 얻은 고장 시간 Weibull 분포를 기반으로 전압 가속 계수는 지수 모델, 온도 가속 계수는 아레니우스모델을 통해 도출했습니다. 도출된 모델은 1000V/100°C에서 15,000년 이상 동작 시 누적 고장률이 1ppm인 것으로 예측하며, 이는 1250V GaN 캐스코드 파워 스위치에 상당한 수준의 내재적 신뢰성 마진이 있음을 나타냅니다(그림 6).

그림 6. 여러 가속 스트레스 조건 하에서의 시간-고장 Weibull 분포와  $1000V/100^{\circ}$ C에서의 예측 분포.

#### B. 고전압 고습 고온 역바이어스(HV-H3TRB)

많은 고신뢰성 응용 분야에서는 HTRB 기반 OFF 상태 신뢰성 검증 스트레스 테스트 통과만으로는 충분하지 않습니다. 제품은 미션 크리티컬한 애플리케이션에서 혹독한 외부 환경 조건에 노출되며 연속 또는 장기간 동작하는 경우가 많습니다. 이러한 애플리케이션을 고려할 때, 통제된 고습 환경을 기존 HTRB 테스트에 추가 스트레스 요인으로 사용하는 HV-H3TRB 테스트를 통과하는 것이 중요합니다. 이 스트레스 테스트는 습기 침투로 인한 추가적인 고장 모드를 포함하며, 패시베이션층, 액티브 및 종단 설계, 하부 구조를 비롯한 디바이스의 모든 측면에 대해 평가합니다.

1250V GaN 캐스코드 스위치의 HV-H3TRB 스트레스 테스트는 JEDEC 표준 JESD22-A101에 따라 85°C의 주변 온도, 85%의 상대 습도(RH)에서 수행되었으며, 1000V의 OFF 상태  $\rm V_{\rm DS}$ 로 1000시간 동안 스트레스를 가했습니다. 이 스트레스 테스트에서는 그림 5와 같이 HTRB 테스트와 동일한 OFF 상태 누설 안정성을 유지하면서 깔끔한 합격 결과를 얻었습니다.

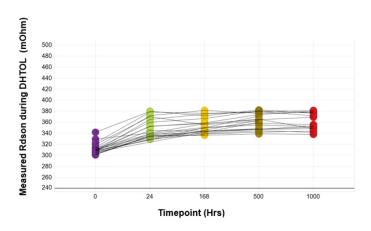

#### C. 동적 고온 동작 수명(DHTOL)

초기에 GaN HEMT의 상용화를 지연시킨 주요 문제 중 하나는 고전압 애플리케이션에서 스위칭 시 발생하는 신뢰성 문제였는데, 디바이스의 ON-저항이 턴온 직후 DC 조건에 비해 즉각적으로 증가하는 현상이 있었습니다. 동적 R<sub>DS(ON)</sub>로 알려진 이 현상은 높은 전계 강도에서 디바이스 내부에 발생하는 전하 트래핑 효과에 기인합니다. 이 문제를 해결하기 위해 epitaxial 구조 엔지니어링, 정밀한 공정 기술 최적화 등 다양한 기술이 사용되어 왔습니다.

PI의 1250V GaN 캐스코드 스위치의 스위칭 신뢰성은 JEDEC DHTOL 가이드라인 JEP180을 준수하며  $125^{\circ}$ C에서 여러 장치를 병렬로 평가할 수 있는 기능을 갖춘 사용자 지정 테스트베드에서 평가되었습니다.가이드라인에 명시된 스위칭 궤적(switching locus)에 따라 가능한 가장 엄격한 동작 조건(1000V에서 하드 스위칭 턴온 및 턴오프)을 선택했습니다. GaN 디바이스는 고전압 스위칭 시 동적  $R_{DS(ON)}$ 이 특히 중요합니다. 설계가 미흡한 GaN HEMT 디바이스는 추가적인 전자 트래핑으로 인해 고전압 스위칭 전이 동안  $R_{DS(ON)}$ 이 크게 증가할 가능성이 높으며, 컨버터 효율에 악영향을 미치거나, 더 심각한 경우 하드 장애를 초래할 수 있습니다.

그림 7. 1000시간 DHTOL 동안 안정적인 R<sub>DS(ON)</sub>, 변화율 20% 미만

$1000\text{V}/125^\circ\text{C}$ , 1000시간 DHTOL 스트레스 조건에서 모니터링된 1250V GaN 캐스코드의  $R_{\text{DS(ON)}}$ 은 초기 시점부터 안정적인 특성을 나타냈고 변화 폭은 20% 미만으로 매우 작았습니다(그림 7). 이는 유사한 하드 스위칭 조건에서 테스트된 최첨단 650V GaN HEMT와 동등한 수준의 성능입니다. GaN HEMT가 핵심 특성인 하드 스위칭 기능을 포함하여 성능 저하 없이 1200V 이상으로까지 확장될 수 있음을 보여주는 결과로, 모든 잠재적 고신뢰성 애플리케이션을 충족할 수 있는 견고성이 있음을 의미합니다.

#### NVIDIA 800VDC AI 데이터 센터 아키텍처 사용 사례

#### A. HVDC AI 데이터 센터 아키텍처 배경

AI 데이터 센터에서 고전압 DC(HVDC) 분배가 기존 54VDC 버스 아키텍처를 대체할 것이라는 점이 점점 더 명확해지고 있습니다. 주요 제안 중 하나는 Google, Meta, Microsoft가 시작한 Open Compute Project(OCP)에서 나왔으며, 800VDC 전력 시스템을 정의하고 있습니다. 이 새로운 아키텍처는 전력 공급 방식을 혁신하여 랙당 기존 100kW 미만에서 1MW로 확장하는 동시에, 전력 변환 효율과 전력 밀도를 더욱 향상시킵니다.

NVIDIA는 차세대 AI 데이터 센터를 위한 800VDC 아키텍처도 제안하고 있습니다. 800VDC 직접 입력 방식을 채택함으로써 컴퓨팅 랙은 기존의 통합 AC-DC PSU단에 의존하지 않고도 전력을 더 효율적으로 공급받을 수 있습니다. 대신, 랙은 2선 800VDC 전원 공급을 수용하고 랙 내부의 고전압 절연 DC-DC 컨버터를 사용하여 xPU 하위 시스템에 전력을 공급합니다. 이 접근 방식은 랙 수준의 AC-DC 변환 블록을 제거하여 추가 컴퓨팅 리소스를 위한 공간을 확보하고 열 관리를 개선합니다. 기존 AC-DC 아키텍처와 비교하여 800VDC 직접 입력은 랙 설계를 간소화하는 동시에 성능을 향상시킵니다.

디바이스 수준에서 1250V 및 1700V PowiGaN 기술은 이러한 혁신을 실현하는 데 중요한 역할을 할 수 있습니다. 간소화된 토폴로지, 빠른 스위칭 속도, 강력한 전압 용량이 조합된 이 기술은 고효율·고밀도 HVDC 변환이 요구되는 차세대 800VDC AI 데이터 센터 아키텍처에 이상적인 선택지입니다. 이 섹션에서는 1250V/1700V PowiGaN이 1) 적층 650V e-모드 GaN, 2) 1200V SiC MOS와 비교하여 가지는 가치 제안을 설명합니다.

#### B. 1250V PowiGaN과 650V e-모드 GaN 비교

그림 8은 800VDC 입력과 12.5V 출력 고정 비율 LLC 토폴로지에서 650V e-모드 GaN과 1250V PowiGaN을 비교한 것입니다. 빠른 스위칭이 가능한 GaN 디바이스 덕분에 두 솔루션 모두 800VDC 입력에서 500kHz 이상의 고주파 동작이 가능합니다. 650V e-모드 GaN의 경우, 800VDC 입력을 견디기 위해 적층 LLC 컨버터가 필요합니다. 1차측에서 이 아키텍처는 직렬로 적층된 2개의 하프 브리지를 사용합니다(총 4개의 650V e-모드 GaN 스위치). 2차측에서는 출력이 병렬로 연결되어 각 하프 브리지가 전체 출력 전력의 절반을 지원합니다. 그러나 이러한 적층 토폴로지는 다음과 같은 몇 가지 문제점을 야기합니다.

- 입력 전압 불균형: 정상 동작 중 입력 전압 불균형은 신중하게 관리해야 합니다. 하프 브리지 간에 불균형이 발생하면 GaN 디바이스에 걸리는 스트레스 전압이 예상 값인 약 400V를 초과할 수 있습니다. 이처럼 높은 전압 스트레스 하에서는 HEMT의 2DEG 채널 내 전류 트래핑 효과로 인해 동적 R<sub>DS(ON)</sub> 열화가 더 두드러집니다. 이러한 한계는 800VDC 입력 시스템에서 650V e-모드 GaN을 적층 구성으로 사용할 때의 신뢰성 및 효율 위험을 강조합니다.

- 복잡한 구동 설계: 적층 토폴로지는 특히 게이트 드라이버 회로에서 설계 복잡성을 증가시킵니다. 각 하프 브리지에는 전용 하이 사이드 드라이버와 절연 바이어스 서플라이가 필요하여 시스템 비용. 공간 및 설계 오버헤드가 더욱 커집니다.

- 효율 저하 및 비용 증가: 동일한  $R_{ ext{DS(ON)}}$  GaN 디바이스를 사용하더라도 적층 토폴로지는  $1250 ext{V}$  PowiGaN 단일 하프 브리지 토폴로지에 비해 전도 손실이 더 높습니다. 즉, 1250V PowiGaN 설계는 R<sub>DS(ON)</sub>이 두 배 더 높은 디바이스를 사용해도 동일한 전체 효율 및 손실 프로파일을 달성할 수 있습니다.

그림 8. (a) 650V e-모드 GaN 기반 적층 하프 브리지 LLC, (b) 1250V PowiGaN 기반 단일 하프 브리지 LLC

하프 브리지 LLC 애플리케이션에서 650V e-모드 GaN과 1250V PowiGaN의 차이점은 표 2에 요약되어 있으며, 고밀도 800VDC 전력 아키텍처에서 1250V PowiGaN을 사용하는 단일 하프 브리지 방식의 명확한 장점을 보여줍니다.

|                                       | 650V e-모드 GaN을 사용한 적층 하프<br>브리지 LLC | 1250V PowiGaN을 사용한 단일 하프<br>브리지 LLC |

|---------------------------------------|-------------------------------------|-------------------------------------|

| 입력 커패시턴스 불균형                          | 예                                   | 아니요                                 |

| 게이트 드라이버                              | 4개 드라이버(3개는 절연 드라이버)                | 2개 드라이버(1개는 절연 드라이버)                |

| 드라이버용 절연 바이어스 서플라이                    | 3개                                  | 1개                                  |

| 동일한 GaN R <sub>DS(ON)</sub> 에서의 전도 손실 | 2배 더 높은 손실                          | -                                   |

| 동일한 효율 및 손실 수준 유지에 필요한                | -                                   | 2배 높은 R <sub>DS(ON)</sub>           |

표 1. 650V e-모드 GaN과 1250V PowiGaN의 하프 브리지 LLC 비교

#### C. 1MHz LLC 동작에서 1250V PowiGaN과 1200V SiC MOSFET 비교

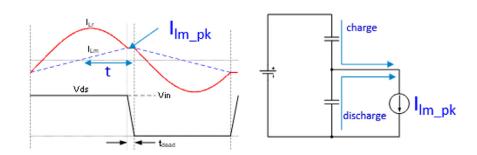

높은 전력 밀도를 달성하기 위해서는 LLC 컨버터를 높은 주파수에서 동작시키는 것이 매우 중요하며, 최대 동작 주파수는 몇 가지 주요 파라미터에 의해 결정됩니다. 그림 9는 데드타임 전환 중 LLC 등가 회로와 파형을 보여줍니다. 턴온을 위한 ZVS를 달성하기 위해서는 각 데드타임 동안 이 피크 자화 전류  $I_{lm\_pk}$ 를 사용하여 트랜지스터의 기생 출력 커패시턴스를 완전히 방전/충전해야 합니다. 그러나 자화 전류는 데드타임 동안 1차측에 추가적인 순환 손실을 유발합니다. 따라서 자화 전류 I<sub>m nk</sub>를 최소화하는 것이 LLC 컨버터의 주파수 및 효율을 개선하기 위한 목표가 됩니다.

더 높은 주파수를 달성하려면, 파워 스위치는  $C_{o(tr)}($ 시간 관련 유효 출력 커패시턴스) 값, 또는  $C_{o(tr)} \cdot V_{dc}$ 의 곱으로 얻어지는  $Q_{oss}$ (출력 전하)라고 불리는 값이 작아야 합니다. 하프 브리지 LLC의 ZVS 달성 조건을 위한 최소 데드타임  $t_{deadmin}$ 은 식 (1)에서 구할 수 있습니다.

(1)

$$t_{deadmin} = 8 \cdot C_{o(tr)} \cdot L_m \cdot f_s$$

여기서 Lm은 메인 트랜스포머의 자화 인덕턴스이고 f 는 스위칭 주파수입니다.

식 (1)에서 드레인-소스 전압을 수동으로 전환하는 데 필요한 출력 커패시턴스를 나타내는 디바이스 파라미터  $\mathsf{C}_{\mathrm{oft}}$ 은 고효율 및 고밀도 LLC 컨버터의 핵심 파라미터입니다. 주어진  $L_m$  및  $t_{dead}$ 에 대해 유효  $C_{o(tr)}$  값이 낮을수록 더 높은 스위칭 주파수 f 를 ZVS 조건과 함께 사용하여 더 높은 밀도를 만들 수 있습니다.

그림 9. 데드타임 전환 중 하프 브리지 LLC 등가 회로의 1차측 전류 및 전압 파형

스위칭 주파수에 영향을 미치는 다른 주요 디바이스 파라미터로는 총 게이트 전하량 Q 와 턴오프 지연 시간 Td(off) 가 있습니다. 간단히 말해,  $Q_{oss}$ ,  $Q_g$ ,  $T_{d(off)}$  값이 낮을수록 효율과 전력 밀도를 고려하여  $\mathring{\Delta}$ 계된 LLC 컨버터의 성능이 향상됩니다. 표 3은 1250V PowiGaN과 1200V SiC MOS의 비교를 보여줍니다. 결론적으로, 1250V PowiGaN은 비슷한  $R_{DS(ON)}$ 을 갖는 1200V SiC MOS에 비해 더 높은 주파수의 LLC를 구현할 수 있습니다.

|                               | SiC MOS | PowiGaN | PowiGaN 가치 제안           |

|-------------------------------|---------|---------|-------------------------|

| Voltage Rating (V)            | 1200    | 1250    | 더 높은 BV                 |

| $R_{DS(ON)}$ m $\Omega$ 25 °C | 60      | 60      | 동일한 R <sub>DS(ON)</sub> |

| Q <sub>oss</sub> @ 800 V; nC  | 180     | 140     | 높은 주파수                  |

| LLC iQ <sub>g</sub> ; nC      | 106     | 45      | 낮은 구동 손실                |

| T <sub>d(off)</sub> ; ns      | 48      | 15      | 낮은 턴오프 손실               |

표 3. 1200V SiC MOS와 1250V PowiGaN의 파라미터 비교

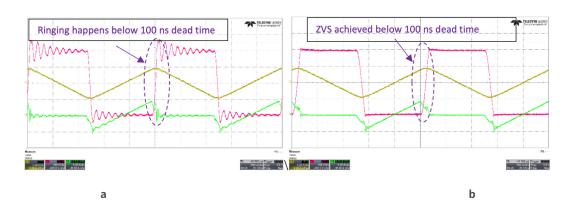

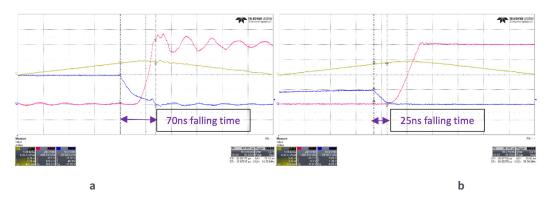

그림 10은 1250V, 60mΩ PowiGaN 디바이스의 최대 스위칭 주파수를 검증한 것으로, 800VDC 입력, 1MHz 하프 브리지 LC 공진 파형을 동급 최고 수준인 1200V, 60mΩ SiC MOS와 비교한 결과를 보여줍니다. 결과는 1250V PowiGaN 기술이 100ns 미만의 전환 데드타임으로 1MHz ZVS 동작을 달성함을 보여줍니다. 반면, 1200V SiC MOS는 하드 스위칭 정류로 1MHz에서 ZVS를 달성하지 못하며, 고온에서 현저한 링잉 현상을 보입니다. 그림 11은 동일한  $R_{G(off)}$ =2  $\Omega$ 에서 턴오프 시  $V_{GS}$ 와  $V_{DS}$ 를 확대하여 보여줍니다. SiC MOS는  $V_{GS}$  하강 시간이 상당히 길어(PowiGaN보다 약 3배 긴 하강 시간) 실제 동작 주파수가 500kHz 미만으로 제한됩니다.

그림 10. (a) 1200V 60mΩ SiC MOS 1MHz 공진 파형 (b) 1250V 60mΩ PowiGaN 1MHz 공진 파형(200ns / div)

(녹색: 로우 사이드 I<sub>ns</sub> 전류 5A / div, 빨간색: 하프 브리지 스위칭 노드 V<sub>ns</sub> 전압 200V / div, 노란색: 자화 전류 5A / div)

그림 11. 턴오프 기간  $V_{GS}$  및  $V_{DS}$  파형 확대 (a) 1200V  $60m\Omega$  SiC MOS 1MHz 공진 파형 (b) 1250V  $60m\Omega$  PowiGaN 1MHz 공진 파형(50ns / div)

(파란색: 게이트-소스  $V_{GS}$  전압 10V/div, 빨간색: 하프 브리지 스위칭 노드  $V_{DS}$  전압 200V/div, 노란색: 자화 전류 5A/div)

#### D. HVDC AI 데이터 센터를 위한 1700V PowiGaN

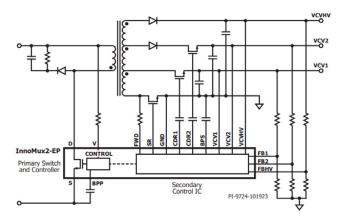

2024년, 파워 인테그레이션스(Power Integrations)는 업계 최초의 1700V PowiGaN 기반 제품인 IMX2353F(25°C 에서  $520m\Omega$ )를 출시했습니다. 이 제품은 1000VDC 공칭 입력 전압을 손쉽게 지원하는 동시에 HVDC AI 데이터 센터 애플리케이션의 보조 전력 요구 사항을 완벽하게 충족합니다. 그림 12에서 볼 수 있듯이, IMX2353F는 InnoMux<sup>™</sup>2-EP 제품군에 속하며, 1, 2차측 컨트롤러와 보호 기능, 센싱 부품, 안전성이 검증된 피드백 메커니즘(FluxLink™)을 1700V PowiGaN을 갖춘 단일 IC에 통합했습니다. 각 출력을 독립적으로 레귤레이션하고 보호함으로써 멀티 다운스트림 변환 단계를 제거합니다.

IMX2353F는 레귤레이션된 출력 전압을 하나에서 세 개까지 유연하게 제공하며, DCM SR-ZVS 모드에서만 작동하고 1차측 스위치에서 제로 전압 스위칭(ZVS)을 특징으로 합니다. 이 특징은 800VDC~1000VDC 입력 범위의 고전압 애플리케이션에 매우 유용하여 턴온 시 기생 정전용량성 방전 손실과 전체 발열을 줄여줍니다.

그림 12. IMX2353F의 일반 애플리케이션

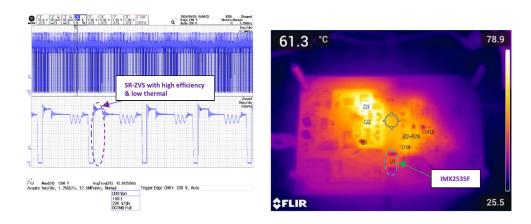

그림 13은 1000V 입력에서 IMX2353F를 사용한 60W 레퍼런스 디자인의 파형과 열을 보여줍니다. 1700V PowiGaN 과 독특한 SR-ZVS 제어 덕분에 1000V 입력과 최대 전력에서 온도 상승은 22.3°C에 불과합니다. 이는 HVDC AI 데이터 센터를 위한 소형 저온 보조 파워 서플라이를 구현하는 데 도움이 됩니다. 이 디바이스는 800VDC PSU에서 최신 트렌드에 맞게 48V 팬을 구현하면서 12V 시스템 출력을 필요로 하는 경우에 특히 이상적입니다.

그림 13. IMX2353F와 1000V 입력을 갖춘 60W 레퍼런스 디자인

# 결론

파워 인테그레이션스(Power Integrations)의 독점 PowiGaN 기술을 사용하면 1200V 이상의 정격 전압을 갖는 고신뢰성 GaN HEMT를 실현할 수 있습니다. 이 업계 최초의 1250V GaN 스위치를 통해 설계자는 NVIDIA 800VDC AI 데이터 센터 아키텍처를 위한 고밀도, 고효율 파워 서플라이를 구축할 수 있으며, 1200V SiC 또는 650V GaN을 사용하는 적층 토폴로지 기반 솔루션에 비해 성능이 크게 향상됩니다.

향후 HVDC 시스템은 현대 데이터 센터의 랙당 전력 수요가 증가함에 따라 800VDC 이상의 전압으로 나아갈 것으로 예상됩니다. 이러한 변화는 메인 파워단의 고신뢰성 1700V PowiGaN 디바이스가 낮은 ON 상태 저항으로 더 높은 효율과 전력 밀도를 제공할 수 있도록 새로운 기회를 열어줍니다. 미래는 그 어느 때보다 빠르게 다가오고 있습니다.

### 추가 자료 목록

K. Varadarajan et al. "Reliability Qualification of 1250 V Lateral GaN HEMTs for High Reliability Industrial Applications,"

IEEE International Reliability Physics Symposium proceeding, 3A2.1-3A2.6 (2025)

K. Varadarajan et al. "Reaching Beyond 1200 V: Lateral GaN HEMTs for High-Reliability EV and Industrial Applications"

PCIM Europe proceeding, 1593-1598 (2024)

K. Murukesan et al. "State of the Art 1.7kV Lateral GaN HEMTs, an Alternative to SiC", IEEE Applied Power Electronics Conference proceeding, 180-184 (2025)

# For more information,