# 1250V/1700V PowiGaN HEMT在800VDC AI数据中心架 构中的应用

作者: Kamal Varadarajan、Jimmy Liu和Chris Lee, Power Integrations

## 简介

GaN功率半导体器件因其优异的材料特性而非常适合高效率功率变换器。GaN HEMT (氮化镓高电子迁移率晶体管)已被广泛应用于众多商用电源设计中,覆盖各类应用场景。该技术凭借其低损耗、快速开关特性,在电源领域展现出显著优势。

市面上大部分制造商提供的商用器件通常具有低于200V的额定耐压,或其额定耐压介于600V至650V之间。在650V以上电压领域,仅有少数制造商推出了900V额定耐压的GaN HEMT。基于硅衬底的商用GaN HEMT技术难以实现900V以上的电压扩展,因为这需要极厚的缓冲层,从而带来显著的工艺挑战。

因此,需要额定耐压1200V及以上宽禁带功率器件的应用一直受限于使用SiC开关器件。然而,与SiC相比,GaN能够实现更高的开关频率,在保持高效率的同时,为满足AI数据中心等应用日益增长的功率密度需求提供了可行路径。Power Integrations采用其专有PowiGaN™技术制造的GaN HEMT具有独特的优势,可在实际器件中实现极高额定耐压(高达1700V),使其成为替代1200V SiC器件及更高电压器件的现成且极具吸引力的选择。

为在800VDC母线应用中充分发挥GaN的优势,通常会采用两个650V GaN器件进行串联堆叠的半桥结构,共计使用四个650V GaN器件。虽然这种堆叠拓扑结构可以在GaN所能达到的高频下工作,但它带来了若干挑战,包括控制复杂性增加、输入电压不平衡导致的可靠性风险、占用空间增大以及导通损耗增加,从而导致效率降低和成本上升。相比之下,在此应用中采用1250V额定耐压的PowiGaN开关,不仅能显著简化功率变换器拓扑结构,更能充分利用GaN的特性——正是这些使其成为理想的高频功率开关。

利用1250V的PowiGaN共源共栅开关,电源设计人员可以非常放心地明确其设计可以工作于1000V的峰值V<sub>DS</sub>,同时满足80%的行业降额标准。对于工作峰值V<sub>DS</sub>超过1000V且高达1360V的应用场景,采用1700V PowiGaN共源共栅开关可让用户设计出同样高效的电源方案,但此时却是在更高的电压下工作。本文阐述了业界首款额定耐压超过1200V的GaN功率开关的可靠性与耐用性,并证明其完全满足NVIDIA 800VDC AI数据中心架构对功率密度和超过98%效率的要求。

# Power Integrations的1250V/1700V GaN HEMT共源共栅开关

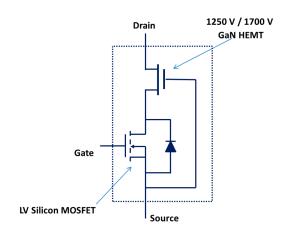

1250V/1700V GaN HEMT是一款基于Power Integrations的专有PowiGaN技术制造的常开、耗尽型器件。它与低压硅MOSFET串联,形成共源共栅结构,以实现有效的常关操作,这对于电力电子系统的安全运行至关重要。耗尽型GaN器件被认为具有极高的可靠性,因为它们无需p型GaN栅极层。因此,它们避免了阈值电压漂移及相关的不稳定性问题,确保了长期稳定性。图1所示为高压GaN HEMT和低压硅MOSFET构成的共源共栅开关的电路原理图。图2所示为一款60m $\Omega$  (25°C下最大值)、1250V GaN共源共栅开关的显微照片,其中低压硅MOSFET堆叠在GaN HEMT顶部。

图1. 高压PowiGaN共源共栅开关的电路原理图

图2. 60mΩ、1250V PowiGaN共源共栅开关的显微照片

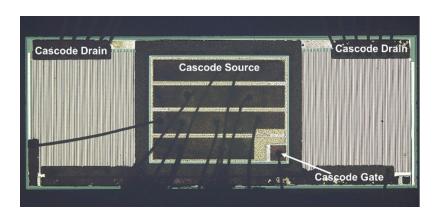

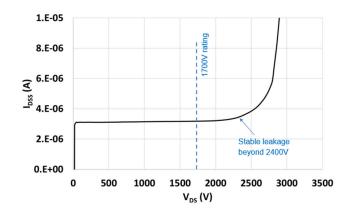

图3和图4显示了典型的1250V和1700V PowiGaN共源共栅开关的关断状态特性,其漏电特性在远超额定电压时仍保 持稳定,确保了出色的瞬态过压承受能力。这表明与同等耐压规格的硅或SiC器件相比具有显著的安全裕量。

图3.1250V PowiGaN共源共栅开关的典型关断状态特性

图4. 1700V PowiGaN共源共栅开关的典型关断状态特性

# 确保应用可靠性

虽然优良的电气特性至关重要,但功率器件还必须满足并超越行业标准的可靠性认证要求,以确保在实际应用中可 靠工作。在本节中,我们将分享1250V GaN HEMT在静态及动态条件下测得的高压可靠性应力评估结果,而这些评估 通常用来作为对应用于功率变换的高压GaN HEMT进行认证的部分测试。

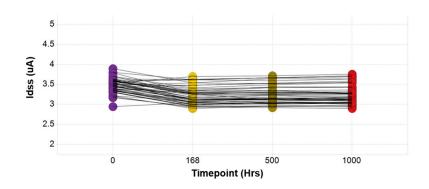

#### A. 高温反偏压(HTRB)测试

高温反向偏压(HTRB)是一种关断状态可靠性应力测试,用于评估功率器件在高漏源偏压下的长期稳定性,旨在通 过长时间高电场作用加速热激活故障机制。1250V GaN共源共栅开关的HTRB应力测试在150℃的环境中进行,并以 1000V (1250V额定值的80%) 的关断状态V<sub>DS</sub>进行1000小时的应力测试,结果符合JEDEC HTRB指南JEP198中规定的 规格要求。如图5所示,该器件展现出优异的漏电流稳定性,验证了其适用于高压环境下的高可靠性应用。

图5. 在1000V/150°C条件下经1000小时HTRB应力测试后,仍保持稳定的关断状态漏极漏电流

| Voltage/Temperature | 80 °C    | 100 °C   | 120 °C   |

|---------------------|----------|----------|----------|

| 2100 V              |          | <b>✓</b> |          |

| 2150 V              | <b>✓</b> | <b>✓</b> | <b>✓</b> |

| 2200 V              |          | <b>✓</b> |          |

表1.关断状态下的加速评估条件

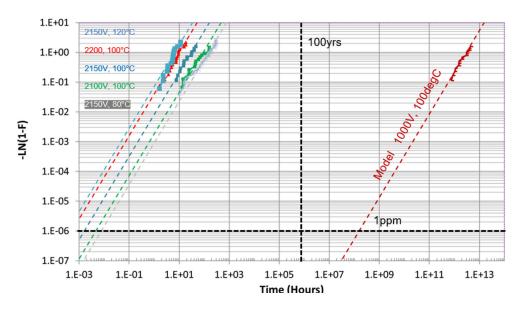

除了上述描述的HTRB认证测试外,还通过在加速 $V_{\rm DS}$ 条件(2100V至2200V)下,对大量器件在多个温度(80°C至120°C)下进行测试,提取了本征关断状态故障率,如表1所示。

根据本组实验获得的无故障时间威布尔分布,使用指数模型提取电压加速因子,通过Arrhenious模型提取温度加速因子。提取的模型预测在1000V/100°C的条件下运行15,000多年以后的累积故障率为1ppm,这表明1250V GaN共源共栅功率开关具有显著的内在可靠性裕量(图6)。

图6. 威布尔分布表示在多种加速应力条件下的无故障时间,以及在1000V/100°C下的预估分布结果

#### B. 高压高湿高温反向偏压(HV-H3TRB))

对于许多有高可靠性要求的应用而言,仅通过基于HTRB的关断状态可靠性认证应力测试是不够的。终端产品可能会经常暴露在恶劣的外部环境条件下,在极端关键应用场合需要连续或长时间运行。对于此类应用,通过HV-H3TRB测试非常重要,该测试在原有HTRB测试的基础上,使用受控高湿环境作为额外的应力因素。该应力测试包含由于湿气渗透而导致的其他故障模式,并且是对器件所有方面的测试,包括钝化层、有源和接线设计以及底层结构。

1250V GaN共源共栅开关的HV-H3TRB应力测试在85°C的环境温度下进行,相对湿度(RH)为85%,关断状态 $V_{DS}$ 为 1000V,持续1000小时,遵循JEDEC标准JESD22-A101。该应力测试获得合格的通过结果,其关断状态漏电流稳定性与HTRB期间相同,如图5所示。

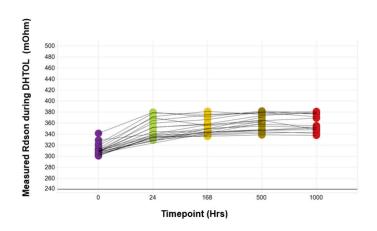

#### C. 动态高温工作寿命(DHTOL)试验

最初延缓GaN HEMT商业化应用的主要顾虑之一,在于其在高压开关应用中的可靠性问题。研究发现,相较于直流工 作状态,器件在导通后其导通电阻会立即升高。这种现象称为动态R<sub>DS(ON)</sub>,归因于高电场强度下器件内的电荷捕获效 应。为解决这一问题,已采用多种技术手段,包括外延结构工程和精心优化的工艺技术。

PI的1250V GaN共源共栅开关的可靠性在符合JEDEC DHTOL指南JEP180的定制测试平台上进行了评估,该平台具 备在125°C环境下并行测试多个器件的能力。根据指南所述的开关轨迹,选择了最严苛的工作条件——在1000V电压 下进行硬开关的开通与关断操作。对于GaN器件而言,高压开关期间的动态导通电阻Rpsinnl尤为重要。设计不当的 GaN HEMT器件在高压开关转换过程中,可能因额外的电子捕获导致R<sub>DS(ON)</sub>显著增大,这不仅会损害变换器效率,更 可能引发硬性故障。

图7. 在1000小时DHTOL期间观察到稳定的 $R_{DS(ON)}$ ,且具有极小偏移(<20%)

在1000V/125℃条件下进行1000小时DHTOL应测试期间,1250V GaN共源共栅开关的R<sub>DS(ON)</sub>表现出稳定性能(图7), 与测试起始时的数值相比仅出现小干20%的极小偏移,与在类似硬开关条件下测试的最先进的650V GaN HEMT相 当。这一结果表明, GaN HEMT的电压可扩展至1200V以上, 而不会对性能(包括关键的硬开关能力)产生任何影响, 并 证明其具备满足所有潜在高可靠性应用需求的耐用性。

#### NVIDIA 800VDC AI数据中心架构中的用例

#### A. HVDC AI数据中心架构背景

日益清楚的是,高压直流(HVDC)配电系统将取代AI数据中心中传统的54VDC母线架构。其中一项主要提案来自于谷 歌、Meta和微软发起的开放计算项目(OCP),该项目定义了一套800VDC供电系统。这种新型架构彻底改变了功率传 输方式,将传统机架功率从低于100kW提升至1MW,同时实现了更高效的功率变换和更高的功率密度。

NVIDIA还为下一代AI数据中心提出了一套800VDC架构方案。通过采用直流800VDC输入,计算机架可以更高效地接 收电力,而无需依赖传统的集成AC-DC PSU级。相反,机架采用双导线800VDC供电,并在机架内部使用高压隔离式。 DC-DC变换器为xPU子系统供电。该方案消除了机架级AC-DC变换模块,节省出来的空间可用于增加计算资源,并能 改善温升管理。相较干传统的AC-DC架构,直流800VDC输入简化了机架设计,同时提高了性能。

在器件层面,1250V和1700V的PowiGaN技术将在推动这一变革中发挥关键作用。更简洁的拓扑结构、快速的开关速 度和强大的耐压能力相结合,使其成为新兴800VDCAI数据中心架构中高效率、高功率密度HVDC变换的理想选择。 本节将阐述1250V/1700V PowiGaN相较于以下两种方案的技术优势:1) 堆叠式650V增强型GaN;2) 1200V SiC MOS。

#### B. 1250V PowiGaN与650V增强型GaN比较

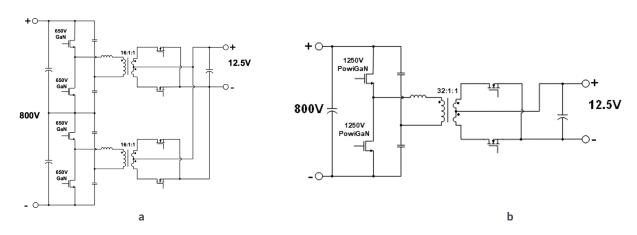

图8展示了采用650V增强型GaN器件与1250V PowiGaN器件的800VDC、12.5V输出固定比的LLC拓扑结构对比。由于 采用了快速开关的GaN器件,这两种方案都可以在800VDC输入下以超过500kHz的高频率进行工作。对于650V增强 型GaN方案,需要采用堆叠式LLC变换器以耐受800VDC输入电压。在初级侧,该架构采用两管串联的堆叠半桥(总共 四个650V增强型GaN开关)。在次级侧,输出并联连接,使得每个半桥支持总输出功率的一半。然而,这种堆叠拓扑结 构带来了若干挑战:

- 输入电压不平衡:正常工作期间的输入电压不平衡必须得到妥善控制。如果半桥之间出现不平衡,GaN器件两端 的应力电压可能会超过预期的约400V。在这种较高的电压应力下,由于HEMT的2DEG通道内的电流捕获效应,动 态R<sub>DS(ON)</sub>退化将变得更加明显。这些限制凸显了在800VDC输入系统中采用650V增强型GaN堆叠结构时存在的可 靠性与效率风险。

- 复杂的驱动设计:堆叠拓扑结构还会增加设计复杂性,特别是在栅极驱动电路中。每个半桥都需要专用上管驱 器及隔离偏置电源,这进一步增加了系统成本、占用空间和设计负担。

- ・效率较低且成本较高:采用具有相同R<sub>ps(ON)</sub>的GaN器件时,与1250V PowiGaN单管半桥拓扑结构相比,堆叠拓 扑结构会产生更高的导通损耗。这意味着1250V PowiGaN设计可采用R<sub>DS(ON)</sub>值高出2倍的器件,同时仍能实现相 同的整体效率和损耗特件。

图8. (a) 基于650V增强型GaN的堆叠半桥LLC; (b) 基于1250V PowiGaN的单管半桥LLC

表2总结了650V增强型GaN与1250V PowiGaN在半桥LLC应用中的差异,展示了采用1250V PowiGaN的单管半桥方 案在高功率密度800VDC供电架构中的显著优势。

采用650V增强型GaN的堆叠半桥LLC 采用1250V PowiGaN的单管半桥LLC

| 输入电容不平衡                                 | 是                | 否                        |  |

|-----------------------------------------|------------------|--------------------------|--|

| 栅极驱动器                                   | 4个驱动器,其中3个为隔离驱动器 | 2个驱动器,其中1个为隔离驱动器         |  |

| 驱动器的隔离偏置电源                              | 3个               | 1个                       |  |

| GaN R <sub>DS(ON)</sub> Rdson相同时的导通损耗   | 损耗高出2倍           | -                        |  |

| 具有相同效率和损耗时所需的GaN<br>R <sub>DS(ON)</sub> | _                | R <sub>DS(ON)</sub> 高出2倍 |  |

表2.650V增强型GaN与1250V PowiGaN在半桥LLC应用中的比较

#### C. 1250V PowiGaN与1200V SiC MOSFET在1MHz LLC工作模式下的比较

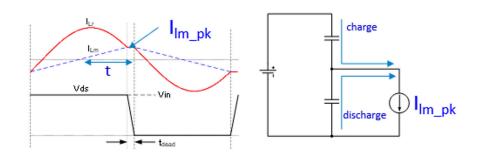

为了实现高功率密度,使LLC变换器工作于高频率至关重要,其最大工作频率由几个关键参数决定。图9所示为死区 时间切换期间的LLC等效电路及其波形。为实现开通时的零电压开关(ZVS),应利用每次死区时间内的峰值励磁电流 I<sub>m nk</sub>,使晶体管的寄生输出电容完全放电/充电。然而,在死区时间内,励磁电流将在初级侧产生额外的环流损耗。因 此,尽量降低励磁电流Imak是提高LLC变换器频率和效率的目标。

为了实现更高的频率,功率开关应该具有较小的Colti (与时间相关的有效输出电容)值,或称为Qoss (输出电荷),其值 是 $C_{o(tr)} \cdot V_{dc}$ 的乘积。半桥LLC的ZVS实现条件的最小死区时间 $t_{deadmin}$ 可由公式(1)得出。

(1)

$$t_{deadmin} = 8 \cdot C_{o(tr)} \cdot L_m \cdot f_s$$

其中,Lm是主变压器的励磁电感,fe是开关频率。

由公式(1)可知, $C_{o(tr)}$ (用来表述将漏极电压被动转换至源极电压所需的输出电容)是实现高效率、高功率密度LLC变 换器的关键参数。对于给定的 $L_m$ 和 $t_{dead}$ ,有效 $C_{o(tr)}$ 值越低,就可以在ZVS条件下使用更高的开关频率 $f_s$ ,从而实现更高 的功率密度。

图9. 死区时间切换期间半桥LLC等效电路的初级电流和电压波形

影响开关频率的其他关键器件参数是总栅极电荷 $Q_a$ 和关断延迟时间 $T_{dioffl}$ 。简而言之, $Q_{oss}$ 、 $Q_a$ 和 $T_{dioffl}$ 的值越低,为提 高效率和功率密度而设计的LLC变换器的性能就越好。表3显示了1250V PowiGaN与1200V SiC MOS之间的比较。结 论很明确,与具有近似R<sub>DS(ON)</sub>的1200V SiC MOS相比,1250V PowiGaN可以实现更高频率的LLC。

|  | SiC MOS | PowiGaN | PowiGaN 技术优势 |

|--|---------|---------|--------------|

|--|---------|---------|--------------|

| 电压额定值(V)                      | 1200 | 1250 | 额定耐压值更高                |

|-------------------------------|------|------|------------------------|

| $R_{DS(ON)}$ m $\Omega$ 25 °C | 60   | 60   | R <sub>DS(ON)</sub> 相同 |

| Q <sub>oss</sub> @ 800 V; nC  | 180  | 140  | 高工作频率                  |

| LLC iQ <sub>g</sub> ; nC      | 106  | 45   | 低驱动损耗                  |

| T <sub>d(off)</sub> ; ns      | 48   | 15   | 低关断损耗                  |

表3.1200V SiC MOS与1250V PowiGaN参数比较

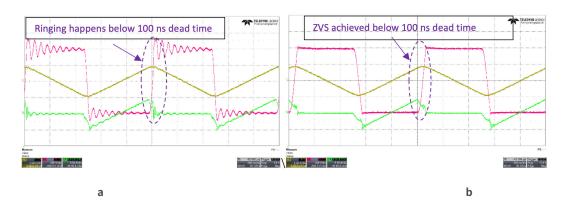

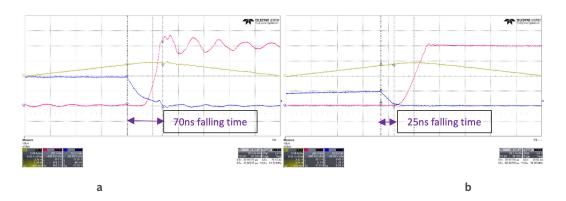

为了验证1250V、60mΩ PowiGaN器件的最大开关频率,图10显示了800VDC输入、1MHz半桥LLC谐振波形,并与一 流的1200V、60mΩ SiC MOS进行了比较。结果表明,1250V PowiGaN技术实现了1MHz ZVS操作,且切换死区时间小 于100ns。相比之下,1200V SiC MOS在硬开关换向时无法在1MHz频率下实现ZVS,在温度升高时会出现明显的振 铃。图11提供了在相同 $R_{Gloff}$ = $2\Omega$ 下关断时 $V_{GS}$ 和 $V_{DS}$ 波形的局部放大图:SiC MOS显示出明显更长的 $V_{GS}$ 下降时间(比 PowiGaN的下降时间长约3倍),从而有效地将其实际工作频率限制在500kHz以下。

图10. (a) 1200V 60mΩ SiC MOS 1MHz谐振波形;(b) 1250V 60mΩ PowiGaN 1MHz谐振波形(200ns / 格)

(绿色:下管I<sub>D</sub>s电流5A/格;红色:半桥开关节点V<sub>DS</sub>电压200V/格;黄色:励磁电流5A/格)

图11. 关断期间的 $V_{GS}$ 和 $V_{DS}$ 波形局部放大图 (a) 1200V 60m $\Omega$  SiC MOS 1MHz谐振波形;(b) 1250V 60m $\Omega$  PowiGaN 1MHz谐振波形 (50ns / 格)

(蓝色:栅源极 $V_{cs}$ 电压10V/格;红色:半桥开关节点 $V_{ns}$ 电压200V/格;黄色:励磁电流5A/格)

#### D. 适用于HVDC AI数据中心的1700V PowiGaN

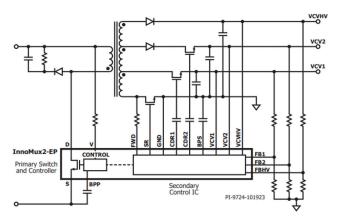

2024年, Power Integrations发布了业界首款基于1700V PowiGaN开关的产品IMX2353F (25°C时为520mΩ),可轻 松支持1000VDC额定输入电压,同时完美匹配HVDC AI数据中心应用的辅助电源要求。如图12所示,IMX2353F属于 InnoMux™2-EP产品系列,该产品系列将具有保护功能的初级和次级控制器、检测元件以及符合安全标准的反馈机制 (FluxLink™)集成到了采用1700V PowiGaN开关的单个IC中。该器件可对每路输出提供独立调整和保护,从而消除多 个后级变换级。

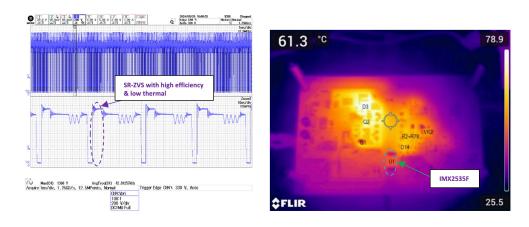

IMX2353F可灵活地提供一至三个电压稳定的稳压输出,并仅在初级开关具有零电压开关(ZVS)特性的DCM SR-ZVS 模式下工作。这一特性对于800VDC至1000VDC输入范围内的高压应用非常有益,可降低开通期间的寄生电容放电损 耗以及整体温升。

图12. IMX2353F的典型应用

图13所示为使用IMX2353F、输入电压为1000V的60W参考设计的波形和温升表现。由于采用了1700V PowiGaN和独 特的SR-ZVS控制,在1000V输入和满功率下温升仅为22.3℃。它有助于为HVDC AI数据中心实现小尺寸的低温升辅助 电源设计;该器件特别适合于在800VDC电源中给流行的48V风扇供电,同时还可提供12V的系统供电输出。

图13. 采用IMX2353F和1000V输入的60W参考设计

## 结论

凭借Power Integrations专有的PowiGaN技术,可以实现额定耐压超过1200V的高可靠性GaN HEMT。这些业界首 创的1250V GaN开关可以帮助设计人员为NVIDIA 800 VDC AI数据中心架构构建高功率密度、高效率的电源,与使用 1200V SiC的解决方案或使用650V GaN的堆叠拓扑结构相比,性能有显著提升。

展望未来,在现代数据中心每个机架电力需求不断增长的推动下,HVDC系统的电压趋势将超过800VDC。这一转变 为主功率级中的高可靠性1700V PowiGaN器件带来了新的机遇,其较低的导通电阻可实现更高的效率和功率密度。 未来正以前所未有的速度到来。

#### 延伸阅读清单:

K. Varadarajan et al. "Reliability Qualification of 1250 V Lateral GaN HEMTs for High Reliability Industrial Applications,"

IEEE International Reliability Physics Symposium proceeding, 3A2.1-3A2.6 (2025)

K. Varadarajan et al. "Reaching Beyond 1200 V: Lateral GaN HEMTs for High-Reliability EV and Industrial Applications"

PCIM Europe proceeding, 1593-1598 (2024)

K. Murukesan et al. "State of the Art 1.7kV Lateral GaN HEMTs, an Alternative to SiC", IEEE Applied Power Electronics Conference proceeding, 180-184 (2025)

# For more information,